Thermal Characterization of Conductive Filaments in Unipolar Resistive Memories

Abstract

:1. Introduction

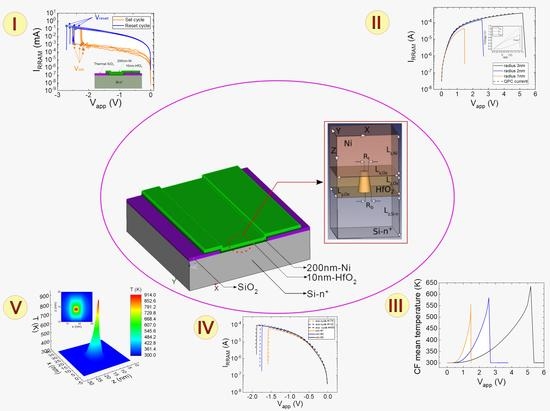

2. Device Fabrication and Measurement Setup

3. Device Simulation and Conductive Filament Temperature Determination

3.1. Simulator Description

3.2. Experimental Conductive Filament Temperature Extraction

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lanza, M.; Sebastian, A.; Lu, W.; Le Gallo, M.; Chang, M.-F.; Akinwande, D.; Puglisi, F.; Alshareef, H.; Liu, M.; Roldan, J. Memristive technologies for data storage, computation, encryption and radio-frequency communication. Science 2022, 376, 6597. [Google Scholar] [CrossRef] [PubMed]

- Spiga, S.; Sebastian, A.; Querlioz, D.; Rajendran, B. Memristive Devices for Brain-Inspired Computing; Elsevier: Amsterdam, The Netherlands, 2020. [Google Scholar]

- Chou, C.-C.; Lin, Z.-J.; Tseng, P.-L.; Li, C.-F.; Chang, C.-Y.; Chen, W.-C.; Chih, Y.D.; Chang, T.-Y.J. An N40 256K×44 embedded RRAM macro with SL-precharge SA and Low-Voltage Current Limiter to Improve Read and Write Performance. In Proceedings of the 2018 IEEE International Solid–State Circuits Conference, San Francisco, CA, USA, 11–15 February 2018. [Google Scholar]

- Yang, C.-F.; Wu, C.-Y.; Yang, M.-H.; Wang, W.; Yang, M.-T.; Chien, T.-C.; Fan, V.; Ts, S.-C. Industrially applicable read disturb model and performance on Mega-bit 28nm embedded RRAM. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020. [Google Scholar]

- Wang, Q.; Zhang, D.; Zhao, Y.; Liu, C.; Xu, X.; Yang, J.; Lv, H. A 22nm 96K×144 RRAM macro with a self-tracking reference and a low ripple charge pump to achieve a configurable read window and a wide operating voltage range. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020. [Google Scholar]

- Yu, S.; Jiang, H.; Huang, S.; Peng, X.; Lu, A. A 3.6 Mb 10.1 Mb/mm2 embedded non-volatile Re-RAM macro in 22nm FinFET technology with adaptive forming/set/reset schemes yielding down to 0.5 V with sensing time of 5ns at 0.7 V. In Proceedings of the IEEE International Solid–State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019. [Google Scholar]

- Sebastian, A.; Le Gallo, M.; Khaddam-Aljameh, R. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 2020, 15, 529–544. [Google Scholar] [CrossRef] [PubMed]

- Yu, S.; Jiang, H.; Huang, S.; Peng, X.; Lu, A. Computing-in-memory chips for deep learning: Recent trends and prospects. IEEE Circuits Syst. Mag. 2021, 21, 31–56. [Google Scholar] [CrossRef]

- Pérez-Bosch, E.; Romero-Zaliz, R.; Pérez, E.; Kalishettyhalli, M.; Reuben, J.; Schubert, M.; Jiménez-Molinos, F.; Roldán, J.; Wenger, C. Toward reliable compact modeling of multilevel 1T-1R RRAM devices for neuromorphic systems. Electronics 2021, 10, 645. [Google Scholar] [CrossRef]

- Zidan, M.; Strachan, J.; Lu, W.D. The future of electronics based on memristive systems. Nat. Electron. 2018, 1, 22–29. [Google Scholar] [CrossRef]

- Prezioso, M.; Merrikh-Bayat, F.; Hoskins, B.; Adam, G.; Likharev, K.; Strukov, D. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 2015, 521, 61–64. [Google Scholar] [CrossRef] [Green Version]

- Zhu, K.; Mahmoodi, M.; Fahimi, Z.; Xiao, Y.; Wang, T.; Bukvišová, K.; Kolíbal, M.; Roldan, J.; Perez, D.; Aguirre, F.; et al. Memristors with initial low resistive state for efficient neuromorphic systems. Adv. Intell. Syst. 2022, 4, 2200001. [Google Scholar] [CrossRef]

- Nandakumar, S.; Rajendran, B. Bio-mimetic synaptic plasticity and learning in a sub-500 mV Cu/SiO2/W. Microelectron. Eng. 2020, 226, 111290. [Google Scholar] [CrossRef] [Green Version]

- Romero-Zaliz, R.; Perez, E.; Jiménez-Molinos, F.; Wenger, C.; Roldán, J. Study of quantized hardware deep neural networks based on resistive switching devices, conventional versus convolutional approaches. Electronics 2021, 10, 346. [Google Scholar] [CrossRef]

- Merolla, P.; Arthur, J.; Alvarez-Icaza, R.; Cassidy, A.; Sawada, J.; Akopyan, F.; Jackson, B.; Imam, N.; Guo, C.; Nakamura, Y.B. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 2014, 345, 668–673. [Google Scholar] [CrossRef]

- Roldan, J.B.; Maldonado, D.; Aguilera-Pedregosa, C.; Moreno, E.; Aguirre, F.; Romero-Zaliz, R.; García-Vico, A.; Shen, Y.; Lanza, M.; Yuan, Y.; et al. Spiking neural networks based on two-dimensional materials. 2D Mater. Appl. 2022, 26, 63. [Google Scholar] [CrossRef]

- Yang, B.; Arumí, D.; Manich, S.; Gómez-Pau, A.; Rodríguez-Montañés, R.; Gonzalez, M.; Campabadal, F.; Fang, L. RRAM Random Number Generator Based on Train of Pulses. Electronics 2021, 10, 1831. [Google Scholar] [CrossRef]

- Wei, Z.; Katoh, Y.; Ogasahara, S.; Yoshimoto, Y.; Kawai, K.; Ikeda, Y.; Eriguchi, K.; Ohmori, K.; Yoneda, S. True random number generator using current difference based on a fractional stochastic model in 40-nm embedded ReRAM. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar] [CrossRef]

- Lanza, M.; Wen, C.; Li, X.; Zanotti, T.; Puglisi, F.M.; Shi, Y.; Saiz, F.; Antidormi, A.; Roche, S.; Zheng, W.; et al. Advanced data encryption using two-dimensional materials. Adv. Mater. 2021, 33, 2100185. [Google Scholar]

- Carboni, R.; Ielmini, D. Stochastic Memory Devices for Security and Computing. Adv. Electron. Mater. 2019, 5, 1900198. [Google Scholar] [CrossRef] [Green Version]

- Chua, L.O.; Sung, M.K. Memristive devices and systems. Proc. IEEE 1976, 64, 209–223. [Google Scholar] [CrossRef]

- von Witzleben, M.; Fleck, K.; Funck, C.; Baumkötter, B.; Zuric, M.; Idt, A.; Breuer, T.; Waser, R.; Böttger, U.; Menzel, S. Investigation of the Impact of High Temperatures on the Switching Kinetics of Redox-Based Resistive Switching Cells using a High-Speed Nanoheater. Adv. Electron. Mater. 2017, 3, 1700294. [Google Scholar] [CrossRef]

- Funck, C.; Menzel, S. Comprehensive model of electron conduction in oxide-based memristive devices. ACS Appl. Electron. Mater. 2021, 3, 3674–3692. [Google Scholar] [CrossRef]

- Lanza, M.; Waser, R.; Ielmini, D.; Yang, J.; Goux, L.; Suñe, J.; Kenyon, A.; Mehonic, A.; Spiga, S.; Rana, V.; et al. Standards for the Characterization of Endurance in Resistive Switching Devices. ACS Nano 2021, in press. [Google Scholar] [CrossRef]

- Chang, C.-C.; Chen, P.-C.; Chou, T.; Wang, I.-T.; Hudec, B.; Chang, C.-C.; Tsai, C.-M.; Chang, T.-S.; Hou, T.-H. Mitigating Asymmetric Nonlinear Weight Update Effects in Hardware Neural Network Based on Analog Resistive Synapse. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 116–124. [Google Scholar] [CrossRef] [Green Version]

- Hirtzlin, T.; Bocquet, M.; Penkovsky, B.; Klein, J.-O.; Nowak, E.; Vianello, E.; Portal, J.-M.; Querlioz, D. Digital Biologically Plausible Implementation of Binarized Neural Networks with Differential Hafnium Oxide Resistive Memory Arrays. Front. Neurosci. 2020, 13, 1383. [Google Scholar] [CrossRef] [Green Version]

- Camuñas-Mesa, A.; Vianello, E.; Reita, C.; Serrano-Gotarredona, T.; Linares-Barranco, B. A CMOL-Like Memristor-CMOS Neuromorphic Chip-Core Demonstrating Stochastic Binary STDP. IEEE J. Emerg. Sel. Top. Circuits Syst. 2022, 12, 898–912. [Google Scholar] [CrossRef]

- Aldana, S.; García-Fernández, P.; Romero-Zaliz, R.; González, M.; Jiménez-Molinos, F.; Gómez-Campos, F.; Campabadal, F.; Roldán, J. Resistive Switching in HfO2 based valence change memories, a comprehensive 3D kinetic Monte Carlo approach. J. Phys. D Appl. Phys. 2020, 53, 225106. [Google Scholar] [CrossRef]

- Gonzalez, M.; Rafí, J.; Beldarrain, O.; Zabala, M.; Campabadal, F. Analysis of the switching variability in Ni/HfO2-based RRAM devices. IEEE Trans. Dev. Mat. Reliab. 2014, 14, 769–771. [Google Scholar]

- Ielmini, D.; Waser, R. Resistive Switching: From Fundamentals of Nanoionic Redox Processes to Memristive Device Applications; Wiley-VCH: Hoboken, NJ, USA, 2015. [Google Scholar]

- Aldana, S.; García-Fernández, P.; Rodríguez-Fernández, A.; Romero-Zaliz, R.; González, M.; Jiménez-Molinos, F.; Campabadal, F.; Gómez-Campos, F.; Roldán, J. A 3D Kinetic Monte Carlo simulation study of Resistive Switching processes in Ni/HfO2/Si-n+-based RRAMs. J. Phys. D Appl. Phys. 2017, 50, 335103. [Google Scholar] [CrossRef]

- Spring, J.; Sediva, E.; Hood, Z.; Gonzalez-Rosillo, J.; O’Leary, W.; Kim, K.; Carrillo, A.; Rup, J.L.M. Toward Controlling Filament Size and Location for Resistive Switches via Nanoparticle Exsolution at Oxide Interfaces. Nano-Micro Small 2020, 16, 2003224. [Google Scholar] [CrossRef] [PubMed]

- Simanjuntak, F.; Chandrasekaran, S.; Lin, C.; Tseng, T.-Y. Switching Failure Mechanism in Zinc Peroxide-Based Programmable Metallization Cell. Nanoscale Res. Lett. 2018, 13, 327. [Google Scholar] [CrossRef]

- Deshmukh, S.; Muñoz-Rojo, M.; Yalon, E.; Vaziri, S.; Koroglu, C.; Islam, R.; Iglesias, R.; Saraswat, K.; Pop, E. Direct measurement of nanoscale filamentary hot spots in resistive memory devices. Sci. Adv. 2022, 8, eabk1514. [Google Scholar] [CrossRef]

- Roldán, J.B.; González-Cordero, G.; Picos, R.; Miranda, E.; Palumbo, F.; Jiménez-Molinos, F.; Moreno, E.; Maldonado, D.; Baldomá, S.; Al Chawa, M.M.; et al. On the Thermal Models for Resistive Random Access Memory Circuit Simulation. Nanomaterials 2021, 11, 1261. [Google Scholar] [CrossRef]

- Russo, U.; Ielmini, D.; Cagli, C.; Lacaita, A.L. Self-Accelerated Thermal Dissolution Model for Reset Programming in Unipolar Resistive-Switching Memory (RRAM) Devices. IEEE Trans. Electron Devices 2009, 56, 193–200. [Google Scholar] [CrossRef]

- Maldonado, D.; Aldana, S.; González, M.; Jiménez-Molinos, F.; Campabadal, F.; Roldán, J. Parameter extraction techniques for the analysis and modeling of resistive memories. Microelectron. Eng. 2022, 265, 111876. [Google Scholar] [CrossRef]

- Mazumder, S. Numerical Methods for Partial Differential Equations: Finite Difference and Finite Volume Methods; Academic Press: Cambridge, MA, USA, 2015. [Google Scholar]

- Moreno, E.; Hemmat, Z.; Roldan, J.; Pantoja, M.; Bretones, A.; Garcia, S.; Faez, R. Implementation of Open Boundary Problems in Photo-Conductive Antennas by Using Convolutional Perfectly Matched Layers. IEEE Trans. Antennas Propag. 2016, 64, 4919–4922. [Google Scholar] [CrossRef] [Green Version]

- Pan, F.; Gao, S.; Chen, C.; Song, C.; Zeng, F. Recent progress in resistive random access memories: Materials, switching mechanisms and performance. Mater. Sci. Eng. 2014, 83, 1–59. [Google Scholar] [CrossRef]

- Huang, P.; Liu, X.Y.; Chen, B.; Li, H.T.; Wang, Y.J.; Deng, Y.X.; Kang, J.F. A Physics-Based Compact Model of Metal-Oxide-Based RRAM DC and AC Operations. IEEE Trans. Electron Devices 2013, 60, 4090–4097. [Google Scholar] [CrossRef]

- Ielmini, D.; Nardi, F.; Balatti, S. Evidence for Voltage-Driven Set/Reset Processes in Bipolar Switching RRAM. IEEE Trans. Electron Devices 2012, 59, 2049–2056. [Google Scholar] [CrossRef]

- Scott, E.; Gaskins, J.; King, S.; Hopkins, P. Thermal conductivity and thermal boundary resistance of atomic layer deposited high- k dielectric aluminum oxide, hafnium oxide, and titanium oxide thin films on silicon. APL Mater. 2018, 6, 058302. [Google Scholar] [CrossRef] [Green Version]

- Panzer, M.; Shandalov, M.; Rowlette, J.; Oshima, Y.; Chen, Y.; McIntyre, P.; Goodson, K. Thermal Properties of Ultrathin Hafnium Oxide Gate Dielectric Films. IEEE Electron Device Lett. 2009, 30, 1269–1271. [Google Scholar] [CrossRef]

- Finlayson, B. The Method of Weighted Residuals and Variational Principles: With Application in Fluid Mechanics, Heat and Mass Transfer; Academic Press: Cambridge, MA, USA, 1972. [Google Scholar]

- Ielmini, D. Modeling the universal set/reset characteristics of bipolar RRAM by field- and temperature-driven filament growth. IEEE Trans. Electron Devices 2011, 58, 4309–4317. [Google Scholar] [CrossRef]

- Miranda, E.; Walczyk, C.; Wenger, C.; Schroeder, T. Model for the resistive switching effect in HfO2 MIM structures based on the transmission properties of narrow constrictions. IEEE Electron. Device Lett. 2010, 31, 609. [Google Scholar] [CrossRef]

- Roldán, J.; Miranda, E.; González-Cordero, G.; García-Fernández, P.; Romero-Zaliz, R.; González-Rodelas, P.; Aguilera, A.; González, M.; Jiménez-Molinos, F. Multivariate analysis and extraction of parameters in resistive RAMs using the Quantum Point Contact model. J. Appl. Phys. 2018, 123, 014501. [Google Scholar] [CrossRef]

- Milano, G.; Aono, M.; Boarino, L.; Celano, U.; Hasegawa, T.; Kozicki, M.; Majumdar, S.; Menghini, M.; Miranda, E.; Ricciardi, C.; et al. Quantum Conductance in Memristive Devices: Fundamentals, Developments, and Applications. Adv. Mater 2022, 34, 2201248. [Google Scholar] [CrossRef]

- Chang, S.; Lee, J.; Chae, S.; Lee, S.; Liu, C.; Kahng, B.; Kim, D.; Noh, T. Occurrence of both unipolar memory and threshold resistance switching in a NiO film. Phys. Rev. Lett. 2009, 102, 026801. [Google Scholar] [CrossRef] [PubMed]

- Brivio, S.; Spiga, S. Stochastic circuit breaker network model for bipolar resistance switching memories. J. Comput. Electron. 2017, 16, 1154–1166. [Google Scholar] [CrossRef] [Green Version]

- Zhuang, P.; Ma, W.; Liu, J.; Cai, W.; Lin, W. Progressive RESET induced by Joule heating in hBN RRAMs. Appl. Phys. Lett. 2021, 118, 143101. [Google Scholar] [CrossRef]

- Russo, U.; Ielmini, D.; Cagli, C.; Lacaita, A.L. Filament conduction and reset mechanism in NiO-based resistive switching memory (RRAM) Devices. IEEE Trans. Electron Devices 2009, 56, 186–192. [Google Scholar] [CrossRef]

| αT | 0.5 × 10−3 K−1 | CF thermal parameter |

| kth(Si) | 148 W K−1 m−1 | Si thermal conductivity |

| kth(CF) | 11 W K−1 m−1 | CF thermal conductivity |

| kth(Ni) | 90 W K−1 m−1 | Ni thermal conductivity |

| kth(HfO2) | 1 W K−1 m−1 | HfO2 thermal conductivity |

| σσCF0 | 3 × 105 Ω−1 m−1 | CF electrical conductivity |

| T0 | 300 K | Room temperature |

| Ea | 0.84 eV | Activation energy |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aguilera-Pedregosa, C.; Maldonado, D.; González, M.B.; Moreno, E.; Jiménez-Molinos, F.; Campabadal, F.; Roldán, J.B. Thermal Characterization of Conductive Filaments in Unipolar Resistive Memories. Micromachines 2023, 14, 630. https://doi.org/10.3390/mi14030630

Aguilera-Pedregosa C, Maldonado D, González MB, Moreno E, Jiménez-Molinos F, Campabadal F, Roldán JB. Thermal Characterization of Conductive Filaments in Unipolar Resistive Memories. Micromachines. 2023; 14(3):630. https://doi.org/10.3390/mi14030630

Chicago/Turabian StyleAguilera-Pedregosa, Cristina, David Maldonado, Mireia B. González, Enrique Moreno, Francisco Jiménez-Molinos, Francesca Campabadal, and Juan B. Roldán. 2023. "Thermal Characterization of Conductive Filaments in Unipolar Resistive Memories" Micromachines 14, no. 3: 630. https://doi.org/10.3390/mi14030630