A Compact MEMS Microphone Digital Readout System Using LDO and PPA-Less VCO-Based Delta-Sigma Modulation Technique

Abstract

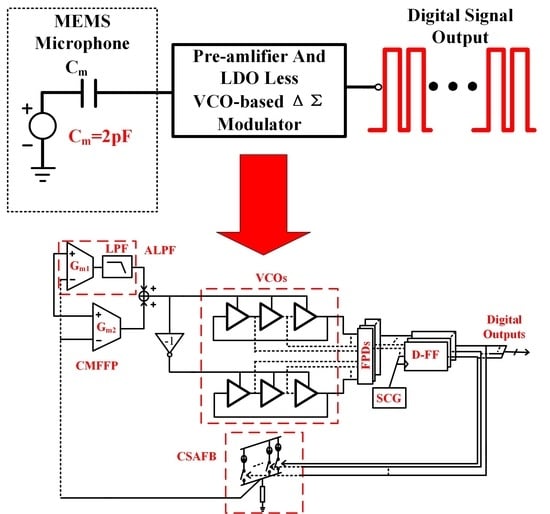

:1. Introduction

2. System Design Considerations

2.1. Analysis of Conventional System Drawbacks

2.2. Proposed System Implementation

2.3. Proposed System Mathematical Model

2.4. Noise and THD

2.5. PSR and Gain Tuning

3. Block Circuit Implementation

3.1. ALPF and CMFFP Implementation

3.2. VCO and SCG Implementation

3.3. CSAFB and CSARB Implementation

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Gemelli, A.; Tambussi, M.; Fusetto, S.; Aprile, A.; Moisello, E.; Bonizzoni, E.; Malcovati, P. Recent Trends in Structures and Interfaces of MEMS Transducers for Audio Applications: A Review. Micromachines 2023, 14, 847. [Google Scholar] [CrossRef] [PubMed]

- Fattaruso, J.; Hochschild, J.; Sjursen, W.; Fang, L.; Gata, D.; Branch, C.; Holmes, J.; Jiang, Z.; Chen, S.; Ling, K.; et al. Analog processing circuits for a 1.1 V 270 /spl mu/A mixed-signal hearing aid chip. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (Cat. No.02CH37315), San Francisco, CA, USA, 7 February 2002; Volume 1, pp. 384–475. [Google Scholar] [CrossRef]

- Wu, J.; Fedder, G.; Carley, L. A low-noise low-offset capacitive sensing amplifier for a 50-/spl mu/g//spl radic/Hz monolithic CMOS MEMS accelerometer. IEEE J. Solid-State Circuits 2004, 39, 722–730. [Google Scholar] [CrossRef]

- Nebhen, J.; Savary, E.; Rahajandraibe, W.; Dufaza, C.; Meillère, S.; Haddad, F.; Kussener, E.; Barthélémy, H.; Czarny, J.; Walther, A. Low-noise CMOS analog-to-digital interface for MEMS resistive microphone. In Proceedings of the 2013 IEEE 20th International Conference on Electronics, Circuits, and Systems (ICECS), Abu Dhabi, United Arab Emirates, 8–11 December 2013; pp. 445–448. [Google Scholar] [CrossRef]

- van den Boom, J. A 50 μW biasing feedback loop with 6ms settling time for a MEMS microphone with digital output. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 200–202. [Google Scholar] [CrossRef]

- Arbet, D.; Nagy, G.; Kováč, M.; Stopjaková, V.; Nagy, L. Readout interface for capacitive MEMS microphone in CMOS technology. In Proceedings of the 2015 22nd International Conference Mixed Design of Integrated Circuits & Systems (MIXDES), Torun, Poland, 25–27 June 2015; pp. 370–374. [Google Scholar] [CrossRef]

- Chung, C.T.J.; Lu, C.C.; Rih, W.S.; Lee, C.F.; Shih, C.M.; Yeh, Y.L. An Ultra-low Power Voice Interface Design for MEMS Microphones Sensor. In Proceedings of the 2021 IEEE Sensors, Sydney, Australia, 31 October–3 November 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Barbieri, A.; Nicollini, G. A 470 µA direct readout circuit for electret and MEMS digital microphones. Analog. Integr. Circuits Signal Process. 2014, 81, 229–240. [Google Scholar] [CrossRef]

- Picolli, L.; Grassi, M.; Fornasari, A.; Malcovati, P. A 1.0-mW, 71-dB SNDR, fourth-order ΔΣ interface circuit for MEMS microphones. Analog. Integr. Circuits Signal Process. 2011, 66, 223–233. [Google Scholar] [CrossRef]

- Jawed, S.A.; Cattin, D.; Massari, N.; Gottardi, M.; Baschirotto, A. A 1.8 V 828 µW 80 dB digital MEMS microphone. Analog. Integr. Circuits Signal Process. 2011, 67, 395–405. [Google Scholar] [CrossRef]

- Im, S.; Park, S.G. Analysis and Design of a Microphone Preamplifier for Mobile Applications. Electronics 2021, 10, 1624. [Google Scholar] [CrossRef]

- Yang, H.; Cho, J.S.; Yang, Y.; Kim, S. A load variation tolerant readout interface for high linear MEMS capacitive microphones. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Yoo, Y.; Choi, B.D. Readout Circuits for Capacitive Sensors. Micromachines 2021, 12, 960. [Google Scholar] [CrossRef] [PubMed]

- InvenSense. T5837 Bottom Port PDM Digital Output Multi-Mode Microphone. Available online: https://invensense.tdk.com/download-pdf/t5837-datasheet/ (accessed on 23 May 2023).

- InvenSense. ICS-43434 Multi-Mode Microphone with I2S Digital Output Datasheet. Available online: https://invensense.tdk.com/download-pdf/ics-43434-datasheet/ (accessed on 23 May 2023).

- InvenSense. ICS-40310 Ultra-low Current, Low-Noise Microphone with Analog Output Datasheet. Available online: https://invensense.tdk.com/download-pdf/ics-40310-datasheet/ (accessed on 23 May 2023).

- Infineon. IM70A135V01 High Performance Analog XENSIV™ MEMS Microphone. Available online: https://www.infineon.com/cms/cn/product/sensor/mems-microphones/mems-microphones-for-consumer/ (accessed on 23 May 2023).

- Infineon. IM68A130V01 High Performance Analog XENSIV™ MEMS Microphone. Available online: https://www.infineon.com/cms/cn/product/sensor/mems-microphones/mems-microphones-for-consumer/ (accessed on 23 May 2023).

- Infineon. IM70D122V01 XENSIV™ Digital PDM MEMS Microphone. Available online: https://www.infineon.com/cms/cn/product/sensor/mems-microphones/mems-microphones-for-consumer/ (accessed on 23 May 2023).

- Nebhen, J.; Ferreira, P.M. A Chopper Negative-R Delta-Sigma ADC for Audio MEMS Sensors. CMES-Comput. Model. Eng. Sci. 2022, 130, 607–631. [Google Scholar] [CrossRef]

- Quintero, A.; Cardes, F.; Perez, C.; Buffa, C.; Wiesbauer, A.; Hernandez, L. A VCO-Based CMOS Readout Circuit for Capacitive MEMS Microphones. Sensors 2019, 19, 4126. [Google Scholar] [CrossRef] [PubMed]

- Maezawa, K.; Mori, M.; Andoh, H. Noise Floor Reduction in Frequency Delta-Sigma Modulation Microphone Sensors. Sensors 2021, 21, 3470. [Google Scholar] [CrossRef] [PubMed]

- Nikolić, M.; Florian, W.; Gaggl, R.; Liao, L. A 125dBSPL 1%-THD, 115 μA MEMS Microphone Using Passive Pre-Distortion Technique 2023. In Proceedings of the ESSCIRC 2023—IEEE 49th European Solid State Circuits Conference (ESSCIRC), Lisbon, Portugal, 11–14 September 2023; pp. 209–212. [Google Scholar] [CrossRef]

- Lee, B.; Yang, J.; Cho, J.S.; Kim, S. A Low-Power Digital Capacitive MEMS Microphone Based on a Triple-Sampling Delta-Sigma ADC With Embedded Gain. IEEE Access 2022, 10, 75323–75330. [Google Scholar] [CrossRef]

- Silva, J.; Moon, U.; Steensgaard, J.; Temes, G.C. Wideband low-distortion delta-sigma ADC topology. Electron. Lett. 2001, 37, 737–738. [Google Scholar] [CrossRef]

- Verma, N.; Chandrakasan, A.P. An Ultra Low Energy 12-bit Rate-Resolution Scalable SAR ADC for Wireless Sensor Nodes. IEEE J. Solid-State Circuits 2007, 42, 1196–1205. [Google Scholar] [CrossRef]

- Li, S.; Mukherjee, A.; Sun, N. A 174.3-dB FoM VCO-Based CT ΔΣ Modulator With a Fully-Digital Phase Extended Quantizer and Tri-Level Resistor DAC inshould be a space130-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 1–13. [Google Scholar] [CrossRef]

- Gutierrez, E.; Hernandez, L.; Cardes, F.; Rombouts, P. A Pulse Frequency Modulation Interpretation of VCOs Enabling VCO-ADC Architectures with Extended Noise Shaping. IEEE Trans. Circuits Syst. Regul. Pap. 2018, 65, 444–457. [Google Scholar] [CrossRef]

- Fanyang, L.; Shuying, C. A Highly Digital ADC with Enhanced Accuracy Using a Simple Ripple-Transferring Replica Pseudo PLL Loop Technique. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 197–201. [Google Scholar] [CrossRef]

- Jawed, S.A.; Nielsen, J.H.; Gottardi, M.; Baschirotto, A.; Bruun, E. A multifunction low-power preamplifier for MEMS capacitive microphones. In Proceedings of the Esscirc, Athens, Greece, 14–18 September 2009. [Google Scholar]

- Barbieri, A.; Nicollini, G. 100+ dB A-Weighted SNR Microphone Preamplifier with On-Chip Decoupling Capacitors. IEEE J. Solid-State Circuits 2012, 47, 2737–2750. [Google Scholar] [CrossRef]

- Oh, S.; Jang, T.; Choo, K.D.; Blaauw, D.; Sylvester, D. A 4.7uW switched-bias MEMS microphone preamplifier for ultra-low-power voice interfaces. In Proceedings of the Symposium on Vlsi Circuits, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Jawed, S.A.; Cattin, D.; Gottardi, M.; Massari, N.; Baschirotto, A. A low-power interface for the readout and motion-control of a MEMS capacitive sensor. In Proceedings of the IEEE International Workshop on Advanced Motion Control, Trento, Italy, 26–28 March 2008. [Google Scholar]

- Cheng, A. Design of a Readout Scheme for a MEMS Microphone. Electr. Eng. Math. Comput. Sci. 2009. [Google Scholar]

- Citakovic, J.; Hovesten, P.F.; Rocca, G.; van Halteren, A.; Rombach, P.; Stenberg, L.J.; Andreani, P.; Bruun, E. A compact CMOS MEMS microphone with 66 dB SNR. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 350–351. [Google Scholar] [CrossRef]

- Ersoy, S.; van Veldhoven, R.H.; Sebastiano, F.; Reimann, K.; Makinwa, K.A. A 0.25mm2 AC-biased MEMS microphone interface with 58dBA SNR. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 382–383. [Google Scholar] [CrossRef]

- Resources, T.I.D. Speech Recognition Reference Design on the C5535 eZdspTM. Available online: https://www.ti.com/tool/TIDEP0066 (accessed on 23 May 2023).

| Product | Producer | Typical Voltage (V) | Typical Current (µA) | SNR (dBA) | Output Type | Topology |

|---|---|---|---|---|---|---|

| T5837 [14] | InvenSense | 1.8 | 310 | 68 | Digital | LDO + ADC + PDM |

| ICS-43434 [15] | InvenSense | 1.8/3.3 | 310 | 65 | Digital | LDO + ADC + IS |

| ICS-40310 [16] | InvenSense | 0.9–1.3 | 19.5 | 64 | Analog | LDO + Amplifier |

| IM70A135 [17] | Infineon | 1.5–3.0 | 170 | 70 | Analog | LDO + Amplifier |

| IM68A130 [18] | Infineon | 2.4–3.6 | 110 | 68 | Analog | LDO + Amplifier |

| IM70D122 [19] | Infineon | 1.6–3.6 | 980 | 70 | Digital | LDO + ADC + PDM |

| Blocks | Power (µW) |

|---|---|

| ALPF | 9 |

| VCOS, SCG and FPDS | ∼23 |

| CMFFP | ∼8 |

| CSAFB | ∼9 |

| CSARB | 8 |

| Whole System | 57 |

| Ref# | [4] | [7] | [12] | [32] | [36] | This Work |

|---|---|---|---|---|---|---|

| Process | 280 nm | 180 nm | 180 nm | 180 nm | 160 nm | 180 nm |

| VDD (V) | 2.5 | 1.2 | 3.3 | 1.4 | 4.0∼6.0 | 1.2 |

| Area (mm) | 1 | 0.402 | 0.55 | 0.07 | 0.25 | 0.52 |

| THD @1 kHz (%@dB SPL) | / | 0.25@94 | / | 0.6@94 | 0.5@94 | 0.035@94 |

| Input-referred noise | 8 nV/sqrHz | 2.6/5.7 µ | / | 7.3 µ | ∼30 nV/sqrHz | ∼10 nV/sqrHz |

| Power (µW) | 2400 | <15 | 4500∼15,000 | 5 | 2000∼3000 | <57 |

| Gain range (dB) | 65 | 22∼40 | −7.88 ∼11.81 | 9.6 | / | 20∼40 |

| MEMS sensitivity (dBV/Pa) | / | −37 | −53 | −29.5 | −35.1 | −51.3 |

| Output signal type | Digital | Digital | Analog | Analog | Analog | Digital |

| Topology | Pre-amplifier + ADC | Pre-amplifier + SAR-ADC | Pre-amplifier | Pre-amplifier | Pre-amplifier | VCO-based |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, F.; Yin, T.; Wu, S.; Deng, W. A Compact MEMS Microphone Digital Readout System Using LDO and PPA-Less VCO-Based Delta-Sigma Modulation Technique. Electronics 2023, 12, 5014. https://doi.org/10.3390/electronics12245014

Li F, Yin T, Wu S, Deng W. A Compact MEMS Microphone Digital Readout System Using LDO and PPA-Less VCO-Based Delta-Sigma Modulation Technique. Electronics. 2023; 12(24):5014. https://doi.org/10.3390/electronics12245014

Chicago/Turabian StyleLi, Fanyang, Tao Yin, Shuwen Wu, and Wenren Deng. 2023. "A Compact MEMS Microphone Digital Readout System Using LDO and PPA-Less VCO-Based Delta-Sigma Modulation Technique" Electronics 12, no. 24: 5014. https://doi.org/10.3390/electronics12245014