Power and Signal-to-Noise Ratio Optimization in Mesh-Based Hybrid Optical Network-on-Chip Using Semiconductor Optical Amplifiers

Abstract

:1. Introduction

2. Related Work

2.1. Insertion Loss

2.2. Crosstalk Noise

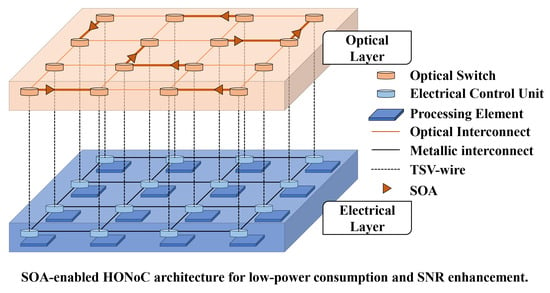

3. SOA-Enabled HONoC Architecture

- The SOA compensates for the insertion loss by amplifying the optical signal and reduces the burden of the laser source to reduce the total power consumption of the HONoC.

- An appropriate SOA gain can prevent the SNR degradation problem of the longest path due to the network size growth of the mesh-based HONoC.

3.1. Optical Router Model

3.2. Semiconductor Optical Amplifier

3.3. Constrained Optimization Problem in SOA-Enabled HONoC

4. Design Methodology for SOA-Enabled HONoC

4.1. SOA Placement Algorithm for Laser Source Power Saving and SNR Enhancement

| Algorithm 1. SOA Placement for Laser Source Power Saving and SNR Improvement | |

| Input: mesh size (, ), maximum hop count of possible paths without SOAs () | |

| Output: number of SOAs (), SOA spacing of X-axis and Y-axis (, ) | |

| 1: | = + |

| 2: | For from 1 to do |

| 3: | |

| 4: | [] = + ( |

| 5: | If [] then |

| 6: | = [ |

| 7: | |

| 8: | End if |

| 9: | End for |

| 10: | , |

| 11: | For from to do |

| 12: | For from 1 to do |

| 13: | Allocate SOA at east link of R(,) |

| 14: | |

| 15: | End for |

| 16: | |

| 17: | End for |

| 18: | For from to do |

| 19: | For from 1 to do |

| 20: | Allocate SOA at south link of R(,) |

| 21: | |

| 22: | End for |

| 23: | |

| 24: | End for |

4.2. Worst-Case Crosstalk Noise and SNR Analysis

- : the total number of routers in the optical signal path

- : the total number of SOAs in the optical signal path

- : the number of the routers between the th SOA and the th SOA in the optical signal path ()

- : the crosstalk noise introduced into the th router in the optical signal path

- : router loss, : SOA gain, : crosstalk noise coefficient

- The insertion loss and the crosstalk noise coefficient are the same regardless of ports. (

- The mesh size is .

- : the total number of routers in the crosstalk path

- : the total number of SOAs in the crosstalk path

- : the number of the routers between the th SOA and the th SOA in the crosstalk path

- (1)

- ,

- (2)

- ,

4.2.1. SNR Analysis with Multiple SOAs Using Segmented Regions in Mesh-Based HONoCs

4.2.2. SNR Analysis of the Longest Path

- (1)

- Case 1: ,

- (2)

- Case 2: ,

- (3)

- Case 3:

4.2.3. SNR Analysis inside Regions without SOAs

- (1)

- Case 1: ,

- (2)

- Case 2:

4.3. Minimum SOA Gain and Laser Source Power Allocation

4.3.1. Minimum SOA Gain Allocation

| Algorithm 2. Calculation for the Minimum SOA Gain | |

| Input: mesh size (, ), SOA spacing (, ) | |

| Output: minimum SOA gain () | |

| 1: | , |

| 2: | Ifthen |

| 3: | |

| 4: | Else |

| 5: | |

| 6: | End if |

| 7: | Ifthen |

| 8: | |

| 9: | Else |

| 10: | |

| 11: | End if |

| 12: | |

4.3.2. Minimum Laser Source Power Allocation

- (1)

- (2)

- (3)

5. Simulation Results

5.1. SNR Analysis

5.2. Power Consumption

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Vantrease, D.; Schreiber, R.; Monchiero, M.; McLaren, M.; Jouppi, N.P.; Fiorentino, M.; Davis, A.; Binkert, N.; Beausoleil, R.G.; Ahn, J.H. Corona: System implications of emerging nanophotonic technology. In Proceedings of the IEEE/ACM International Symposium on Computer Architecture (ISCA), Beijing, China, 21–25 June 2008. [Google Scholar]

- International Technology Roadmap for Semiconductors. Available online: http://www.itrs2.net (accessed on 27 September 2018).

- Shacham, A.; Bergman, K.; Carloni, L.P. Photonics Networks-on-Chip for Future Generations of Chip Multiprocessors. IEEE Trans. Comput. 2008, 57, 1246–1260. [Google Scholar] [CrossRef]

- Mo, K.H.; Ye, Y.; Wu, X.; Zhang, W.; Liu, W.; Xu, J. A Hierarchical Hybrid Optical-Electronic Network-on-Chip. In Proceedings of the 2010 IEEE Computer Society Annual Symposium on VLSI, Lixouri, Kefalonia, Greece, 5–7 July 2010. [Google Scholar]

- Gu, H.; Xu, J.; Wang, Z. A novel optical mesh network-on-chip for gigascale systems-on-chip. In Proceedings of the 2008 IEEE Asia Pacific Conference on Circuits and Systems, Macao, China, 30 November–3 December 2008. [Google Scholar]

- Lee, J.; Kim, Y.; Li, C.; Han, T. A shortest path adaptive routing technique for minimizing path collision in hybrid optical network-on-chip. J. Syst. Arch. 2013, 59, 1334–1347. [Google Scholar] [CrossRef]

- Lan, F.; Wu, R.; Zhang, C.; Pan, Y.; Cheng, K.-T.T. DLPS: Dynamic laser power scaling for optical Network-on-Chip. In Proceedings of the 2017 22nd Asia and South Pacific Design Automation Conference (ASP-DAC), Chiba, Japan, 16–19 January 2017. [Google Scholar]

- Xie, Y.; Nikdast, M.; Xu, J.; Zhang, W.; Li, Q.; Wu, X.; Ye, Y.; Wang, X.; Liu, W. Crosstalk noise and bit error rate analysis for optical network-on-chip. In Proceedings of the ACM/IEEE Design Automation Conference, Anaheim, CA, USA, 13–18 June 2010. [Google Scholar]

- Xiao, S.; Khan, M.H.; Shen, H.; Qi, M. Multiple-channel silicon micro-resonator bad filters for WDM applications. Opt. Express 2007, 15, 7489–7498. [Google Scholar] [CrossRef] [PubMed]

- Eid, N.; Boeck, R.; Jayatilleka, H.; Chrostowski, L.; Shi, W.; Jaeger, N.A.F. A silicon-on-insulator microring resonator filter with bent contradirectional couplers. In Proceedings of the 2016 IEEE Photonics Conference (IPC), Waikoloa, HI, USA, 2–6 October 2016. [Google Scholar]

- Fusella, E.; Cilardo, A. Lighting Up On-Chip Communications with Photonics: Design Tradeoffs for Optical NoC Architectures. IEEE Circuits Syst. Mag. 2016, 16, 4–14. [Google Scholar] [CrossRef]

- Poon, A.W.; Xu, F.; Luo, X. Cascaded active silicon microresonator array cross-connect circuits for WDM networks-on-chip. In Proceedings of the SPIE—The International Society for Optical Engineering, San Jose, CA, USA, 13 February 2008. [Google Scholar]

- Ding, W.; Tang, D.; Liu, Y.; Chen, L.; Sun, X. Compact and low crosstalk waveguide crossing using impedance matched metamaterial. Appl. Phys. Lett. 2010, 96, 111114. [Google Scholar] [CrossRef]

- Biberman, A.; Preston, K.; Hendry, G.; Sherwood-Droz, N.; Chan, J.; Levy, J.S.; Lipson, M.; Bergman, K. Photonic network-on-chip architectures using multilayer deposited silicon materials for high-performance chip multiprocessors. ACM J. Emerg. Technol. Comput. Syst. 2011, 7, 7. [Google Scholar] [CrossRef]

- Dong, P.; Qian, W.; Liao, S.; Liang, H.; Kung, C.-C.; Feng, N.-N.; Shafiiha, R.; Fong, J.; Feng, D.; Krishnamoorthy, A.V.; et al. Low Loss Silicon Waveguides for Application of Optical Interconnects. In Proceedings of the IEEE Photonics Society Summer Topicals 2010, Playa del Carmen, Mexico, 19–21 July 2010. [Google Scholar]

- Lee, B.G.; Biberman, A.; Dong, P.; Lipson, M.; Bergman, K. All-Optical Comb Switch for Multiwavelength Message Routing in Silicon Photonic Networks. IEEE Photonics Technol. Lett. 2008, 20, 767–769. [Google Scholar] [CrossRef]

- Sanchis, P.; Galan, J.V.; Brimont, A.; Griol, A.; Marti, J.; Piqueras, M.A.; Perdigues, J.M. Low-crosstalk in silicon-on-insulator waveguide crossings with optimized-angle. In Proceedings of the 2007 4th IEEE International Conference on Group IV Photonics, Tokyo, Japan, 19–21 September 2007. [Google Scholar]

- Chen, H.; Poon, A.W. Low-Loss Multimode-Interference-Based Crossings for Silicon Wire Waveguides. IEEE Photonics Technol. Lett. 2006, 18, 2260–2262. [Google Scholar] [CrossRef]

- Xie, Y.; Nikdast, M.; Xu, J.; Wu, X.; Zhang, W.; Ye, Y.; Wang, X.; Wang, Z.; Liu, W. Formal Worst-Case Analysis of Crosstalk Noise in Mesh-Based Optical Networks-on-Chip. IEEE Trans. Very Large Scale Integr. Syst. 2013, 21, 1823–1836. [Google Scholar] [CrossRef]

- Nikdast, M.; Xu, J.; Wu, X.; Zhang, W.; Ye, Y.; Wang, X.; Wang, Z.; Wang, Z. Systematic Analysis of Crosstalk Noise in Folded-Torus-Based Optical Networks-on-Chip. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2014, 33, 437–450. [Google Scholar] [CrossRef]

- Duong, L.H.K.; Nikdast, M.; Xu, J.; Wang, Z.; Thonnart, Y.; Beux, S.L.; Yang, P.; Wu, X.; Wang, Z. Coherent crosstalk noise analyses in ring-based optical interconnects. In Proceedings of the 2015 Design, Automation and Test in Europe Conference and Exhibition (DATE), Grenoble, France, 9–13 March 2015. [Google Scholar]

- Nikdast, M.; Xu, J.; Duong, L.H.K.; Wu, X.; Wang, Z.; Wang, X.; Wang, Z. Fat-Tree-Based Optical Interconnection Networks Under Crosstalk Noise Constraint. IEEE Trans. Very Large Scale Integr. Syst. 2014, 23, 156–169. [Google Scholar] [CrossRef]

- Rostami, A.; Baghban, H.; Maram, R. Nanostructure Semiconductor Optical Amplifiers, 1st ed.; Springer: Berlin, Germany, 2011; Available online: https://books.google.com.hk/books?hl=en&lr=&id=xN0PXG_38SIC&oi=fnd&pg=PR3&dq=Nanostructure+Semiconductor+Optical+Amplifiers&ots=A-G24LLZxf&sig=QA-Sb2u1vHjRxW_K80vxRLDUB4E&redir_esc=y#v=onepage&q=Nanostructure%20Semiconductor%20Optical%20Amplifiers&f=false (accessed on 16 September 2018).

- Thakkar, I.G.; Chittamuru, S.V.R.; Pasricha, S. Run-time laser power management in photonic NoCs with on-chip semiconductor optical amplifiers. In Proceedings of the 2016 Tenth IEEE/ACM International Symposium on Networks-on-Chip, Nara, Japan, 31 August–2 September 2016. [Google Scholar]

- Ye, Y.; Wu, X.; Xu, J.; Zhang, W.; Nikdast, M.; Wang, X. Holistic comparison of optical routers for chip multiprocessors. In Proceedings of the IEEE 2012 International Conference on Anti-Counterfeiting, Security and Identification (ASID), Taipei, Taiwan, 24–26 August 2012. [Google Scholar]

- Jiang, N.; Becker, D.U.; Michelogiannakis, G.; Balfour, J.; Towles, B.; Shaw, D.E.; Kim, J.; Dally, W.J. A detailed and flexible cycle-accurate Network-on-Chip simulator. In Proceedings of the 2013 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), Austin, TX, USA, 21–23 April 2013. [Google Scholar]

- Bogaerts, W.; Dumon, P.; Thourhout, D.V.; Baets, R. Low-loss, low-cross-talk crossings for silicon-on-insulator nanophotonic waveguides. Opt. Lett. 2007, 32, 2801–2803. [Google Scholar] [CrossRef] [PubMed]

- Chan, J.; Hendry, G.; Bergman, K.; Carloni, L.P. Physical-Layer Modeling and System-Level Design of Chip-Scale Photonic Interconnection Networks. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2011, 30, 1507–1520. [Google Scholar] [CrossRef]

- Maulini, R.; Lyakh, A.; Tsekoun, A.; Patel, C.K.N. λ~7.1 μm quantum cascade lasers with 19% wall-plug efficiency at room temperature. Opt. Express 2011, 19, 17203–17211. [Google Scholar] [CrossRef] [PubMed]

- Joshi, A.; Batten, C.; Kwon, Y.-J.; Beamer, S.; Shamim, I.; Asanovic, K.; Stojanovic, V. Silicon-photonic clos networks for global on-chip communication. In Proceedings of the 2009 3rd ACM/IEEE International Symposium on Networks-on-Chip, San Diego, CA, USA, 10–13 May 2009. [Google Scholar]

| Parameter | Definition | Value |

|---|---|---|

| Light confinement factor | ||

| Constant | ||

| Transparency carrier concentration | ||

| Length of the SOA active region | ||

| Threshold input current | ||

| Loss in the SOA active region | ||

| SOA gain linewidth |

| Loss | Value (dB) | Loss | Value (dB) |

|---|---|---|---|

| 0.50 | 0.38 | ||

| 0.88 | 0.50 | ||

| 0.88 | 1.00 | ||

| 0.63 | 0.63 | ||

| 0.38 | 0.38 | ||

| 1.00 | 0.50 | ||

| 0.50 | 0.38 | ||

| 0.88 | 0.88 |

| Parameter | Value | Reference |

|---|---|---|

| Waveguide crossing loss | –0.12 dB | [12] |

| Propagation loss per cm | –0.274 dB/cm | [15] |

| Power loss of CSE in OFF state | –0.04 dB | [13] |

| Power loss of CSE in ON state | –0.5 dB | [9] |

| Power loss of PSE in OFF state | –0.005 dB | [9] |

| Power loss of PSE in ON state | –0.5 dB | [9] |

| Crossing crosstalk coefficient | –45 dB | [27] |

| Crosstalk coefficient of PSE in OFF state | –20 dB | [28] |

| Crosstalk coefficient of PSE in ON state | –25 dB | [28] |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jang, J.Y.; Kim, M.S.; Li, C.-L.; Han, T.H. Power and Signal-to-Noise Ratio Optimization in Mesh-Based Hybrid Optical Network-on-Chip Using Semiconductor Optical Amplifiers. Appl. Sci. 2019, 9, 1251. https://doi.org/10.3390/app9061251

Jang JY, Kim MS, Li C-L, Han TH. Power and Signal-to-Noise Ratio Optimization in Mesh-Based Hybrid Optical Network-on-Chip Using Semiconductor Optical Amplifiers. Applied Sciences. 2019; 9(6):1251. https://doi.org/10.3390/app9061251

Chicago/Turabian StyleJang, Jun Yeong, Min Su Kim, Chang-Lin Li, and Tae Hee Han. 2019. "Power and Signal-to-Noise Ratio Optimization in Mesh-Based Hybrid Optical Network-on-Chip Using Semiconductor Optical Amplifiers" Applied Sciences 9, no. 6: 1251. https://doi.org/10.3390/app9061251