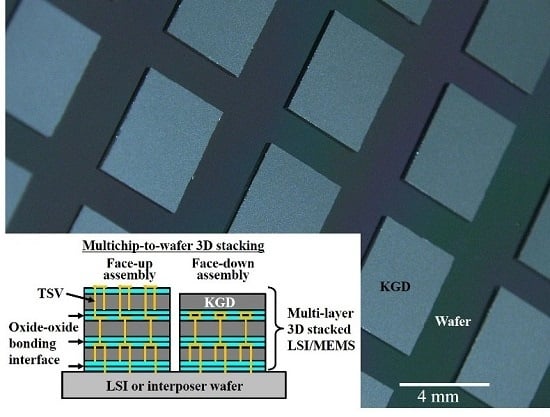

Oxide-Oxide Thermocompression Direct Bonding Technologies with Capillary Self-Assembly for Multichip-to-Wafer Heterogeneous 3D System Integration

Abstract

:1. Introduction

2. Results and Discussion

2.1. Evaluation of Interfacial Energies of Directly Bonded Wafers

2.2. Evaluation of Bonding Strengths of Directly Bonded Chips

2.3. Self-Assembly of Chips on Wafer

2.4. Impact of Plasma Activation on Oxide-Oxide Direct Bonding

3. Experimental Section

3.1. Chip/Wafer Fabrication

3.2. Self-Assembly

3.3. Contact Angle

3.4. Bonding Strength

3.5. Alignment Accuracy

3.6. Atomic Force Microscopy (AFM)

3.7. Atmospheric Pressure Ionization Mass Spectrometer (APIMS)

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Iyer, S.S. Three-dimensional integration: An industry perspective. MRS Bull. 2015, 40, 225–232. [Google Scholar] [CrossRef]

- Matsumoto, T.; Kudoh, Y.; Tahara, M.; Yu, K.-H.; Miyakawa, N.; Itani, H.; Ichikizaki, T.; Fujiwara, A.; Tsukamoto, H.; Koyanagi, M.; et al. Three-Dimensional Integration Technology Based on Wafer Bonding Technique Using Micro-Bumps. In Proceedings of the 1995 International Conference on Solid State Devices and Materials (SSDM), Osaka, Japan, 21–24 August 1995; pp. 1073–1074.

- Ramm, P.; Bollmann, D.; Braun, R.; Buchner, R.; Cao-Minh, U.; Engelhardt, M.; Errmann, G.; Grassl, T.; Hieber, T.K.; Hubner, H.; et al. Three dimensional metallization for vertically integrated circuits. Microelectron. Eng. 1997, 37–38, 39–47. [Google Scholar] [CrossRef]

- Koyanagi, M.; Kurino, H.; Lee, K.W.; Sakuma, K.; Miyakawa, N.; Itani, H. Future system-on-silicon LSI chips. IEEE Micro 1998, 18, 17–22. [Google Scholar] [CrossRef]

- Koyanagi, M.; Nakamura, T.; Yamada, Y.; Kikuchi, H.; Fukushima, T.; Tanaka, T.; Kurino, H. Three-dimensional integration technology based on wafer bonding with vertical buried interconnections. IEEE Trans. Electron Devices 2006, 53, 2799–2808. [Google Scholar] [CrossRef]

- Lee, K.; Noriki, A.; Kiyoyama, K.; Fukushima, T.; Tanaka, T.; Koyanagi, M. Three-dimensional hybrid integration technology of CMOS, MEMS, and photonics circuits for optoelectronic heterogeneous integrated systems. IEEE Trans. Electron Devices 2011, 58, 748–757. [Google Scholar] [CrossRef]

- Fukushima, T.; Iwata, E.; Ohara, Y.; Murugesan, M.; Bea, J.; Lee, K.; Tanaka, T.; Koyanagi, M. Multichip-to-wafer three-dimensional integration technology using chip self-assembly with excimer lamp irradiation. IEEE Trans. Electron Devices 2012, 59, 2956–2963. [Google Scholar] [CrossRef]

- Kondo, T.; Takazawa, N.; Takemoto, Y.; Tsukimura, M.; Saito, H.; Kato, H.; Aoki, J.; Kobayashi, K.; Suzuki, S.; Gomi, Y.; et al. 3-D-stacked 16-mpixel global shutter CMOS image sensor using reliable in-pixel four million microbump interconnections with 7.6-μm pitch. IEEE Trans. Electron Devices 2016, 63, 128–137. [Google Scholar] [CrossRef]

- Ohyama, M.; Nimura, M.; Mizuno, J.; Shoji, S.; Tamura, M.; Enomoto, T.; Shigetou, A. Hybrid Bonding of Cu/Sn Microbump and Adhesive with Silica Filler for 3D Interconnection of Single Micron Pitch. In Proceedings of the Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015; pp. 325–330.

- Lee, K.-W.; Bea, J.-C.; Fukushima, T.; Suresh, R.; Wu, X.; Tanaka, T.; Koyanagi, M. Novel hybrid bonding technology using ultra-high density Cu nano-pillar for exascale 2.5D/3D integration. IEEE Electron Device Lett. 2016, 37, 81–83. [Google Scholar] [CrossRef]

- Fukushima, T.; Yamada, Y.; Kikuchi, H.; Koyanagi, M. New Three-Dimensional Integration Technology Using Self-Assembly Technique. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2005; pp. 359–362.

- Fukushima, T.; Iwata, E.; Ohara, Y.; Murugesan, M.; Bea, J.-C.; Lee, K.-W.; Tanaka, T.; Koyanagi, M. Multichip self-assembly technology for advanced die-to-wafer 3-D integration to precisely align known good dies in batch processing. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1873–1884. [Google Scholar] [CrossRef]

- Fukushima, T.; Bea, J.C.; Kino, H.; Nagai, C.; Murugesan, M.; Hashiguchi, H.; Lee, K.-W.; Tanaka, T.; Koyanagi, M. Reconfigured-wafer-to-wafer 3D integration using parallel self-assembly of chips with Cu-SnAg microbumps and a NCF. IEEE Trans. Electron Devices 2014, 61, 533–539. [Google Scholar] [CrossRef]

- Sakuma, K.; Skordas, S.; Zitz, J.; Perfecto, E.; Guthrie, W.; Guerin, L.; Langlois, R.; Liu, H.; Ramachandran, K.; Lin, W.; et al. Bonding Technologies for Chip Level and Wafer Level 3D integration. In Proceedings of the 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 647–654.

- Ito, Y.; Fukushima, T.; Lee, K.-W.; Choki, K.; Tanaka, T.; Koyanagi, M. Direct Multichip-to-Wafer 3D Integration Technology Using Flip-Chip Self-Assembly of NCF-Covered Known Good Dies. In Proceedings of the 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 856–861.

- Ito, Y.; Murugesan, M.; Kino, H.; Fukushima, T.; Lee, K.-W.; Choki, K.; Tanaka, T.; Koyanagi, M. Development of Highly-Reliable Microbump Bonding Technology Using Self-Assembly of NCF-Covered KGDs and Multi-Layer 3D Stacking Challenges. In Proceedings of the IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015; pp. 336–331.

- Goto, M.; Hagiwara, K.; Iguchi, Y.; Ohtake, H.; Saraya, T.; Higurashi, E.; Toshiyoshi, H.; Hiramoto, T. 3-D silicon-on-insulator integrated circuits with NFET and PFET on separate layers using Au/SiO2 hybrid bonding. IEEE Trans. Electron Devices 2014, 61, 2886–2892. [Google Scholar] [CrossRef]

- Enquist, P.; Fountain, G.; Petteway, C.; Hollingsworth, A.; Grady, H. Low Cost of Ownership Scalable Copper Direct Bond Interconnect 3D IC Technology for Three Dimensional Integrated Circuit Applications. In Proceedings of the IEEE International Conference on 3D System Integration (3DIC), San Francisco, CA, USA, 28–30 September 2009; pp. 1–6.

- Aoki, M.; Furuta, F.; Hozawa, K.; Hanaoka, Y.; Kikuchi, H.; Yanagisawa, A.; Mitsuhashi, T.; Takeda, K. Fabricating 3D Integrated CMOS Devices by Using Wafer Stacking and Via-Last TSV Technologies. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 727–730.

- Sanchez, L.; Bally, L.; Montmayeul, B.; Fournel, F.; Dafonseca, J.; Augendre, E.; Cioccio, L.D.; Carron, V.; Signamarcheix, T.; Taibi, R.; et al. Chip to Wafer Direct Bonding Technologies for High Density 3D Integration. In Proceedings of the IEEE 62nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2012; pp. 1960–1964.

- Mermoz, S.; Sanchez, L.; Cioccio, L.D.; Berthier, J.; Deloffre, E.; Coudrain, P.; Fretigny, C. High Density Chip-to-Wafer Integration Using Self-Assembly: On the Performances of Directly Interconnected Structures Made by Direct Copper/Oxyde Bonding. In Proceedings of the IEEE 15th Electronics Packaging Technology Conference (EPTC 2013), Singapore, 11–13 December 2013; pp. 162–167.

- Moriceau, H.; Rieutord, F.; Fournel, F.; Imbert, B.; Cioccio, L.D.; Baudin, F.; Rauer, C.; Morales, C. Low Temperature Direct Bonding Assisted by CMP and Plasma Activation. In Proceedings of the IEEE 3rd International Workshop on Low Temperature Bonding for 3D Integration (LTB-3D), Tokyo, Japan, 22–23 May 2012; p. 123.

- Batra, P.; Skordas, S.; LaTulipe, D.; Winste, K.; Kothandaraman, C.; Himmel, B.; Maier, G.; He, B.; Gamage, D.W.; Golz, J.; et al. Three-dimensional wafer stacking using Cu TSV integrated with 45 nm high performance SOI-CMOS embedded DRAM technology. J. Low Power Electron. Appl. 2014, 4, 77–89. [Google Scholar] [CrossRef]

- Sugimoto, F.; Arimoto, Y. Bond strength of bonded SOI wafers. Jpn. J. Appl. Phys. 1992, 31, 975–978. [Google Scholar] [CrossRef]

- Hirayama, T. Rational 3-Dimensional Devices. In Proceedings of the 3D Architectures for Semiconductor Integration and Packaging Conference (3D ASIP), Redwood City, CA, USA, 15–17 December 2015.

- Tong, Q.-Y.; Cha, G.; Gafiteanu, R.; Gösele, U. Low temperature wafer direct bonding. J. Microelectromech. Syst. 1994, 3, 29–35. [Google Scholar] [CrossRef]

- Fukushima, T.; Iwata, E.; Konno, T.; Bea, J.C.; Lee, K.W.; Tanaka, T.; Koyanagi, M. Surface tension-driven chip self-assembly with load-free hydrogen fluoride-assisted direct bonding at room temperature for three-dimensional integrated circuits. Appl. Phys. Lett. 2010, 96, 154105. [Google Scholar] [CrossRef]

- Fukushima, T.; Hashiguchi, H.; Bea, J.; Ohara, Y.; Murugesan, M.; Lee, K.-W.; Tanaka, T.; Koyanagi, M. New Chip-to-Wafer 3D Integration Technology Using Hybrid Self-Assembly and Electrostatic Temporary Bonding. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012; pp. 789–792.

- Hashiguchi, H.; Yonekura, H.; Fukushima, T.; Murugesan, M.; Kino, H.; Lee, K.-W.; Tanaka, T.; Koyanagi, M. Plasma Assisted Multichip-to-Wafer Direct Bonding Technology for Self-Assembly Based 3D Integration. In Proceedings of the IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015; pp. 1458–1463.

- Stengle, R.; Tan, T.; Gösele, U. A model for the silicon wafer bonding process. Jpn. J. Appl. Phys. 1989, 28, 1735–1741. [Google Scholar] [CrossRef]

- Plach, T.; Hingerl, K.; Tollabimazraehno, S.; Hesser, G.; Dragoi, V.; Wimplinger, M. Mechanisms for room temperature direct wafer bonding. J. Appl. Phys. 2013, 113, 094905. [Google Scholar] [CrossRef]

- Vandroux, L.; Cioccio, L.D.; Gueguen, P. Treatment, Before the Bonding of a Mixed Cu-Oxide Surface, by a Plasma Containing Nitrogen and Hydrogen. U.S. Patent 13/818,864, 20 June 2013. [Google Scholar]

- Rauer, C.; Moriceau, H.; Fournel, F.; Charvet, A.M.; Morales, C.; Rochat, N.; Vandroux, L.; Rieutord, F.; McCormick, T.; Raduc, I.; et al. Treatments of deposited SiOx surfaces enabling low temperature direct bonding. ECS J. Solid State Sci. Technol. 2013, 2, Q147–Q150. [Google Scholar] [CrossRef]

- Fournel, F.; Martin-Cocher, C.; Radisson, D.; Larrey, V.; Beche, E.; Morales, C.; Delean, P.A.; Rieutord, F.; Moriceaua, H. Water stress corrosion in bonded structures. ECS J. Solid State Sci. Technol. 2015, 4, P124–P130. [Google Scholar] [CrossRef]

- Maszara, W.P.; Goetz, G.; Caviglia, A.; McKitterick, J.B. Bonding of silicon wafers for silicon-on-insulator. J. Appl. Phys. 1988, 64, 4943–4950. [Google Scholar] [CrossRef]

- Gilman, J.J. Direct measurements of the surface energies of crystals. J. Appl. Phys. 1960, 31, 2208–2218. [Google Scholar] [CrossRef]

- Vallin, O.; Jonsson, K.; Lindberg, U. Adhesion quantification methods for wafer bonding. Mater. Sci. Eng. 2005, 50, 109–165. [Google Scholar] [CrossRef]

- Sabbione, C.; di Cioccio, L.; Vandroux, L.; Nieto, J.-P.; Rieutord, F. Low temperature direct bonding mechanisms of tetraethyl orthosilicate based silicon oxide films deposited by plasma enhanced chemical vapor deposition. J. Appl. Phys. 2012, 112, 063501. [Google Scholar] [CrossRef]

- Takagi, H.; Maeda, R.; Chung, T.R.; Hosoda, N.; Suga, T. Effect of surface roughness on room-temperature wafer bonding by Ar beam surface activation. Jpn. J. Appl. Phys. 1998, 37, 4197–4203. [Google Scholar] [CrossRef]

- Sato, K.; Ito, K.; Hata, S.; Shimokohbe, A. Self-alignment of microparts using liquid surface tension—behavior of micropart and alignment characteristics. Precis. Eng. 2003, 27, 42–50. [Google Scholar] [CrossRef]

- Sariola, V.; Jääskeläinen, M.; Zhou, Q. Hybrid microassembly combining robotics and water droplet self-alignment. IEEE Trans. Robot. 2010, 26, 965–977. [Google Scholar] [CrossRef]

- Arutinov, G.; Mastrangeli, M.; Smits, E.C.P.; van Heck, G.; den Toonder, J.M.J.; Dietzel, A. Foil-to-foil system integration through capillary self-alignment directed by laser patterning. J. Microelectromech. Syst. 2015, 24, 126–133. [Google Scholar] [CrossRef]

- Ito, Y.; Fukushima, T.; Kino, H.; Lee, K.-W.; Tanaka, T.; Koyanagi, M. Impact of chip-edge structures on alignment accuracies of self-assembled dies for microelectronic system integration. J. Microelectromech. Syst. 2016, 25, 91–100. [Google Scholar] [CrossRef]

- Ventosa, C.; Rieutord, F.; Libralesso, L.; Morales, C.; Fournel, F.; Moriceau, H. Hydrophilic low-temperature direct wafer bonding. J. Appl. Phys. 2008, 104, 123524. [Google Scholar] [CrossRef]

- Ventosa, C.; Morales, C.; Libralesso, L.; Fournel, F.; Papon, A.M.; Lafond, D.; Moriceau, H.; Penot, J.D.; Rieutord, F. Mechanism of thermal silicon oxide direct wafer bonding. Electrochem. Solid-State Lett. 2009, 12, H373–H375. [Google Scholar] [CrossRef]

- Jimbo, T.; Sakai, S.; Katuyama, K.; Ito, M.; Tomioka, H. Thermal Desorption Behavior of Adsorbed Materials on Wafer Surfaces. In Proceedings of the IEEE International Symposium on Semiconductor Manufacturing Conference Proceedings, San Francisco, CA, USA, 6–8 October 1997; pp. E5–E8.

| Bonding Conditions | TH/TH | TH/TH | PE/PE |

| N2/— | N2/— | N2/— | |

| 0.8 N/chip | 10 N/chip | 10 N/chip | |

| Bonding Yield (%) | 33 | 92 | 92 |

© 2016 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fukushima, T.; Hashiguchi, H.; Yonekura, H.; Kino, H.; Murugesan, M.; Bea, J.-C.; Lee, K.-W.; Tanaka, T.; Koyanagi, M. Oxide-Oxide Thermocompression Direct Bonding Technologies with Capillary Self-Assembly for Multichip-to-Wafer Heterogeneous 3D System Integration. Micromachines 2016, 7, 184. https://doi.org/10.3390/mi7100184

Fukushima T, Hashiguchi H, Yonekura H, Kino H, Murugesan M, Bea J-C, Lee K-W, Tanaka T, Koyanagi M. Oxide-Oxide Thermocompression Direct Bonding Technologies with Capillary Self-Assembly for Multichip-to-Wafer Heterogeneous 3D System Integration. Micromachines. 2016; 7(10):184. https://doi.org/10.3390/mi7100184

Chicago/Turabian StyleFukushima, Takafumi, Hideto Hashiguchi, Hiroshi Yonekura, Hisashi Kino, Mariappan Murugesan, Ji-Chel Bea, Kang-Wook Lee, Tetsu Tanaka, and Mitsumasa Koyanagi. 2016. "Oxide-Oxide Thermocompression Direct Bonding Technologies with Capillary Self-Assembly for Multichip-to-Wafer Heterogeneous 3D System Integration" Micromachines 7, no. 10: 184. https://doi.org/10.3390/mi7100184