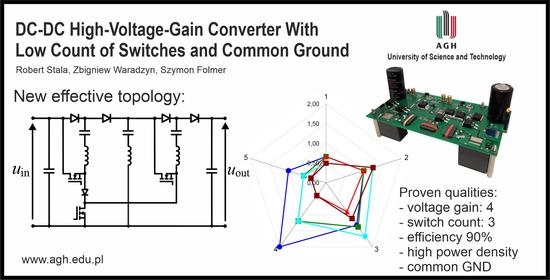

DC-DC High-Voltage-Gain Converters with Low Count of Switches and Common Ground

Abstract

:1. Introduction

2. Operating Principle of the Converters

2.1. Switching Strategy Concepts for the LCSCVMa

2.1.1. Simulation Results of the Switching Strategy C1

2.1.2. Simulation Results of the Switching Strategy C2

2.1.3. Simulation Results of the Switching Strategy C3

2.2. Switching Strategy Concepts for the LCSCVMb

2.2.1. Simulation Results of the Switching Strategy C4

2.2.2. Simulation Results of the Switching Strategy C5

2.3. Comparison among the Topologies and Switching Strategies

- Number of components,

- Voltage gain,

- The lowest frequency in the input current (fac_in),

- The lowest frequency in the output current (fac_out),

- Voltage pulsation on capacitors (UC1p-p, UC2p-p, UC3p-p),

- rms values of inductor currents (IL1_rms, IL2_rms, IL3_rms),

- Maximum values of inductor currents (IL1_max, IL2_ max, IL3_ max),

- Symmetry of inductor currents (Sym_iL).

3. Efficiency Model of the LCSCVM Converters

4. Experimental Verification

4.1. Experimental Setup

4.2. Test Results

5. Conclusions

- The major idea of the proposed new converters is based on the elimination of the number of switches in a voltage multiplier (SCVM), while maintaining its proper operation. By the modification of an SCVM, the new topology concepts LCSCVMa and LCSCVMb were proposed, with a reduced number of switching cells and redesigned functions of the diodes. Depending on the technology of practical implementation, either of these converters can be more attractive than the other.

- Various switching strategies are possible for the converters, which affect the parameters of operation related to switching losses and the sizing of the passive components of the converter, but also the required input and output filters.

- The converter operates properly with a wide range of output loads.

- From the compared results, it follows that the most effective topology, the LCSCVMb, can operate with nearly the lowest parameters of AC component in the voltages on capacitors, and the highest frequency in the input and output current. This allows for a reduction of the converter volume, especially by optimizing the input and output filters.

- The discussed converters demonstrated an improvement in the SCVM topology, which may result in a prospective cost reduction.

Author Contributions

Funding

Conflicts of Interest

References

- Ioinovici, A. Switched-capacitor power electronics circuit. IEEE Circuits Syst. Mag. 2001, 1, 37–42. [Google Scholar] [CrossRef]

- Tofoli, F.L.; de Castro Pereira, D.; de Paula, W.J.; Júnior, D.S.O. Survey on non-isolated high-voltage step-up dc–dc topologies based on the boost converter. IET Power Electron. 2015, 8, 2044–2057. [Google Scholar] [CrossRef] [Green Version]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Wu, G.; Ruan, X.; Ye, Z. Nonisolated High Step-Up DC–DC Converters Adopting Switched-Capacitor Cell. IEEE Trans. Ind. Electron. 2015, 62, 383–393. [Google Scholar] [CrossRef]

- Li, W.; He, X. Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications. IEEE Trans. Ind. Electron. 2011, 58, 1239–1250. [Google Scholar] [CrossRef]

- Raghavendra, K.V.G.; Zeb, K.; Muthusamy, A.; Krishna, T.N.V.; Kumar, S.V.S.V.P.; Kim, D.-H.; Kim, M.-S.; Cho, H.-G.; Kim, H.-J. A Comprehensive Review of DC–DC Converter Topologies and Modulation Strategies with Recent Advances in Solar Photovoltaic Systems. Electronics 2020, 9, 31. [Google Scholar] [CrossRef] [Green Version]

- Liu, W.; Niazi, K.A.K.; Kerekes, T.; Yang, Y. A Review on Transformerless Step-Up Single-Phase Inverters with Different DC-Link Voltage for Photovoltaic Applications. Energies 2019, 12, 3626. [Google Scholar] [CrossRef] [Green Version]

- Xiao, H. Overview of Transformerless Photovoltaic Grid-Connected Inverters. IEEE Trans. Power Electron. 2020, 36, 533–548. [Google Scholar] [CrossRef]

- Alluhaybi, K.; Batarseh, I.; Hu, H. Comprehensive Review and Comparison of Single-Phase Grid-Tied Photovoltaic Microinverters. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1310–1329. [Google Scholar] [CrossRef]

- Tran, V.-T.; Nguyen, M.-K.; Choi, Y.-O.; Cho, G.-B. Switched-Capacitor-Based High Boost DC-DC Converter. Energies 2018, 11, 987. [Google Scholar] [CrossRef] [Green Version]

- Lee, J.; Jeong, Y.; Han, B. An Isolated DC/DC Converter Using High-Frequency Unregulated LLC Resonant Converter for Fuel Cell Applications. IEEE Trans. Ind. Electron. 2011, 58, 2926–2934. [Google Scholar] [CrossRef]

- Cao, D.; Peng, F.Z. A family of zero current switching switched-capacitor dc-dc converters. In Proceedings of the 2010 25th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1365–1372. [Google Scholar]

- Waradzyn, Z.; Stala, R.; Mondzik, A.; Penczek, A.; Skala, A.; Pirog, S. Efficiency analysis of MOSFET-based air-choke resonant DC–DC step-up switched-capacitor voltage multipliers. IEEE Trans. Ind. Electron. 2017, 64, 8728–8738. [Google Scholar] [CrossRef]

- Penczek, A.; Mondzik, A.; Waradzyn, Z.; Stala, R.; Skała, A.; Piróg, S. Switching strategies of a resonant switched-capacitor voltage multiplier. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’ 17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. 1–10. [Google Scholar]

- Xie, W.; Li, S.; Zheng, Y.; Smedley, K.; Wang, J.; Ji, Y.; Yu, J. A Step-up Series-parallel Resonant Switched-capacitor Converter with Extended Line Regulation Range. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 2150–2154. [Google Scholar]

- Stala, R.; Waradzyn, Z.; Mondzik, A.; Penczek, A.; Skała, A. DC–DC High Step-up Converter with Low Count of Switches Based on Resonant Switched-Capacitor Topology. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE’ 19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. 1–10. [Google Scholar]

- Xie, H.; Li, R. A Novel Switched-Capacitor Converter with High Voltage Gain. IEEE Access 2019, 7, 107831–107844. [Google Scholar] [CrossRef]

- Lei, H.; Hao, R.; You, X.; Li, F. Nonisolated High Step-Up Soft-Switching DC–DC Converter with Interleaving and Dickson Switched-Capacitor Techniques. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 2007–2021. [Google Scholar] [CrossRef]

- He, L.; Zheng, Z. High step-up DC–DC converter with switched-capacitor and its zero-voltage switching realization. IET Power Electron. 2017, 10, 630–636. [Google Scholar] [CrossRef]

- Chen, M.; Li, K.; Hu, J.; Ioinovici, A. Generation of a Family of Very High DC Gain Power Electronics Circuits Based on Switched-Capacitor-Inductor Cells Starting from a Simple Grap. IEEE Trans. Circuits Syst. 2016, 63, 2381–2392. [Google Scholar] [CrossRef]

- Kawa, A.; Stala, R. A multilevel switched capacitor DC–DC converter. An analysis of resonant operation conditions. Power Electron. Drives 2016, 1, 35–53. [Google Scholar]

- Kawa, A.; Stala, R. SiC-Based Bidirectional Multilevel High-Voltage Gain Switched-Capacitor Resonant Converter with Improved Efficiency. Energies 2020, 13, 2445. [Google Scholar] [CrossRef]

- Li, S.; Zheng, Y.; Wu, B.; Smedley, K.M. A Family of Resonant Two-Switch Boosting Switched-Capacitor Converter with ZVS Operation and a Wide Line Regulation Range. IEEE Trans. Power Electron. 2018, 33, 448–459. [Google Scholar] [CrossRef]

- Qian, W.; Cao, D.; Cintron-Rivera, J.G.; Gebben, M.; Wey, D.; Peng, F.Z. A Switched-Capacitor DC–DC Converter with High Voltage Gain and Reduced Component Rating and Count. IEEE Trans. Ind. Appl. 2012, 48, 1397–1406. [Google Scholar] [CrossRef]

- Xiong, S.; Tan, S. Cascaded High-Voltage-Gain Bidirectional Switched-Capacitor DC–DC Converters for Distributed Energy Resources Applications. IEEE Trans. Power Electron. 2017, 32, 1220–1231. [Google Scholar] [CrossRef]

- Stala, R.; Piróg, S. DC–DC boost converter with high voltage gain and a low number of switches in multisection switched capacitor topology. Arch. Electr. Eng. 2018, 67, 617–627. [Google Scholar]

- Kumar, A.; Wang, Y.; Pan, X.; Raghuram, M.; Singh, S.K.; Xiong, X.; Tripathi, A.K. Switched-LC Based High Gain Converter with Lower Component Count. IEEE Trans. Ind. Appl. 2020, 56, 2816–2827. [Google Scholar] [CrossRef]

- Li, S.; Smedley, K.M.; Caldas, D.R.; Martins, Y.W. Hybrid Bidirectional DC–DC Converter with Low Component Counts. IEEE Trans. Ind. Appl. 2018, 54, 1573–1582. [Google Scholar] [CrossRef]

- Waradzyn, Z.; Stala, R.; Skała, A.; Mondzik, A.; Penczek, A. A cost-effective resonant switched-capacitor dc-dc boost converter—Experimental results and feasibility model. Power Electron. Drives 2018, 3, 75–83. [Google Scholar] [CrossRef] [Green Version]

- Wu, G.; Ruan, X.; Ye, Z. High Step-Up DC–DC Converter Based on Switched Capacitor and Coupled Inductor. IEEE Trans. Ind. Electron. 2018, 65, 5572–5579. [Google Scholar] [CrossRef]

- Kazimierczuk, M.K.; Czarkowski, D. Resonant Power Converters, 2nd ed.; Wiley: Hoboken, NJ, USA, 2011. [Google Scholar]

| The Concept for Switching Strategy of LCSCVMa | Description—Stages of Charge Transfer in the Converter | |

|---|---|---|

| Strategy C1 |  | 1.Simultaneous charging of all the switched capacitors 2. Discharging of the capacitor that is the nearest to the source (C1) to the internal branch (C2) 3. Charging C1, and discharging C2 and the next SC capacitor (C3) to the output 4. Discharging C1 to the internal branch (as in 2) 5. Discharging C2 and C3 to the output |

| Strategy C2 |  | 1. Simultaneous charging of all the switched capacitors 2. Discharging C1 to the internal branch (C2) 3. Discharging C2 and C3 to the output |

| Strategy C3 |  | 1. Simultaneous charging of all the switched capacitors (C1 and C3) 2. Simultaneous discharging of all the switched capacitors and charging the internal branch capacitor (C2) |

| The Concept for Switching Strategy of LCSCVMb | Description—Stages of Charge Transfer in the Converter | |

|---|---|---|

| Strategy C4 |  | Similarly to strategy C2 for the LCSCVMa, strategy C4 gives the following characteristic in the LCSCVMb: 1. Simultaneous charging of all the switched capacitors 2. Discharging C1 to the internal branch (C2) 3. Discharging C2 and C3 to the output |

| Strategy C5 |  | Similarly to strategy C3 for the LCSCVMa, strategy C5 gives the following characteristic in the LCSCVMb: 1. Simultaneous charging of all the switched capacitors 2. Simultaneous discharging of all the switched capacitors and charging the internal branch (C2) |

| Parameter | LCSCVMa Strategy | LCSCVMb Strategy | SCVM | |||

|---|---|---|---|---|---|---|

| C1 | C2 | C3 | C4 | C5 | ||

| No. of switches | 4 | 4 | 4 | 3 | 3 | 6 |

| No. of diodes | 4 | 4 | 4 | 5 | 5 | 4 |

| Uout, V | 178.0 | 177.0 | 185.0 | 172.1 | 181.4 | 191.2 |

| TS, μs | 21.0 | 12.6 | 8.4 | 12.6 | 8.4 | 8.4 |

| fac_in, kHz | 47.6 | 79.4 | 238.1 | 79.4 | 238.1 | 238.1 |

| fac_out, kHz | 47.6 | 79.4 | 119.0 | 79.4 | 119.0 | 119.0 |

| UC1p-p, V | 21.02 | 19.41 | 12.4 | 19.8 | 12.6 | 5.98 |

| UC2p-p, V | 21.61 | 19.41 | 6.54 | 19.8 | 6.65 | 5.98 |

| UC3p-p, V | 16.08 | 9.7 | 6.18 | 9.92 | 6.29 | 5.98 |

| IL1_rms, A | 6.75 | 7.25 | 5.65 | 7.41 | 5.75 | 2.73 |

| IL2_rms, A | 6.22 | 6.28 | 2.92 | 6.42 | 2.97 | 2.73 |

| IL3_rms, A | 4.11 | 3.63 | 2.75 | 3.71 | 2.80 | 2.73 |

| IL1_max, A | 16.1 | 14.8 | 9.46 | 15.1 | 9.60 | 4.57 |

| IL2_ max, A | 13.2 | 14.8 | 5.01 | 15.2 | 5.09 | 4.57 |

| IL3_ max, A | 12.3 | 7.43 | 4.74 | 7.56 | 4.80 | 4.57 |

| Symmetry of current iL1 | no | yes | yes | yes | yes | yes |

| Symmetry of current iL2 | no | no | yes | no | yes | yes |

| Symmetry of current iL3 | no | yes | yes | yes | yes | yes |

| Parameter | Toplogy | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| Gain | LCSCVMa | LCSCVMb | Ref. [13] | Ref. [22] | Ref. [16] | Ref. [25] | Ref. [26] | Ref. [27] | |

| No. of switches(and diodes) | 4 | 4 (4) | 3 (5) | 6 (4) | 8 (0) | - | 8 (0) | 4 (4) | 4 (6) |

| 7 | - | - | 12 (7) | 14 (0) | 7 (5) | - | - | 7 (12) | |

| 8 | 6 (6) | 4 (7) | 14 (8) | 16 (0) | - | 12 (0) | 6 (6) | 8 (14) | |

| fiin_min/fSmax for all gains(fSmax—in (1)) | 1 | 1 | 0.5 | 1 | 1/4 | 1 | 1 | 0.5 | |

| Parameter | Value | The Laboratory Setup |

|---|---|---|

| Input voltage | 50 V |  |

| Output load | 200 W | |

| Switching frequency | 133 kHz | |

| Resonant capacitors | 1.5 µF (KEMET R76 series) | |

| Resonant inductances | Planar chokes: L = 500 nH, RESR = 18 mΩ @ 100 kHz | |

| Transistors | IKB15N65EH5 (VDS = 650 V, VCE = 1.65 V) as S1 IPB50R140CP (VDS = 550 V, RDSon = 0.14 Ω) as S2 and S4 | |

| Diodes | STTH30L06G (IF = 30 A, VF = 1.0 V, VRRM = 600 V) | |

| PCB | 2 layers, 35 µm | |

| Laboratory equipment | Digital scope: Tektronix MDO3104, current probes: Tektronix TCP0030 150 MHz (input current measurement), Rogowsky coil (switch current measurements) voltage probes: Tektronix THDP0200 200 MHz, Tektronix P5205 100 MHz, power analyzer: Yokogawa WT 1801 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Stala, R.; Waradzyn, Z.; Folmer, S. DC-DC High-Voltage-Gain Converters with Low Count of Switches and Common Ground. Energies 2020, 13, 5657. https://doi.org/10.3390/en13215657

Stala R, Waradzyn Z, Folmer S. DC-DC High-Voltage-Gain Converters with Low Count of Switches and Common Ground. Energies. 2020; 13(21):5657. https://doi.org/10.3390/en13215657

Chicago/Turabian StyleStala, Robert, Zbigniew Waradzyn, and Szymon Folmer. 2020. "DC-DC High-Voltage-Gain Converters with Low Count of Switches and Common Ground" Energies 13, no. 21: 5657. https://doi.org/10.3390/en13215657