Design and Implementation of a Low-Power Low-Cost Digital Current-Sink Electronic Load ‡

Abstract

:1. Introduction and Objectives

- Constant current-sink. This method can test the static performance of the power supply systems, such as power level and dc output impedance.

- Pulsed/step current-sink. This test mode, UUT output voltage response is tested under step load current; the dynamic performance of the power supply systems can be evaluated by examining the voltage response.

- Programmed current-sink. Programmed current sink can test the performance of the power supply under nonlinear load excitation. This test mode is of increasing demand as the grid-tie inverters become more prevalent and introduce disturbances back into the dc systems.

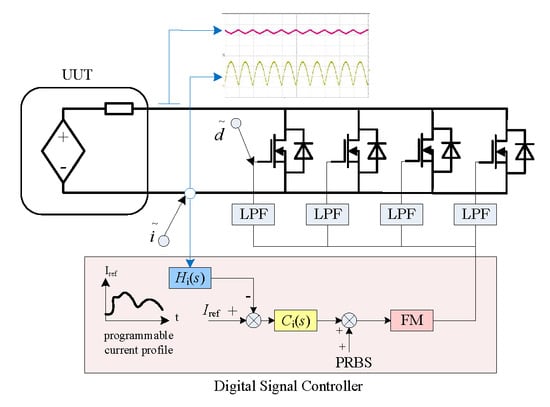

2. Digital Electronic Load System Design

2.1. System Structure

2.2. Power Devices and Drivers

2.3. Sensing and Conditioning

2.4. Model Identification and Control Loop Design

3. Experimental Results and Analysis

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Emadi, A. Modeling of power electronic loads in ac distribution systems using the generalized state-space averaging method. IEEE Trans. Ind. Electron. 2004, 51, 992–1000. [Google Scholar] [CrossRef]

- Ramirez, J.; Torres, E. An electronic load controller for the self-excited induction generator. IEEE Trans. Energy Convers. 2007, 22, 546–548. [Google Scholar] [CrossRef]

- Singh, B.; Rajagopal, V. Neural-network-based integrated electronic load controller for isolated asynchronous generators in small hydro generation. IEEE Trans. Ind. Electron. 2011, 58, 4264–4274. [Google Scholar] [CrossRef]

- Shamsi, P.; Fahimi, B. Dynamic behavior of multiport power electronic interface under source/load disturbances. IEEE Trans. Ind. Electron. 2013, 60, 4500–4511. [Google Scholar] [CrossRef]

- Rao, Y.S.; Chandorkar, M.C. Real-time electrical load emulator using optimal feedback control technique. IEEE Trans. Ind. Electron. 2010, 57, 1217–1225. [Google Scholar]

- Grubic, S.; Amlang, B.; Schumacher, W.; Wenzel, A. A high-performance electronic hardware-in-the-loop drive cload simulation using a linear inverter (linverter). IEEE Trans. Ind. Electron. 2010, 57, 1208–1216. [Google Scholar] [CrossRef]

- Jiang, W.; Wang, S.; Kan, S.; Xie, L.; Hashimoto, S. Digitally controlled multi-phase electronic current sink. In Proceedings of the 2013 IEEE 10th International Conference on Power Electronics and Drive Systems (PEDS), Kitakyushu, Japan, 22–25 April 2013; pp. 862–866. [Google Scholar]

- Kazerani, M. A high-performance controllable dc load. In Proceedings of the IEEE International Symposium on Industrial Electronics, Vigo, Spain, 4–7 June 2007; pp. 1015–1020. [Google Scholar]

- Zhang, R.; Zhang, Z.; Chen, J. Analysis and design of repetitive controlled power electronic load simulator with high dynamic performance. In Proceedings of the IEEE 6th International Power Electronics and Motion Control Conference, Wuhan, China, 17–20 May 2009; pp. 2603–2607. [Google Scholar]

- Rosas-Caro, J.; Peng, F.Z.; Cha, H.; Rogers, C. Z-source-converter-based energy-recycling zero-voltage electronic loads. IEEE Trans. Ind. Electron. 2009, 56, 4894–4902. [Google Scholar] [CrossRef]

- Borrell, A.; Castilla, M.; Miret, J.; Matas, J.; de Vicuna, L.G. Control design for multiphase synchronous buck converters based on exact constant resistive output impedance. IEEE Trans. Ind. Electron. 2013, 60, 4920–4929. [Google Scholar] [CrossRef]

- Sattar, A.; Tsukanov, V. Mosfets withstand stress of linearmode operation. Power Electron. Technol. 2007, 34–39. [Google Scholar]

- Mishra, S.; Ngo, K.D.T. Dynamic characterization of the synthetic ripple modulator in a tightly regulated distributed power application. IEEE Trans. Ind. Electron. 2009, 56, 1164–1173. [Google Scholar] [CrossRef]

- Upadhyay, S.; Mishra, S.; Joshi, A. A wide bandwidth electronic load. IEEE Trans. Ind. Electron. 2012, 59, 733–739. [Google Scholar] [CrossRef]

- Franklin, G.F.; Powell, J.D.; Emami-Naeini, A. Feedback Control of Dynamic Systems, 5th ed.; Pearson Education: London, UK, 2006. [Google Scholar]

- Ljung, L. System Identification-Theory for the User, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 1999. [Google Scholar]

| K | ξn | ξd | ωn | ωd |

|---|---|---|---|---|

| 0.56 | 0.4 | 0.22 | 1.1 × 106 | 1.8 × 105 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, W.; Wang, J.; Wang, Q.; Xu, S.; Hashimoto, S.; Liu, Z. Design and Implementation of a Low-Power Low-Cost Digital Current-Sink Electronic Load ‡. Energies 2019, 12, 2611. https://doi.org/10.3390/en12132611

Jiang W, Wang J, Wang Q, Xu S, Hashimoto S, Liu Z. Design and Implementation of a Low-Power Low-Cost Digital Current-Sink Electronic Load ‡. Energies. 2019; 12(13):2611. https://doi.org/10.3390/en12132611

Chicago/Turabian StyleJiang, Wei, Jieyun Wang, Qianlong Wang, Song Xu, Seiji Hashimoto, and Zhong Liu. 2019. "Design and Implementation of a Low-Power Low-Cost Digital Current-Sink Electronic Load ‡" Energies 12, no. 13: 2611. https://doi.org/10.3390/en12132611