A Topology Synthetization Method for Single-Phase, Full-Bridge, Transformerless Inverter with Leakage Current Suppression—Part II

Abstract

:1. Introduction

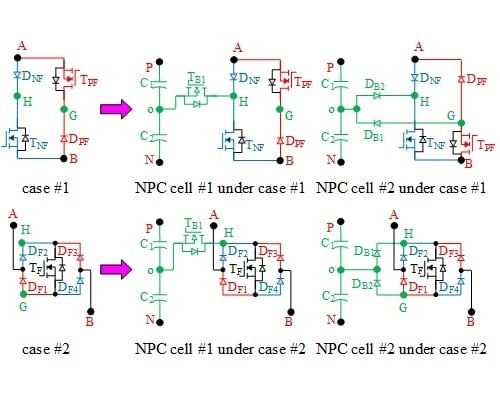

2. NPC Cells for USPWM

- Rule #1:

- To reduce the number of switches in NPC cell, both TPF and TNF are turned on in freewheeling mode, including in PF and NF modes.

- Rule #2:

- Additional switches are added and connected to the freewheeling branch so that point A or B is clamped to point O.

3. Inverter Topologies Based on the Indirect Connection of NPC Cell from USPWM

3.1. Indirect Connection NPC Cell Based on Two Topology Familes

3.2. M = 2, N = 2

3.3. M = 2, N = 3 or M = 3, N = 2

3.4. M = 3, N = 3

3.5. M = 3, N = 4 or M = 4, N = 3

3.6. M = 4, N = 4

4. Inverter Topologies Based on the Direct Connection NPC Cell from USPWM

4.1. Direct Connection NPC Cell Based on Two Topology Families

4.2. M = 2, N = 2

4.3. M = 2, N = 3 or M = 3, N = 2

4.4. M = 3, N = 3

4.5. M = 3, N = 4 or M = 4, N = 3

4.6. M = 4, N = 4

5. Two Types of NPC Cells and Reflected Topologies under DFUSPWM

5.1. Principle of Indirect Connection NPC Cell and Reflected Topologies under DFUSPWM

5.2. Principle of the Direct Connection NPC Cell and Reflected Topology under DFUSPWM

6. Simulation Results

6.1. H6 Topology Without/With Direct Connection NPC Cell under USPWM

6.2. H8 Topology Without/With Indirect Connection NPC Cell under DFUSPWM

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Sun, K.; Zhang, L.; Xing, Y.; Guerrero, J.M. A Distributed Control Strategy Based on DC Bus Signaling for Modular Photovoltaic Generation Systems With Battery Energy Storage. IEEE Trans. Power Electron. 2011, 26, 3032–3045. [Google Scholar] [CrossRef] [Green Version]

- EPIA. Global Market Outlook for Photovoltaics 2013–2017; European Photovoltaic Industry Association: Brussels, Belgium, 2013. [Google Scholar]

- Kjaer, S.B.; Pedersen, J.K.; Blaabjerg, F. A review of single-phase grid-connected inverters for photovoltaic modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Zhe, C.; Kjaer, S.B. Power electronics as efficient interface in dispersed power generation systems. IEEE Trans. Power Electron. 2004, 19, 1184–1194. [Google Scholar] [CrossRef]

- Quan, L.; Wolfs, P. A Review of the Single Phase Photovoltaic Module Integrated Converter Topologies With Three Different DC Link Configurations. IEEE Trans. Power Electron. 2008, 23, 1320–1333. [Google Scholar] [CrossRef] [Green Version]

- Power Generation Systems Connected to the Low-Voltage Distribution Network, VDE-AR-N 4105. Available online: https://www.sogou.com/link?url=hedJjaC291MdqKRdyYP6xaEfyF6gLPTmC2Ly98cd-IVBavtdX5bT4M0N-aB7Vy-zp32izvdhNQ_l-ZZN6CSHZQ (accessed on 1 August 2011).

- Standard for Inverters, Converters, Controllers, and Interconnection System Equipment for Use With Distributed Energy Resources. Available online: https://standardscatalog.ul.com/standards/en/standard_1741_2 (accessed on 28 January 2010).

- Automatic Disconnection Device Between a Generator and the Public Low-Voltage Grid, DIN VDE V 0126-1-1. Available online: https://www.beuth.de/en/pre-standard/din-vde-v-0126-1-1/187485608 (accessed on 1 August 2013).

- Gonzalez, R.; Gubia, E.; Lopez, J.; Marroyo, L. Transformerless Single-Phase Multilevel-Based Photovoltaic Inverter. IEEE Trans. Ind. Electron. 2008, 55, 2694–2702. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S. Transformerless Split-Inductor Neutral Point Clamped Three-Level PV Grid-Connected Inverter. IEEE Trans. Power Electron. 2012, 27, 1799–1808. [Google Scholar] [CrossRef]

- Victor, M.; Greizer, K.; Bremicker, A. Method of Converting a Direct Current Voltage from a Source of direct Current Voltage, More Specifically from a Photovotatic Source of Direct Current Voltage, into a Alternating Current Voltage. U.S. Patent 7411802B2, 12 August 2008. [Google Scholar]

- Schmidt, H.; Siedle, C.; Ketterer, J. Inverter for Converting an Electric Direct Current into an Alternating Current or an Alternating Voltage. European Patent EP2 086 102 A2, 5 August 2009. [Google Scholar]

- Patino, D.G.; Erira, E.G.; Fuelagan, J.R.; Rosero, E.E. Implementation a HERIC inverter prototype connected to the grid controlled by SOGI-FLL. In Proceedings of the 2015 IEEE Workshop on Power Electronics and Power Quality Applications (PEPQA), Bogota, Colombia, 2–4 June 2015; pp. 1–6. [Google Scholar]

- Zhang, L.; Sun, K.; Xing, Y.; Xing, M. H6 Transformerless Full-Bridge PV Grid-Tied Inverters. IEEE Trans. Power Electron. 2014, 29, 1229–1238. [Google Scholar] [CrossRef]

- Yu, W.; Jai, J.-S.; Qian, H.; Hutchens, C.; Zhang, J.; Lisi, G.; Djabbari, A.; Smith, G.; Hegarty, T. High-efficiency inverter with H6-type configuration for photovoltaic non-isolated ac module applications. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1056–1061. [Google Scholar]

- Yang, B.; Li, W.; Gu, Y.; Cui, W.; He, X. Improved Transformerless Inverter With Common-Mode Leakage Current Elimination for a Photovoltaic Grid-Connected Power System. IEEE Trans. Power Electron. 2012, 27, 752–762. [Google Scholar] [CrossRef]

- Su, X.; Sun, Y.; Lin, Y. Analysis on Leakage Current in Transformerless Single-Phase PV Inverters Connected to the Grid. In Proceedings of the 2011 Asia-Pacific Power and Energy Engineering Conference (APPEEC), Wuhan, China, 25–28 March 2011; pp. 1–5. [Google Scholar]

- Xiao, H.F.; Ke, L.; Li, Z. A Quasi-Unipolar SPWM Full-Bridge Transformerless PV Grid-Connected Inverter with Constant Common-Mode Voltage. IEEE Trans. Power Electron. 2015, 30, 3122–3132. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S.; Chen, Y.; Huang, R. An Optimized Transformerless Photovoltaic Grid-Connected Inverter. IEEE Trans. Ind. Electron. 2011, 58, 1887–1895. [Google Scholar] [CrossRef]

- Wang, J.; Ji, B.; Zhao, J.; Yu, J. From H4, H5 to H6 Standardization of full-bridge single phase photovoltaic inverter topologies without ground leakage current issue. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 2419–2425. [Google Scholar]

- Vazquez, G.; Martinez-Rodriguez, P.R.; Sosa, J.M.; Escobar, G.; Juarez, M.A. Transformerless single-phase multilevel inverter for grid tied photovoltaic systems. In Proceedings of the IECON 2014—40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; pp. 1868–1874. [Google Scholar]

- Vazquez, G.; Martinez-Rodriguez, P.R.; Sosa, J.M.; Escobar, G.; Arau, J. A modulation strategy for single-phase HB-CMI to reduce leakage ground current in transformer-less PV applications. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 210–215. [Google Scholar]

- Figueredo, R.S.; de Carvalho, K.C.M.; Ama, N.R.N.; Matakas, L. Leakage current minimization techniques for single-phase transformerless grid-connected PV inverters—An overview. In Proceedings of the 2013 Brazilian Power Electronics Conference (COBEP), Gramado, Brazil, 27–31 October 2013; pp. 517–524. [Google Scholar]

- Hu, S.; Cui, W.; Li, W.; He, X.; Cao, F. A high-efficiency single-phase inverter for transformerless photovoltaic grid-connection. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 4232–4236. [Google Scholar]

- Salmon, J.; Knight, A.; Ewanchuk, J. Single phase multi-level PWM Inverter topologies using coupled inductors. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference (PESC), Rhodes, Greece, 15–19 June 2008; pp. 802–808. [Google Scholar]

- Ozkan, Z.; Hava, A.M. Leakage current analysis of grid connected transformerless solar inverters with zero vector isolation. In Proceedings of the 2011 IEEE Energy Conversion Congress and Exposition (ECCE), Phoenix, AZ, USA, 17–22 September 2011; pp. 2460–2466. [Google Scholar]

- Lopez, O.; Teodorescu, R.; Freijedo, F.; DovalGandoy, J. Leakage current evaluation of a singlephase transformerless PV inverter connected to the grid. In Proceedings of the APEC 2007—Twenty Second Annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 25 February–1 March 2007; pp. 907–912. [Google Scholar]

- Ma, L.; Tang, F.; Zhou, F.; Jin, X.; Tong, Y. Leakage current analysis of a single-phase transformer-less PV inverter connected to the grid. In Proceedings of the 2008 IEEE International Conference on Sustainable Energy Technologies (ICSET), Singapore, 24–27 November 2008; pp. 285–289. [Google Scholar]

- Kerekes, T.; Teodorescu, R.; Rodriguez, P.; Vazquez, G.; Aldabas, E. A New High-Efficiency Single-Phase Transformerless PV Inverter Topology. IEEE Trans. Ind. Electron. 2011, 58, 184–191. [Google Scholar] [CrossRef] [Green Version]

- Ji, B.; Wang, J.; Zhao, J. High-Efficiency Single-Phase Transformerless PV H6 Inverter With Hybrid Modulation Method. IEEE Trans. Ind. Electron. 2013, 60, 2104–2115. [Google Scholar] [CrossRef]

- Islam, M.; Mekhilef, S. A new high efficient transformerless inverter for single phase grid-tied photovoltaic system with reactive power control. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 1666–1671. [Google Scholar]

- Islam, M.; Mekhilef, S. High efficiency transformerless MOSFET inverter for grid-tied photovoltaic system. In Proceedings of the 2014 Twenty-Ninth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 16–20 March 2014; pp. 3356–3361. [Google Scholar]

- San, G.; Qi, H.; Wu, J.; Guo, X. A new three-level six-switch topology for transformerless photovoltaic systems. In Proceedings of the 2012 7th International Power Electronics and Motion Control Conference (IPEMC), Harbin, China, 2–5 June 2012; pp. 163–166. [Google Scholar]

- Freddy, T.K.S.; Rahim, N.A.; Wooi-Ping, H.; Che, H.S. Comparison and Analysis of Single-Phase Transformerless Grid-Connected PV Inverters. IEEE Trans. Power Electron. 2014, 29, 5358–5369. [Google Scholar] [CrossRef]

- Du, D.; Hao, R.; Li, H.; Zheng, T.Q. A novel H6 topology and Its modulation strategy for transformerless photovoltaic grid-connected inverters. In Proceedings of the 2014 16th European Conference on Power Electronics and Applications (EPE’14-ECCE Europe), Lappeenranta, Finland, 26–28 August 2014; pp. 1–8. [Google Scholar]

- Dong, D.; Luo, F.; Boroyevich, D.; Mattavelli, P. Leakage Current Reduction in a Single-Phase Bidirectional AC-DC Full-Bridge Inverter. IEEE Trans. Power Electron. 2012, 27, 4281–4291. [Google Scholar] [CrossRef]

- Cui, W.; Yang, B.; Zhao, Y.; Li, W.; He, X. A novel single-phase transformerless grid-connected inverter. In Proceedings of the IECON 2011—37th Annual Conference on IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; pp. 1126–1130. [Google Scholar]

- Gu, B.; Dominic, J.; Lai, J.-S.; Chen, C.-L.; LaBella, T.; Chen, B. High Reliability and Efficiency Single-Phase Transformerless Inverter for Grid-Connected Photovoltaic Systems. IEEE Trans. Power Electron. 2013, 28, 2235–2245. [Google Scholar] [CrossRef]

- Gu, B.; Dominic, J.; Chen, B.; Lai, J.-S. A high-efficiency single-phase bidirectional AC-DC converter with miniminized common mode voltages for battery energy storage systems. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition (ECCE), Denver, CO, USA, 15–19 September 2013; pp. 5145–5149. [Google Scholar]

- Basu, K.; Mohan, N. A High-Frequency Link Single-Stage PWM Inverter With Common-Mode Voltage Suppression and Source-Based Commutation of Leakage Energy. IEEE Trans. Power Electron. 2014, 29, 3907–3918. [Google Scholar] [CrossRef]

- Barater, D.; Buticchi, G.; Crinto, A.S.; Franceschini, G.; Lorenzani, E. Unipolar PWM Strategy for Transformerless PV Grid-Connected Converters. IEEE Trans. Energy Convers. 2012, 27, 835–843. [Google Scholar] [CrossRef]

- Barater, D.; Buticchi, G.; Crinto, A.S.; Franceschini, G.; Lorenzani, E. A new proposal for ground leakage current reduction in transformerless grid-connected converters for photovoltaic plants. In Proceedings of the 2009 35th Annual Conference of IEEE Industrial Electronics (IECON’09), Porto, Portugal, 3–5 November 2009; pp. 4531–4536. [Google Scholar]

- Islam, M.; Afrin, N.; Mekhilef, S. Efficient single phase transformerless inverter for grid-tied PVG system with reactive power control. IEEE Trans. Sustain. Energy 2016, 7, 1205–1215. [Google Scholar] [CrossRef]

- Islam, M.; Mekhilef, S. H6-type transformerless single-phase inverter for grid-tied photovoltaic system. IET Power Electron. 2015, 8, 636–644. [Google Scholar] [CrossRef] [Green Version]

- Anandababu, C.; Fernandes, B.G. Improved full-bridge neutral point clamped transformerless inverter for photovoltaic grid-connected system. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 7996–8001. [Google Scholar]

- Anandababu, C.; Fernandes, B.G. A novel neutral point clamped transformerless inverter for grid-connected photovoltaic system. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 6962–6967. [Google Scholar]

- Zhang, L.; Sun, K.; Feng, L.; Wu, H.; Xing, Y. A Family of Neutral Point Clamped Full-Bridge Topologies for Transformerless Photovoltaic Grid-Tied Inverters. IEEE Trans. Power Electron. 2013, 28, 730–739. [Google Scholar] [CrossRef]

- Duan, S.; Liu, B.; Kang, Y. A Single-phase Hybrid-Bridge Three-Level Inverter. Chinese Patent ZL200910063079.1, 14 September 2011. [Google Scholar]

- Gonzalez, R.; Lopez, J.; Sanchis, P.; Marroyo, L. Transformerless Inverter for Single-Phase Photovoltaic Systems. IEEE Trans. Power Electron. 2007, 22, 693–697. [Google Scholar] [CrossRef]

- Li, W.; Gu, Y.; Luo, H.; Cui, W.; He, X.; Xia, C. Topology Review and Derivation Methodology of Single-Phase Transformerless Photovoltaic Inverters for Leakage Current Suppression. IEEE Trans. Ind. Electron. 2015, 62, 4537–4551. [Google Scholar] [CrossRef]

- Zhou, L.; Gao, F.; Yang, T. Neutral-point-clamped circuits of single-phase PV inverters: Generalized principle and implementation. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 442–449. [Google Scholar]

- Islam, M.; Mekhilef, S. Efficient transformerless MOSFET inverter for a grid-tied photovoltaic system. IEEE Trans. Power Electron. 2016, 31, 6305–6316. [Google Scholar] [CrossRef]

- Mei, Y.; Hu, S.; Lin, L.; Li, W.; He, X.; Cao, F. Highly efficient and reliable inverter concept-based transformerless photovoltaic inverters with tri-direction clamping cell for leakage current elimination. IET Power Electron. 2016, 9, 1675–1683. [Google Scholar] [CrossRef]

- Akpınar, E.; Balıkcı, A.; Durbaba, E.; Azizoğlu, B.T. Single-phase transformerless photovoltaic inverter with suppressing resonance in improved H6. IEEE Trans. Power Electron. 2019, 34, 8304–8316. [Google Scholar] [CrossRef]

- Zhou, L.; Gao, F. Low leakage current single-phase PV inverters with universal neutral-point-clamping method. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 410–416. [Google Scholar]

- Wang, H.; Burton, S.; Liu, Y.-F.; Sen, P.C.; Guerrero, J.M. A systematic method to synthesize new transformerless full-bridge grid-tied inverters. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 2760–2766. [Google Scholar]

| (M, N) | X1 + X2 | Y1 + Y2 | Family With Extra Diode | Family Without Extra Diode | ||

|---|---|---|---|---|---|---|

| Without NPC Cell (Part I) | With NPC Cell (Part II) | Without NPC Cell (Part I) | With NPC Cell (Part II) | |||

| (M = 2, N = 2) | 1 + 1 | 1 + 1 | R1, R3 | R1S1-1, R1S1-2, R3S1-1, R3S1-2 | R2 | R2S1 |

| (M = 2, N = 3) or (M = 3, N = 2) | 1 + 2 | 1 + 1 | R4 | R4S1-1, R4S1-2, R4S1-3 | R5 | R5S1 |

| 1 + 1 | 1 + 2 | |||||

| 2 + 1 | 1 + 1 | |||||

| 1 + 1 | 2 + 1 | |||||

| (M = 3, N = 3) | 2 + 1 | 2 + 1 | R6 | R6S1 | R7 | R7S1 |

| 1 + 2 | 1 + 2 | |||||

| 2 + 1 | 1 + 2 | R8 | R8S1-1, R8S1-2 | None available | None available | |

| 1 + 2 | 2 + 1 | |||||

| (M = 3, N = 4) or (M = 4, N = 3) | 1 + 2 | 2 + 2 | R9 | R9S1-1, R9S1-2 | R10 | R10S1 |

| 2 + 2 | 1 + 2 | |||||

| 2 + 1 | 2 + 2 | |||||

| 2 + 2 | 2 + 1 | |||||

| (M = 4, N = 4) | 2 + 2 | 2 + 2 | R11, R12 | R11S1-1, R11S1-2, R12S1-1, R12S1-2 | R13 | R13S1-1, R13S1-2 |

| (M, N) | X1 + X2 | Y1 + Y2 | Family With Extra Diode | Family Without Extra Diode | ||

|---|---|---|---|---|---|---|

| Without NPC Cell (Part I) | With NPC Cell (Part II) | Without NPC Cell (Part I) | With NPC Cell (Part II) | |||

| (M = 2, N = 2) | 1 + 1 | 1 + 1 | R1, R3 | R1S2, R3S2 | R2 | R2S2-1, R2S2-2 |

| (M = 2, N = 3) or (M = 3, N = 2) | 1 + 2 | 1 + 1 | R4 | R4S2 | R5 | R5S2-1, R5S2-2 |

| 1 + 1 | 1 + 2 | |||||

| 2 + 1 | 1 + 1 | |||||

| 1 + 1 | 2 + 1 | |||||

| (M = 3, N = 3) | 2 + 1 | 2 + 1 | R6 | R6S2 | R7 | R7S2-1, R7S2-2 |

| 1 + 2 | 1 + 2 | |||||

| 2 + 1 | 1 + 2 | R8 | R8S2 | None available | R8S2 | |

| 1 + 2 | 2 + 1 | |||||

| (M = 3, N = 4) or (M = 4, N = 3) | 1 + 2 | 2 + 2 | R9 | R9S2 | R10 | R10S2 |

| 2 + 2 | 1 + 2 | |||||

| 2 + 1 | 2 + 2 | |||||

| 2 + 2 | 2 + 1 | |||||

| (M = 4, N = 4) | 2 + 2 | 2 + 2 | R11, R12 | R11S2, R12S2 | R13 | R13S2 |

| (M, N) | X1 + X2 | Y1 + Y2 | Family With Extra Diode | Family Without Extra Diode | ||

|---|---|---|---|---|---|---|

| Without NPC Cell | With NPC Cell | Without NPC Cell | With NPC Cell | |||

| (M = 4, N = 4) | 2 + 2 | 2 + 2 | R11, R12 | R11S1, R12S1 | R13 | R13S1 |

| (M, N) | X1 + X2 | Y1 + Y2 | Family with Extra Diode | Family Without Extra Diode | ||

|---|---|---|---|---|---|---|

| Without NPC Cell | With NPC Cell | Without NPC Cell | With NPC Cell | |||

| (M = 4, N = 4) | 2 + 2 | 2 + 2 | R11, R12 | R11S2, R12S2 | R13 | R13S2 |

| Topology Name | Number of Switches | Number of Diodes | Economic Cost | Topology Name | Number of Switches | Number of Diodes | Economic Cost |

|---|---|---|---|---|---|---|---|

| R1S1-1 | 7 | 2 | 7.6 | R10S1 | 8 | 3 | 8.9 |

| R1S1-2 | 6 | 4 | 7.2 | R13S1-1 | 7 | 0 | 7 |

| R3S1-1 | 6 | 4 | 7.2 | R13S1-2 | 6 | 2 | 6.6 |

| R3S1-2 | 5 | 6 | 6.8 | R1S2 | 8 | 4 | 9.2 |

| R4S1-1 | 7 | 2 | 7.6 | R3S2 | 6 | 4 | 7.2 |

| R4S1-2 | 7 | 2 | 7.6 | R4S2 | 8 | 4 | 9.2 |

| R4S1-3 | 6 | 4 | 7.2 | R6S2 | 8 | 4 | 9.2 |

| R6S1 | 7 | 2 | 7.6 | R8S2 | 8 | 4 | 9.2 |

| R8S1-1 | 7 | 2 | 7.6 | R9S2 | 10 | 6 | 11.8 |

| R8S1-2 | 6 | 4 | 7.2 | R11S2 | 12 | 8 | 14.4 |

| R9S1-1 | 8 | 3 | 8.9 | R12S2 | 12 | 4 | 13.2 |

| R9S1-2 | 7 | 5 | 8.5 | R2S2-1 | 8 | 0 | 8 |

| R11S1-1 | 9 | 4 | 10.2 | R2S2-2 | 7 | 2 | 7.6 |

| R11S1-2 | 8 | 6 | 9.8 | R5S2-1 | 8 | 0 | 8 |

| R12S1-1 | 8 | 2 | 8.6 | R5S2-2 | 8 | 2 | 8.6 |

| R12S1-2 | 7 | 4 | 8.2 | R7S2-1 | 8 | 0 | 8 |

| R2S1 | 7 | 0 | 7 | R7S2-2 | 7 | 2 | 7.6 |

| R5S1 | 7 | 0 | 7 | R10S2 | 10 | 2 | 10.6 |

| R7S1 | 6 | 0 | 6 | R13S2 | 12 | 0 | 12 |

| Connection Mode of NPC Cell | Topologies Name | Number of Switches | Number of Diodes | Economic Cost |

|---|---|---|---|---|

| Indirect Connection | R11S1 | 8 | 8 | 10.4 |

| R12S1 | 8 | 2 | 8.6 | |

| R13S1 | 6 | 2 | 6.6 | |

| Direct Connection | R11S2 | 12 | 4 | 13.2 |

| R12S2 | 10 | 2 | 10.6 | |

| R13S2 | 9 | 0 | 9 |

| Parameter | Value |

|---|---|

| Rated power | 3000 W |

| Input voltage | 400 V |

| Grid voltage/frequency | 220 V/50 Hz |

| Filter inductor L1, L2 | 1 mH |

| Switching frequency | 20 kHz |

| DC-bus Capacitor Cdc1, Cdc2 | 470 µF |

| Junction capacitor of each switch | 100 pF |

| PV parasitic capacitor CPV1, CPV2 | 0.1 µH |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yue, X.; Wang, H.; Zhu, X.; Wei, X.; Liu, Y.-F. A Topology Synthetization Method for Single-Phase, Full-Bridge, Transformerless Inverter with Leakage Current Suppression—Part II. Energies 2020, 13, 446. https://doi.org/10.3390/en13020446

Yue X, Wang H, Zhu X, Wei X, Liu Y-F. A Topology Synthetization Method for Single-Phase, Full-Bridge, Transformerless Inverter with Leakage Current Suppression—Part II. Energies. 2020; 13(2):446. https://doi.org/10.3390/en13020446

Chicago/Turabian StyleYue, Xiumei, Hongliang Wang, Xiaonan Zhu, Xinwei Wei, and Yan-Fei Liu. 2020. "A Topology Synthetization Method for Single-Phase, Full-Bridge, Transformerless Inverter with Leakage Current Suppression—Part II" Energies 13, no. 2: 446. https://doi.org/10.3390/en13020446