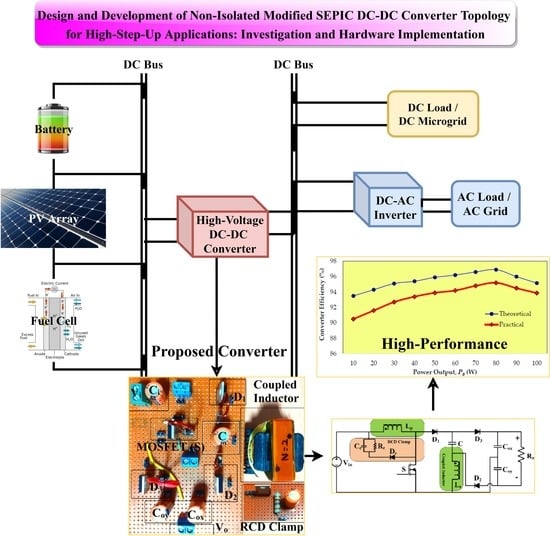

Design and Development of Non-Isolated Modified SEPIC DC-DC Converter Topology for High-Step-Up Applications: Investigation and Hardware Implementation

Abstract

:1. Introduction

- The converter is basically derived from the traditional SEPIC converter with an additional diode to increase the voltage gain of the converter.

- The converter is provided with the traditional RCD clamp circuit to reduce the voltage stress of the MOSFET switch.

- Performance comparison and design guidelines of the proposed converter is discussed in detail.

- The mathematical equations of the output voltage under ideal and practical conditions are discussed for better insight.

- Finally, the circuit structure with an active clamp circuit is also proposed in this paper as a future extension.

2. System Configuration

2.1. CCM Operation

2.2. DCM Operation

3. Steady-State Analysis of the Proposed Converter

Voltage Stress and Current Stress of MOSFET and Diodes

4. Design Guidelines and Performance Comparison of the Proposed Converter

4.1. Design Guidelines

4.2. Performance Comparisons

4.3. Efficiency and Power Loss Analysis

5. Results and Further Discussion

5.1. Simulation Results

5.2. Hardware Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Premkumar, M.; Kumar, C.; Sowmya, R. Analysis and implementation of high-performance DC-DC step-up converter for multilevel boost structure. Front. Energy Res. 2019, 7, 149. [Google Scholar] [CrossRef] [Green Version]

- Premkumar, M.; Kumar, C.; Anbarasan, A.; Sowmya, R. A novel non-isolated high step-up DC-DC boost converter using single switch for renewable energy systems. Electr. Eng. 2020, 102, 811–829. [Google Scholar] [CrossRef]

- Premkumar, M.; Subramaniam, U.; Babu, T.S.; Elavarasan, R.M.; Mihet-Popa, L. Evaluation of mathematical model to characterize the performance of conventional and hybrid PV array topologies under static and dynamic shading patterns. Energies 2020, 13, 3216. [Google Scholar] [CrossRef]

- Gules, R.; Dos Santos, W.M.; Dos Reis, F.A.; Romaneli, E.F.R.; Badin, A.A. A modified SEPIC converter with high static gain for renewable applications. IEEE Trans. Power Electron. 2014, 29, 5860–5871. [Google Scholar] [CrossRef]

- Madurai Elavarasan, R.; Ghosh, A.; Mallick, T.K.; Krishnamurthy, A.; Saravanan, M. Investigations on performance enhancement measures of the bidirectional converter in PV—wind interconnected microgrid system. Energies 2019, 12, 2672. [Google Scholar] [CrossRef] [Green Version]

- Maroti, P.K.; Padmanaban, S.; Holm-Nielsen, J.B.; Pecht, M.; Ojo, O. A novel configuration of modified Cuk converter using multiple VLSI modules for high voltage renewable energy application. In Proceedings of the 45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019; pp. 4083–4088. [Google Scholar]

- Maroti, P.K.; Bhaskar, M.S.; Padmanaban, S.; Holm-Nielsen, J.B.; Sutikno, T.; Iqbal, A. A new multilevel member of modified Cuk converter family for renewable energy applications. In Proceedings of the IEEE Conference on Energy Conversion, Yogyakarta, Indonesia, 16–17 October 2019; pp. 224–229. [Google Scholar]

- Shokati, A.E.; Sabahi, M. Bidirectional quasi-Cuk dc/dc converter with reduced voltage stress on capacitor and capability of changing the output polarity. J. Electr. Eng. Technol. 2017, 12, 1108–1113. [Google Scholar]

- Narula, S.; Singh, B.; Bhuvaneswari, G. Power factor corrected welding power supply using modified zeta converter. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 617–625. [Google Scholar] [CrossRef]

- Maroti, P.K.; Padamanaban, S.; Bhaskar, S.M.; Holm–Nielsen, J.B.; Blaabjerg, F.; Lonel, D.M.; He, J.B. A non-isolated inverting high gain modified new series of landsman converter. In Proceedings of the 45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019; pp. 4077–4082. [Google Scholar]

- Ajami, A.; Ardi, H.; Farakhor, A. A novel high step-up DC/DC converter based on integrating coupled inductor and switched-capacitor techniques for renewable energy applications. IEEE Trans. Power Electron. 2015, 30, 4255–4263. [Google Scholar] [CrossRef]

- Wai, R.J.; Jheng, K.H. High-efficiency single-input multiple-output dc-dc converter. IEEE Trans. Power Electron. 2013, 28, 886–898. [Google Scholar] [CrossRef]

- Zhao, Q.; Lee, F.C. High-efficiency, high step-up dc-dc converters. IEEE Trans. Power Electron. 2003, 18, 65–73. [Google Scholar] [CrossRef] [Green Version]

- Shahir, M.; Babaei, E.; Farsadi, M. Analysis and design of voltage-lift technique-based non-isolated boost dc-dc converter. IET Power Electron. 2018, 11, 1083–1091. [Google Scholar] [CrossRef]

- Zhou, M.; Yang, M.; Wu, X.; Fu, J. Research on composite control strategy of quasi-z-source dc-dc converter for fuel cell vehicles. Appl. Sci. 2019, 9, 3309. [Google Scholar] [CrossRef] [Green Version]

- Schmitz, L.; Martins, D.C.; Coelho, R.F. High step-up non-isolated ZVS/ZCS DC-DC converter for photovoltaic thin-film module applications. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 565–575. [Google Scholar] [CrossRef]

- Ting, N.S.; Sahin, Y.; Aksoy, I. Analysis, design, and implementation of a zero-voltage-transition interleaved boost converter. J. Power Electron. 2017, 17, 41–55. [Google Scholar] [CrossRef] [Green Version]

- Harchegani, A.T.; Mahdavi, M. A new soft-switching dual input converter for renewable energy systems. J. Power Electron. 2017, 17, 1127–1136. [Google Scholar]

- Moradzadeh, M.; Babaei, E.; Zamiri, E.; Hamkari, S. A new high step-up dc/dc converter structure by using coupled inductor with reduced switch-voltage stress. Electr. Power Compon. Syst. 2017, 45, 1705–1719. [Google Scholar] [CrossRef]

- Tang, Y.; Wang, T.; He, Y. A switched-capacitor-based active network converter with high voltage gain. IEEE Trans. Power Electron. 2013, 29, 2959–2968. [Google Scholar] [CrossRef]

- Tran, D.; Chakraborty, S.; Lan, Y.; Van Mierlo, Y.; Hegazy, O. Optimized multiport dc/dc converter for vehicle drivetrains: Topology and design optimization. Appl. Sci. 2018, 8, 1351. [Google Scholar] [CrossRef] [Green Version]

- Gao, W.; Zhang, Y.; Lv, X.; Lou, Q. Non-isolated high-step up soft-switching DC/DC converter with low-voltage stress. IET Power Electron. 2017, 10, 120–128. [Google Scholar] [CrossRef]

- Park, K.B.; Moon, G.W.; Youn, M.J. Non isolated high step-up boost converter integrated with SEPIC converter. IEEE Trans. Power Electron. 2010, 25, 2266–2275. [Google Scholar] [CrossRef]

- Hsieh, Y.P.; Chen, J.F.; Liang, T.J.; Yang, L.S. Novel high step-up dc-dc converter for distributed generation system. IEEE Trans. Ind. Electron. 2013, 60, 1473–1481. [Google Scholar] [CrossRef]

- Premkumar, M.; Karthick, K.; Sowmya, R. A review on solar PV based grid connected microinverter control schemes and topologies. Int. J. Renew. Energy Dev. 2018, 7, 171–182. [Google Scholar] [CrossRef]

- Premkumar, M.; Sumithira, T.R. Design and implementation of new topology for solar PV based transformerless forward microinverter. J. Electr. Eng. Tech. 2019, 14, 145–155. [Google Scholar] [CrossRef]

- Cao, D.; Peng, Z. A family of Z-source and quasi-Z-source DC-DC converters. In Proceedings of the 24th Annual IEEE Applied Power Electronics Conference and Exposition, Washington, DC, USA, 15–19 February 2009; pp. 1097–1101. [Google Scholar]

- Adamowicz, M. Non-isolated resonant quasi-Z-source network DC-DC converter. Electron. Lett. 2019, 55, 855–857. [Google Scholar] [CrossRef]

- Premkumar, M.; Sumithira, T.R. Design and implementation of new topology for non-isolated DC-DC microconverter with effective clamping circuit. J. Circuits Syst. Comput. 2019, 28, 1950082. [Google Scholar] [CrossRef]

- Mohammadzadeh Shahir, F.; Babaei, E.; Farsadi, M. Voltage-lift technique based non-isolated boost dc-dc converter: Analysis and design. IEEE Trans. Power Electron. 2018, 33, 5917–5926. [Google Scholar] [CrossRef]

- Yassera, A.; Mohammad, M. Three topologies of a non-isolated high gain switched-inductor switched-capacitor step-up Cuk converter for renewable energy applications. Electronics 2018, 7, 1–24. [Google Scholar]

- Kumar, A.; Sensarma, P. Ripple-free input current high voltage gain dc-dc converters with coupled inductors. IEEE Trans. Power Electron. 2019, 34, 3418–3428. [Google Scholar] [CrossRef]

- Natarajan, S.; Babu, T.S.; Balasubramanian, K.; Subramaniam, U.; Almakhles, D.J. A State-of-the-art review on conducted electromagnetic interference in non-isolated dc to dc converters. IEEE Access 2020, 8, 2564–2577. [Google Scholar] [CrossRef]

- Natarajan, S.; Padmavathi, P.; Reddy Kalvakurthi, J.; Babu, T.S.; Ramachandaramurthy, V.K.; Sanjeevikumar, P. Conducted electromagnetic interference spectral peak mitigation in LUO-converter using FPGA-based chaotic PWM technique. Electr. Power Compon. Syst. 2019, 47, 838–848. [Google Scholar] [CrossRef]

- Kircioglu, O.; Unlu, M.; Camur, S. Modeling and analysis of DC-DC SEPIC converter with coupled inductors. In Proceedings of the International Symposium on Industrial Electronics, Santa Clara, CA, USA, 8–10 June 2016. [Google Scholar]

- Vinaya Sagar, K.; Kanungo Barada, M.; Aditi, C.; Kishor, T. Modified bridgeless SEPIC rectifier for power factor correction with reduced switch stress operating in continuous conduction mode. J. Circuits Syst. Comput. 2018, 27, 1850127. [Google Scholar]

- Hossein Ajdar, F.B.; Mohamad Reza, B. Enhanced buck-boost dc-dc converter with positive output voltage. J. Circuits Syst. Comput. 2019, 29, 2050072. [Google Scholar]

- Barsana Banu, J.; Balasingh Moses, M.; Rajarajacholan, S. A non-isolated bidirectional DC-DC converter with LCD snubber. Rev. Tec. De La Fac. De Ing. Univ. Del Zulia. 2016, 39, 131–143. [Google Scholar]

- Alenka, H.; Joze, K.; Miro, M. RC-RCD clamp circuit for ringing losses reduction in a flyback converter. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 369–373. [Google Scholar]

- Lo, Y.K.; Liu, Y.C.; Lin, J.Y.; Lin, C.Y.; Cheng, S.J. Analysis and design of an active-clamping zero-voltage-switching isolated inverse-SEPIC converter. Int. J. Circuits Theory Appl. 2010, 40, 287–305. [Google Scholar] [CrossRef]

- Ardi, H.; Ajami, A. Study on a high voltage gain SEPIC-based DC-DC converter with continuous input current for sustainable energy applications. IEEE Trans. Power Electron. 2018, 33, 10403–10409. [Google Scholar] [CrossRef]

- Lee, S.; Do, H. Zero-ripple input-current high-step-up boost–SEPIC DC-DC converter with reduced switch-voltage stress. IEEE Trans. Power Electron. 2017, 32, 6170–6177. [Google Scholar] [CrossRef]

- Moradpour, R.; Ardi, H.; Tavakoli, A. Design and implementation of a new SEPIC-based high step-up dc/dc converter for renewable energy applications. IEEE Trans. Ind. Electron. 2018, 65, 1290–1297. [Google Scholar] [CrossRef]

- Semiconductors. Available online: https://www.mouser.com/Electronic-Components/ (accessed on 25 May 2020).

- Maroti, P.K.; Padmanaban, S.; Holm-Nielsen, J.B.; Sagar Bhaskar, M.; Meraj, M.; Iqbal, A. A new structure of high voltage gain SEPIC converter for renewable energy applications. IEEE Access 2019, 7, 89857–89868. [Google Scholar] [CrossRef]

| S. No. | Parameters | Range |

|---|---|---|

| 1 | Input voltage range, Vin | 20–30 V |

| 2 | Output voltage, Vout | 200 V |

| 3 | Output power, Pout | 100 W |

| 4 | Switching frequency, Fs | 50 kHz |

| 5 | Voltage ripple | <1% |

| 6 | Coupled inductor turns ratio, T | 2 |

| 7 | Inductances, Lm and Llk | 200 µH, 2 µH |

| 8 | Capacitance, C | 10 µF |

| 9 | Capacitance, Cox and Coy | 22 µF |

| 10 | Clamp resistance, Rc | 3.3 kΩ |

| 11 | Clamp capacitance, Cc | 6 nF |

| Ref. | Year | M | Vds | Ids | Input Current Ripple | No. of Components | Ntotal | Rating | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CI | D | C | S | L | ||||||||

| Proposed | - | Low | 1 | 4 | 4 | 1 | - | 10 | 100 | |||

| [1] | 2019 | High | 1 | 1 | 3 | 1 | - | 6 | 60 | |||

| [12] | 2013 | - | Medium | 1 | 4 | 5 | 1 | 1 | 12 | 500 | ||

| [13] | 2003 | - | High | 1 | 2 | 3 | 2 | - | 8 | 36 | ||

| [23] | 2010 | High | 1 | 2 | 4 | 1 | 1 | 9 | 200 | |||

| [24] | 2013 | - | Low | 1 | 5 | 6 | 1 | - | 13 | 150 | ||

| [40] | 2018 | Low | 1 | 5 | 7 | 1 | 1 | 15 | 200 | |||

| [41] | 2017 | - | Medium | 2 | 5 | 6 | 1 | 1 | 14 | 150 | ||

| [42] | 2018 | Low | 1 | 4 | 6 | 1 | 1 | 13 | 100 | |||

| [43] | 2019 | - | Medium | - | 3 | 4 | 1 | 3 | 11 | 100 | ||

| S. No. | Component | Type/Range | Quantity |

|---|---|---|---|

| 1 | MOSFET, S | IRFB4410, 100 V, 96 A, 8 mΩ | 1 |

| 2 | Diode, D1, D2, D3, and Dc | MUR820, 200 V, 8 A | 4 |

| 3 | Capacitors, Cox and Coy | 22 µF, 250 V, Electrolytic type | 2 |

| 4 | Capacitor, C | 10 µF, 250 V, Electrolytic type | 1 |

| 5 | Coupled inductor | Lm = 200 µH, Llk = 2 µH T = 2, EI33 core | 1 |

| 6 | Clamp resistor, Rc | 3.3 kΩ | 1 |

| 7 | Clamp Capacitance, Cc | 6nF, 100 V | 1 |

| 8 | MOSFET driver | TLP250 | 1 |

| Components | rds-on/ESR (Ω) | Forward Voltage Drop (V) | RMS Current (A) | Average Current (A) | Power Loss (W) | |||

|---|---|---|---|---|---|---|---|---|

| Theoretical | Practical | Theoretical | Practical | Theoretical | Practical | |||

| S | 0.008 | - | 4.58 | 4.76 | - | - | 0.1678 | 0.1812 |

| D1 | 0.02 | 0.975 | 1.1 | 1.05 | 1 | 0.96 | 0.999 | 0.9581 |

| D2 | 0.02 | 0.975 | 1.1 | 1.07 | 1 | 0.98 | 0.999 | 0.9783 |

| D3 | 0.02 | 0.975 | 1.1 | 1.13 | 1 | 1.06 | 0.999 | 1.0550 |

| Dc | 0.02 | 0.975 | 0.9 | 0.75 | 0.6 | 0.67 | 0.585 | 0.6532 |

| C | 0.005 | - | 1.85 | 2.15 | - | - | 0.0171 | 0.0231 |

| Cox | 0.005 | - | 0.32 | 0.35 | - | - | 0.0051 | 0.0061 |

| Coy | 0.005 | - | 0.17 | 0.15 | - | - | 0.0014 | 0.0011 |

| Rc | 3300 | 15 | 0.005 | 0.005 | - | - | 0.075 | 0.075 |

| Cc | 0.005 | - | 2.23 | 2.62 | - | - | 0.0241 | 0.034 |

| L1 | 0.051 | - | 4.85 | 5.25 | - | - | 1.1996 | 1.4056 |

| L2 | 0.096 | - | 0.92 | 1.05 | - | - | 0.0812 | 0.1058 |

| Core Loss | - | - | - | - | - | 0 | 1.28 | |

| Total loss | 5.1533 | 6.5753 | ||||||

| Full load conversion efficiency in % | 95.10 | 93.83 | ||||||

| Analysis Type | Vds (V) | Ids (A) | VD1 (V) | VD2 (V) | VD3 (V) | VC (V) | VCox (V) | VCoy (V) | Vout (V) |

|---|---|---|---|---|---|---|---|---|---|

| Theoretical | 50 | 4 | 150 | 100 | 100 | 100 | 150 | 50 | 200 |

| Simulation | 50 | 4.12 | 150 | 100 | 100 | 100 | 150 | 50 | 200 |

| Experiment | 60 | 4.56 | 147 | 102.5 | 104.5 | 98 | 146 | 51 | 197 |

| Component | Quantity | Type for 100 W | Cost in USD * | Type for 1 kW | Cost in USD * |

|---|---|---|---|---|---|

| Switch | 1 | IRFB4410 | 2.19 | IXFB110N60P3 | 17.38 |

| Diodes, D1, D2, D3, Dc | 4 | MUR820 | 5.56 | VS-15EWX06FN-M3 | 8.76 |

| Capacitor, C | 1 | 10 µF, 250 V, Electrolytic | 0.9 | 10 µF, 600 V, Electrolytic | 8.63 |

| Capacitors, Cox and Coy | 2 | 22 µF, 250 V, Electrolytic | 2.08 | 22 µF, 250 V, Electrolytic | 16.56 |

| Clamp capacitor, Cc | 1 | 6 nF, 25 V | 0.69 | 6 nF, 250 V | 3.62 |

| Clamp resistor, Rc | 1 | 3.3 kΩ, 10W | 0.77 | 3.3 kΩ, 25 W | 2.54 |

| Coupled inductor | 1 | T = 2, EI33 Ferrite core (with winding) | 5.02 | T = 2, EE55 Ferrite core (with winding) | 20.45 |

| Driver circuit | 1 | TLP 250 | 2.02 | TLP 250 | 2.02 |

| Overall cost | 19.23 | 79.96 | |||

| Ref. | No. of Components | Cost in USD * | ||||

|---|---|---|---|---|---|---|

| CI | D | C | S | L | ||

| Proposed | 1 | 4 | 4 | 1 | - | 19.23 |

| [1] | 1 | 1 | 3 | 1 | - | 13.68 |

| [12] | 1 | 4 | 5 | 1 | 1 | 25.32 |

| [13] | 1 | 2 | 2 | 1 | 1 | 18.83 |

| [23] | 1 | 2 | 3 | 1 | 1 | 19.68 |

| [24] | 1 | 4 | 5 | 1 | - | 22.69 |

| [40] | 1 | 5 | 7 | 1 | 1 | 28.48 |

| [41] | 2 | 5 | 6 | 1 | 1 | 31.04 |

| [42] | 1 | 4 | 6 | 1 | 1 | 25.69 |

| [43] | - | 3 | 4 | 1 | 3 | 25.18 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Premkumar, M.; Subramaniam, U.; Haes Alhelou, H.; Siano, P. Design and Development of Non-Isolated Modified SEPIC DC-DC Converter Topology for High-Step-Up Applications: Investigation and Hardware Implementation. Energies 2020, 13, 3960. https://doi.org/10.3390/en13153960

Premkumar M, Subramaniam U, Haes Alhelou H, Siano P. Design and Development of Non-Isolated Modified SEPIC DC-DC Converter Topology for High-Step-Up Applications: Investigation and Hardware Implementation. Energies. 2020; 13(15):3960. https://doi.org/10.3390/en13153960

Chicago/Turabian StylePremkumar, Manoharan, Umashankar Subramaniam, Hassan Haes Alhelou, and Pierluigi Siano. 2020. "Design and Development of Non-Isolated Modified SEPIC DC-DC Converter Topology for High-Step-Up Applications: Investigation and Hardware Implementation" Energies 13, no. 15: 3960. https://doi.org/10.3390/en13153960