Analog IC Design—Analog and RF Interface for Electronic Systems

A topical collection in Electronics (ISSN 2079-9292). This collection belongs to the section "Circuit and Signal Processing".

Viewed by 44853Editors

Interests: electronics engineering; analog integrated circuits; CMOS; low-power analog circuits; analog circuit design; analog–digital conversion; energy harvesting; analog in-memory computing; low-power RF receivers; bandgap references

Special Issues, Collections and Topics in MDPI journals

Interests: CMOS; microelectronics; circuit simulation; cadence; analog electronics; circuit analysis; electronics; digital electronics; VHDL programming; electrical and electronics engineering

Topical Collection Information

Dear Colleagues,

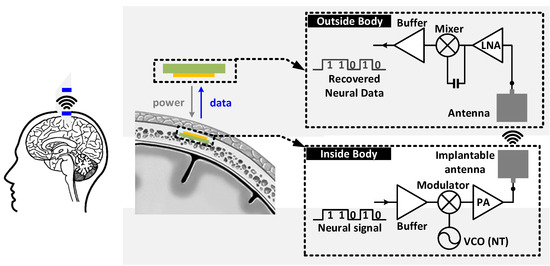

Any analog and RF interface circuit acts as a mandatory bridge between an outer and an inner environment, composed by digital circuits and systems devoted to computing and storage.

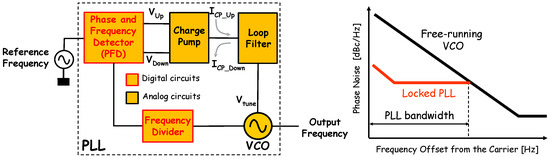

Analog interface circuits are integrated in almost all consumer, industrial, automotive, and medical devices with sensing capability, whereas RF interfaces enable device-to-device connections or connection to a local-area network or the internet. Even if nowadays, radio communication systems are mostly digital, they still need to be interfaced with antennas and, therefore, dedicated circuits such as low-noise amplifiers and RF power amplifiers are mandatory.

Special mention must be made of circuits used to link the analog and digital domains, such as the A/D and D/A converters, which have experienced impressive performance improvements in terms of speed, resolution, silicon area, and power consumption in recent decades. Usually, these interfaces are integrated in dedicated ICs or co-integrated with digital circuits composing mixed-signal systems with increased complexity.

In summary, the digital computation and storage capability embedded in electronic devices are strictly correlated with the world of analog and RF interfaces.

This Special Issue focuses on the analysis, design, and implementation of analog and RF interface circuits, integrated in CMOS or BiCMOS silicon technologies.

Prof. Dr. Andrea Boni

Dr. Michele Caselli

Guest Editors

Manuscript Submission Information

Manuscripts should be submitted online at www.mdpi.com by registering and logging in to this website. Once you are registered, click here to go to the submission form. Manuscripts can be submitted until the deadline. All submissions that pass pre-check are peer-reviewed. Accepted papers will be published continuously in the journal (as soon as accepted) and will be listed together on the collection website. Research articles, review articles as well as short communications are invited. For planned papers, a title and short abstract (about 100 words) can be sent to the Editorial Office for announcement on this website.

Submitted manuscripts should not have been published previously, nor be under consideration for publication elsewhere (except conference proceedings papers). All manuscripts are thoroughly refereed through a single-blind peer-review process. A guide for authors and other relevant information for submission of manuscripts is available on the Instructions for Authors page. Electronics is an international peer-reviewed open access semimonthly journal published by MDPI.

Please visit the Instructions for Authors page before submitting a manuscript. The Article Processing Charge (APC) for publication in this open access journal is 2400 CHF (Swiss Francs). Submitted papers should be well formatted and use good English. Authors may use MDPI's English editing service prior to publication or during author revisions.

Keywords

- A/D and D/A converter

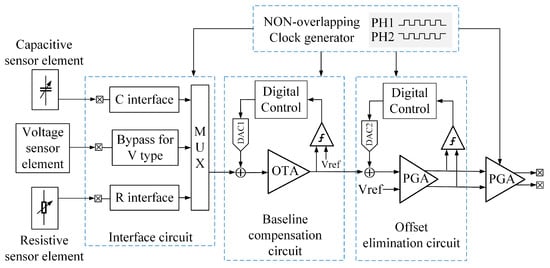

- front-end circuits for sensor interfaces (industrial, biochemical, medical, etc.)

- ultralow-power sensor interfaces for wireless devices

- analog and RF interfaces for IoT devices

- low noise and offset amplifier

- interface circuits for automotive systems

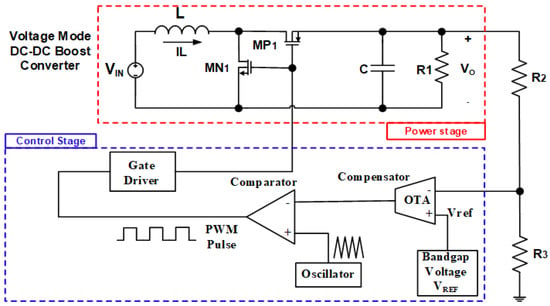

- power amplifiers and drivers

- RF circuits: LNAs and power amplifiers