Article

# Low-Cost Indirect Measurements for Power-Efficient In-Field Optimization of Configurable Analog Front-Ends with Self-X Properties: A Hardware Implementation

Qummar Zaman <sup>1,2</sup>, Senan Alraho <sup>1,3</sup> and Andreas König <sup>1,\*</sup>

- <sup>1</sup> Lehrstuhl Kognitive Integrierte Sensorsysteme (KISE), Fachbereich Elektrotechnik und Informationstechnik, Rheinland-Pfälzische Technische Universität Kaiserslautern-Landau, 67663 Kaiserslautern, Germany; qummar@eit.uni-kl.de (Q.Z.); aube@eit.uni-kl.de (S.A.)

- <sup>2</sup> Department of Electronics Engineering, University of Engineering and Technology Taxila, Taxila 47080, Pakistan

- <sup>3</sup> College of Electronics Engineering, Ninevah University, Ninevah 41002, Iraq

- \* Correspondence: koenig@eit.uni-kl.de

Abstract: This paper presents a practical implementation and measurement results of power-efficient chip performance optimization, utilizing low-cost indirect measurement methods to support self-X properties (self-calibration, self-healing, self-optimization, etc.) for in-field optimization of analog front-end sensory electronics with XFAB 0.35 µm complementary metal oxide semiconductor (CMOS) technology. The reconfigurable, fully differential indirect current-feedback instrumentation amplifier (CFIA) performance is intrinsically optimized by employing a single test sinusoidal signal stimulus and measuring the total harmonic distortion (THD) at the output. To enhance the optimization process, the experience replay particle swarm optimization (ERPSO) algorithm is utilized as an artificial intelligence (AI) agent, implemented at the hardware level, to optimize the performance characteristics of the CFIA. The ERPSO algorithm extends the selection producer capabilities of the classical PSO methodology by incorporating an experience replay buffer to mitigate the likelihood of being trapped in local optima. Furthermore, the CFIA circuit has been integrated with a simple power-monitoring module to assess the power consumption of the optimization solution, to achieve a power-efficient and reliable configuration. The optimized chip performance showed an approximate 34% increase in power efficiency while achieving a targeted THD value of -72 dB, utilizing a 1 Vp-p differential input signal with a frequency of 1 MHz, and consuming approximately 53 mW of power. Preliminary tests conducted on the fabricated chip, using the default configuration pattern extrapolated from post-layout simulations, revealed an unacceptable performance behavior of the CFIA. Nevertheless, the proposed in-field optimization successfully restored the circuit's performance, resulting in a robust design that meets the performance achieved in the design phase.

**Keywords:** analog front-ends; self-X properties; indirect measurements; extrinsic/intrinsic optimization; indirect-current-feedback instrumentation amplifier; metaheuristic optimization algorithm; reconfigurable sensory electronics

## 1. Introduction

The integration of machine learning (ML) and artificial intelligence (AI) with other emerging technologies, such as cloud computing, big data analytics, cyber–physical systems, and industrial internet of things (I(I)oTs), is revolutionizing the industrial sector, commonly known as industry 4.0 [1–4]. The current industry transformation predominantly depends on acquiring, analyzing, and interpreting data from smart sensors and I(I)oTs devices [5]. Consequently, it is crucial to develop accurate and reliable sensors and sensory electronics [6], which are capable of collecting, processing, and transferring data to the primary processing unit [7]. However, the performance and long-term reliability of these

Citation: Zaman, Q.; Alraho, A.; König, A. Low-Cost Indirect Measurements for Power-Efficient In-Field Optimization of Configurable Analog Front-Ends with Self-X Properties: A Hardware Implementation. *Chips* **2023**, *2*, 102–129. https://doi.org/10.3390/ chips2020007

Received: 2 April 2023 Revised: 26 April 2023 Accepted: 29 April 2023 Published: 1 May 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). sensors and readout electronics encounter significant challenges due to static and dynamic variations and the aging effect [8,9]. To overcome these challenges, industry 4.0 emphasizes the importance of self-X properties, such as self-configuration, self-optimization, self-calibration, and self-diagnosis [10], in automation technology, which are new design principles for effective and autonomous control of the manufacturing process [11]. These self-X properties are essential for ensuring the reliability and performance of smart sensory electronics in industry 4.0, enabling a higher level of control and coordination across the entire value chain of products [12].

Static variations, particularly for analog sensory electronics in modern node complementary metal oxide semiconductor (CMOS) technology, result from process imperfections of semiconductor fabrication [13,14]. Additionally, package mechanical stress and the heat generated during die molding induced by the assembly process can lead to severe mismatches in characteristics of chip devices [15]. Dynamic variations are caused by environmental fluctuations, voltage changes in the power supply, and thermal drift resulting from IC self-heating [16]. On the other hand, the impact of aging, which refers to the deterioration of device characteristics over time, poses ongoing challenges in accurately modeling and forecasting circuit performance and long-term reliability during design and simulation [17,18]. This consideration is essential when evaluating and implementing robust circuits for critical applications under actual operating conditions across the IC lifecycle [19].

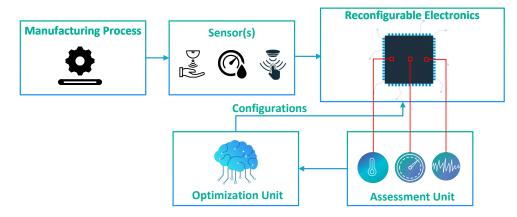

Chip-level dynamic calibration methods of analog and mixed-signal ICs are realized by utilizing configurable elements of the circuit serving as a calibration or tuning knobs and system performance evaluation setups [20–24]. As shown in Figure 1 this approach utilizes evolvable hardware (EHW), which refers to configurable electronic hardware that can be self-configured using ML and AI techniques such as metaheuristic optimization algorithms [25,26]. The evolutionary processing unit (EP) [27] runs the EHW to enable self-X properties for the system. The self-X methodology presents benefits by facilitating the calibration of sensory electronics systems even after chip packaging. Nonetheless, EHW resources may constrain the dynamic performance of analog circuits, owing to increased parasitic effects. Additionally, EHW consumes more die area and necessitates optimization time.

Figure 1. A block diagram of sensory electronics with self-X properties.

Likewise, the overhead associated with the performance evaluation setup is critical for smart sensory electronic systems (SSEs) with self-X properties regarding system complexity, cost, and measurement time of different quantities [8,28]. Synopsys, after acquiring Moortec, developed Silicon Lifecycle Management (SLM) based on on-chip sensing devices and corresponding control loops integrated into their complex chips (SoCs) along with long-term data collection [29–32]. On-chip measurement setups can be classified into two different categories, depending on the evaluation criteria for the intended performance parameters. The direct performance measurement method offers enhanced accuracy and precision at the expense of increased design complexity and chip area [8]. In contrast,

the indirect measurement (IM) method relies on the statistical correlation of different performance characteristics, enabling simultaneous estimation of multiple system performance parameters from simple test stimuli [8,28,33–35].

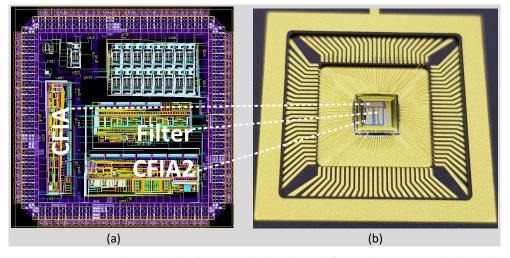

This paper continues our work previously published in [36] after receiving the manufactured chip from the XFAB foundry using the standard CMOS 0.35 µm technology supported by EUROPRACTICE MPW. For the design and verification process, we utilized the Cadence tools, also provided by EUROPRACTICE. Figure 2a shows the layout implementation of the chip, while the chip micrograph can be seen in Figure 2b. The chip has been coated with passivation and the top metal layer for the die surface protection. Hence, the die details are not visible. The chip is assembled using the CPGA 100 package type. The chip is a multi-project chip (MPC) that comprises amplitude and spike-domain analog front-end circuits with self-X properties (AFEX). The MPC cells will serve as the foundation for an advanced universal sensor interface featuring self-X properties, referred to as the USIX chip. However, the focus of this paper is solely on the amplitude domain.

**Figure 2.** MPC USIX chip. (**a**) Chip layout including the pad frame. (**b**) Micrograph photo showing the bonding wires and the sealing ring.

The amplitude domain comprises three essential blocks: the indirect current-feedback instrumentation amplifier (CFIA), the CFIA with digital offset autozeroing (CFIA2), and the programmable analog filter. Our former work was based on extrinsic evaluation of the proposed methodology, while the present study primarily emphasizes the intrinsic, or hard-ware, implementation of in-field optimization for the amplitude domain AFEX, in particular the configurable CFIA. The CFIA is a key component of the AFEX and designed to process wide-input-range sensor input signals with adjustable gain and dynamic performance. It serves as a test vehicle for in-field optimization. A four-row (4X48 bits) shadow register is integrated into the chip for CFIA as a memory unit to save and pipeline the configuration patterns from the optimization solutions, while the other three are utilized to save the following solutions in the background. To reduce the complexity of the performance evaluation setup, a cost-effective indirect measurement method based on the total harmonic distortions (THD) is being implemented to optimize the performance of the CFIA circuit using a single test stimulus.

To carry out in-field performance optimization, an AI agent is embedded inside the automatic test equipment (ATE) for system-performance optimization. This work involves placing the AI agent at the hardware level closest to the device under test (DUT). The proposed experience replay particle swarm optimization (ERPSO) [37] has been selected as the choice of AI-based optimizer and implemented on the field programmable gate array (FPGA) board provided by the Red Pitaya [38], which functions as an edge computing device. As far as long-term chip reliability and power efficiency are con-

cerned, an indirect power monitoring module (PMM) is integrated with the THD-based optimization methodology.

Mixtrinsic evolution, which was originally introduced by [39], involves a population of particles in an optimization algorithm that includes both intrinsic and extrinsic individuals. The previous work conducted at the authors' institute [40] expanded this idea to perform complex measurements, such as open-loop gain, phase margin, and output resistance, using the SPICE simulator in an extrinsic manner, while running simple measurements, such as common-mode range, output-voltage swing, and offset, intrinsically. However, this approach is not always suitable for two reasons. Firstly, simulating circuit modules is less accurate compared to physical hardware of the DUT. Secondly, it requires a significant amount of time depending on the processing power unit.

The primary objective of this work is to address three challenges in the field of chipperformance optimization and reconfigurable analog circuits. The first challenge is to demonstrate a low-cost evaluation setup that can be used for chip-performance optimization. This involves developing a cost-effective method for evaluating the performance of chips, which can help to reduce the overall cost of the evaluation process. The second challenge is to reduce the chip area of configurable SSE with reserved flexibility. This requires the development of a method to selectively apply configurability to the critical elements within the circuit that have a substantial influence on the SSE's performance. The third challenge is to provide a reliable and power-efficient optimization method for reconfigurable analog circuits. This involves developing simple PMM that can improve circuit efficiency and enhance the device's long-term reliability. This study endeavors to advance the development of highly efficient and robust chips that are compatible with Industry 4.0 applications and adhere to the specifications outlined in the association for sensors and measurement (AMA) vision [6]. The remainder of this paper is structured as follows: Section 2 provides an overview of the proposed methodology. Section 3 details the experimental setup and presents the measurement results of the fully-differential CFIA. Lastly, Section 4 offers conclusions and highlights avenues for future research.

## 2. Proposed Methodology

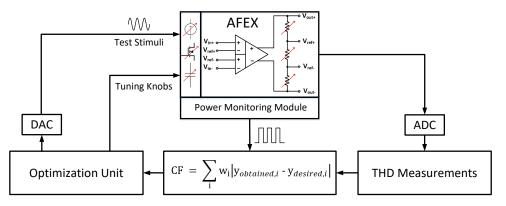

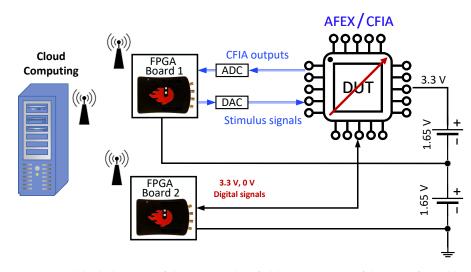

Figure 3 displays a block diagram of the proposed method for cost-effective indirect performance measurement in smart sensory electronic systems. The method utilizes a reconfigurable, fully-differential CFIA as a test vehicle for intrinsic evaluation. A sinusoidal signal with predefined amplitude and frequency is generated by the on-chip digital-to-analog (DAC) converter of Red Pitaya and applied to the CFIA for optimization purposes. Subsequently, the output response of the CFIA is sampled using the high-speed analog-to-digital converter (ADC) of the Red Pitaya board. The THD is then evaluated based on the sampled system response, which aids in predicting most of the CFIA's characteristics simultaneously.

**Figure 3.** A block diagram of the proposed methodology of a power-efficient THD-based indirect measurement method for AFEX.

This method relies on the fact that design imperfections such as slew rate (SR), gainbandwidth product (GBW), input common-mode range (ICMR), effective number of bits, full-power bandwidth, and signal-to-noise ratio (SNR) can be translated as nonlinear distortions at the closed-loop amplifier's output. Optimization of evolvable analog circuits at the transistor level can result in harmful solutions, such as excessive currents that may cause a permanent failure of the DUT or reduce its life cycle, unlike digital evolvable hardware optimization, such as the FPGA optimization. To address this issue, enhance long-term reliability, and improve the CFIA power efficiency, we incorporated a lowcost indirect PMM with a THD-based optimization methodology. Finally, we chose our proposed experience replay particle swarm optimization (ERPSO) [37], which is a modified version of PSO, as the optimization unit.

## 2.1. Indirect Current-Feedback Instrumentation Amplifier (CFIA)

The instrumentation amplifier (in-amp) is the key component of the AFE circuitry for the sensor signal interface and conditioning [41]. Three primary topologies exist for implementing in-amp circuits [42]; those are the capacitive coupling chopper-stabilized in-amp (CCIA) [43], the most traditional in-amp based on three operational amplifiers (op-amps), and the indirect current-feedback in-amp (CFIA) [44]. The CFIA employs the active feedback amplifier topology [45] also referred to as a differential-difference amplifier (DDF) [46], which offers several advantages, such as high input impedance, high open-loop DC gain, and broad bandwidth [47]. Compared to the 3-opamp in-amp, the CFIA is more area and power-efficient, as its input and feedback transconductance stages share a single output-driver stage [41].

A notable feature of the CFIA is the separation and isolation of the input stage's common-mode voltage from the feedback stage's common-mode voltage, achieved through two balanced differential stages [48]. This design allows for the direct connection of sensor pairs with distinct common-mode voltages from the CFIA output common-mode voltage [45]. The input and feedback transconductance stages convert voltage signals into current signals while rejecting the common-mode voltage, resulting in a higher CMRR than that of the 3-opamp in-amp [49]. Furthermore, mismatches in the feedback resistor only lead to a closed-loop gain inaccuracy error [50] and do not impact the CMRR's performance. Depending on the input stage type (NMOS or PMOS), the CFIA's capability to amplify sensor voltages approaching either supply rail renders it suitable for conditioning various sensor types. Nevertheless, the CFIA faces two issues associated with the DDF core amplifier. The first issue concerns gain inaccuracy errors due to the mismatch between input and feedback transconductances. However, this can be tackled using the same type of differential transistors for both input and feedback stages, with meticulous attention to layout matching during physical implementation.

Additionally, employing cascoded biasing currents can achieve a higher degree of matching. The second issue arises from the limited input-differential range of the input transconductance in an open-loop configuration [46]. This limitation becomes particularly problematic when interfacing high dynamic range sensors, such as magnetoresistive sensors [51]. In order to address this issue, the authors in [52] proposed a wide-input-range fully differential CFIA solution based on a fully balanced DDF [53]. This method enabled the concurrent achievement of outstanding dynamic performance and wide-input-range capabilities.

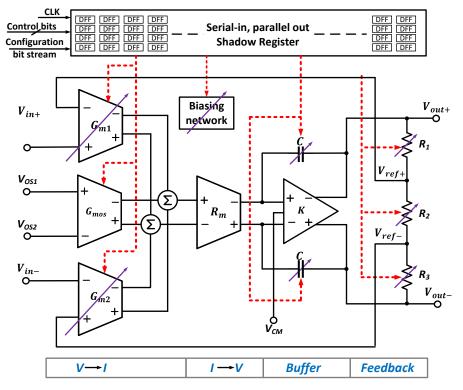

In order to facilitate self-X characteristics, we incorporated configuration capabilities into the critical components of the CFIA circuit, as well as those elements that significantly influence its performance. The selection of these sensitive elements was carried out by running the optimization algorithm on CFIA using extrinsic optimization techniques [54–56] and analyzing the performance of the CFIA. These elements function as design tuning knobs [57], as illustrated in Figure 4 and denoted by the arrow symbol. The algorithm consist of digitally weighted, scalable arrays governed by configuration bits originating from the optimization algorithm. A shadow register memory with 4 rows saves the con-

figuration bits and allows hot swapping between different saved solutions to improve the optimization time.

**Figure 4.** A block diagram of the proposed configurable, fully differential indirect current-feedback instrumentation amplifier (CFIA).

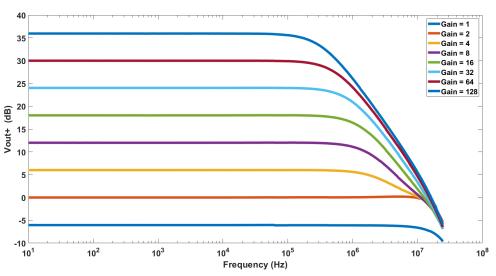

The proposed design incorporates programmable GBW by adjusting the compensation capacitors based on the stability requirements for the selected gain. Eight discrete gain levels are available, i.e., 1, 2, 4, 8, 16, 32, 64, and 128. Moreover, programming the biasing current enables control over the amplifier's dominant and nondominant poles. This feature proves highly beneficial in restoring the stability of the CFIA should it encounter an unstable state. More details about the CFIA circuit schematic are provided in the next section.

#### 2.2. Power Monitoring Module (PMM)

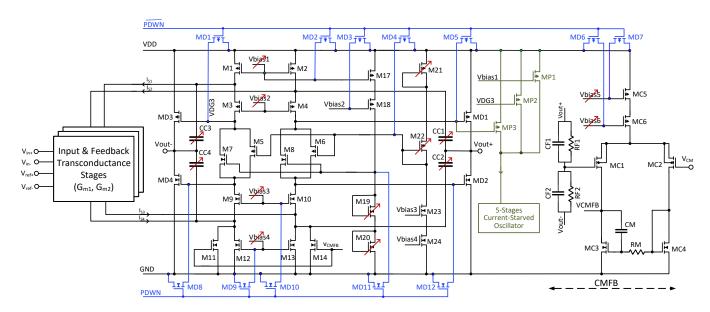

Figure 5 illustrates the primary components of the CFIA, including the PMM. The amplifier employs a buffered class-AB topology [58,59]. A common-mode feedback amplifier (CMFB) from [60] is incorporated to maintain the CFIA's output common-mode voltage around the target voltage ( $V_{CM}$ ). To optimize the output dynamic range,  $V_{CM}$  is established at the midpoint of the supply voltage, specifically at 1.65 V. Due to the utilization of NWELL CMOS technology, the bulk connections for all NMOS transistors are linked to the ground, while those for PMOS transistors are connected to  $V_{DD}$ , unless otherwise specified. The power-down scheme is represented in blue. For the sake of simplicity, the biasing circuit and programmable current source are not displayed. The adjustable input and feedback transconductance ( $G_{m1}$  and  $G_{m2}$ , respectively) can be seen in Figure 6. This configuration comprises three selectable stages that can be multiplexed based on the common- and differential-range voltages. Stage 1 is appropriate for scenarios with high dynamic sensor signals centered within the CFIA-supply operation's midpoint. Stage 2 and 3 incorporate degeneration resistors and benefit when the sensor's common-mode voltage approaches  $V_{DD}$  or  $G_{ND}$ , respectively. More details about the transistor sizes can be found in our previous work in [36,57].

Figure 5. Schematic CFIA diagram integrating the power monitoring module.

Figure 6. Configurable input and feedback transconductance of the CFIA.

In the printed circuit-board (PCB) domain, a prevalent technique for gauging circuit current involves monitoring the voltage drop across a tiny current-sense resistor (CSR) situated along the primary supply-voltage rail. This method employs a differential amplifier and an ADC [61]. The voltage drop on the CSR should not substantially lower the circuit headroom voltage when high currents flow through it. Moreover, the total circuit's alternating current, resulting from dynamic operation, modulates the voltage drop at an equivalent frequency of operation. Consequently, the power supply rejection ratio (PSRR) must be considered when this method is used to assess the power of the amplifier working at a high frequency. When copying this method in integrated circuit solutions, it must be noted that it measures power on the primary supply rails, which can be shared by various cells. Hence, separate power rings should be employed to measure individual cells' power consumption.

In some instances, only the power threshold value detection is necessary, while continuous measurement is not essential. For this purpose, the authors of [62] suggested a fundamental method for detecting maximum power utilizing a simple current-sense sensor. This approach is unsuitable when the power of different optimization solutions must be evaluated. The authors of [63] proposed an alternative technique for indirectly estimating the CFIA DC power. As illustrated in Figure 5 with the green-colored components, this method relies on mirroring scaled-down values of currents from the power-intensive branches into the current-starved ring oscillator [64]. This method modulates the drawn current and, subsequently, the power dissipation in the form of clock frequencies. The existing digital processing unit in smart sensory electronics can easily interpret the generated signal. As the output frequency is proportional to the current drawn, this method can not only identify the power-threshold value but also provide a reasonable approximation of the power consumption for different optimization solutions.

## 2.3. Experience Replay Particle Swarm Optimization (ERPSO)

The ERPSO algorithm enhances the classical PSO algorithm's selection producer by randomly selecting the historical global best of particles using the experience replay buffer (ERB) to tackle the complex objective space problem in SSEs [37]. The ERB concept, commonly used in reinforcement learning [65,66], leverages the accumulated historical values to improve convergence accuracy. In the case of ERPSO, the ERB represents an archive of previously visited global best particles, which reduces the likelihood of being trapped in local minima by utilizing prior knowledge instead of relying solely on recent experiences. The ERB selection process employs an adaptive epsilon-greedy algorithm to balance exploration and exploitation [67].

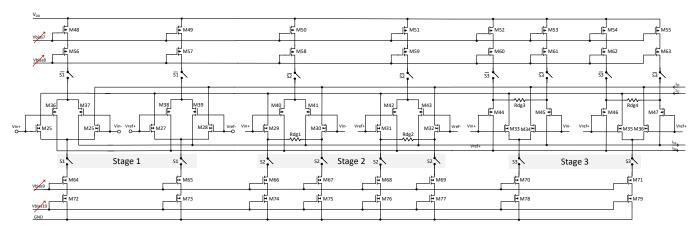

A flow diagram the proposed design methodology is presented in Figure 7. The process begins with a random initialization of the particle's velocity and position. Subsequently, fast Fourier transform (FFT) is executed on the output signal of the reconfigurable amplifier, where a sinusoidal signal with a known fundamental frequency is applied as a test stimulus, and the THD value is calculated from the output spectrum. The power consumption of the solution is then estimated using the built-in indirect PMM. The values of power consumption and THD serve as fitness values or cost functions for the ERPSO algorithm. During the subsequent phase, the ERPSO algorithm updates the respective personal or global best positions, if required.

To balance the trade-off between exploration and exploitation, we modified the velocity-update equation (VUE) of the conventional PSO algorithm by incorporating previously visited global best positions, and implemented its selection using the epsilon-greedy algorithm. According to the proposed VUE, the particles aim to converge quickly towards the global optimal solution with a probability of  $1-\epsilon$ . As a result, the VUE of the conventional PSO algorithm is utilized for the first scenario. On the other hand, to mitigate the probability of premature convergence, the ERPSO algorithm randomly selects any historic global best solution from the ERB with a probability of  $\epsilon$ . This iterative process continues until the maximum number of iterations is reached.

**Figure 7.** A flowchart of the proposed optimization methodology incorporating the ERPSO algorithm, PMM, and THD-based low-cost indirect measurements.

## 3. Experimental Setup

## 3.1. Intrinsic Implementation and Architecture of the Self-X System

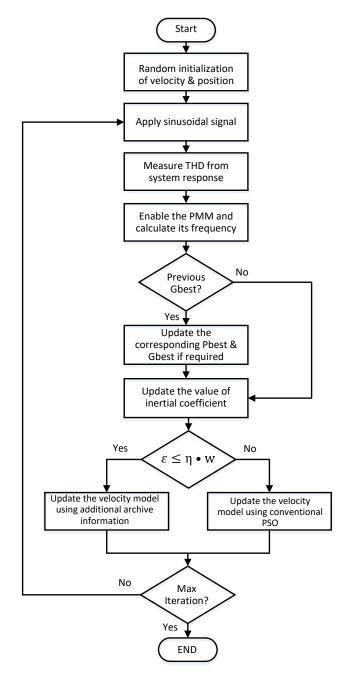

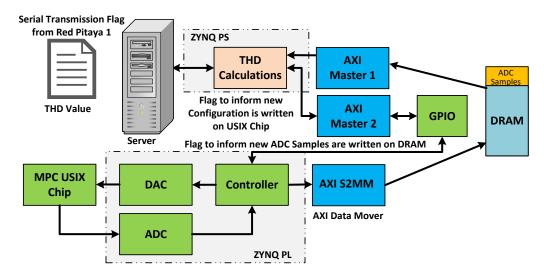

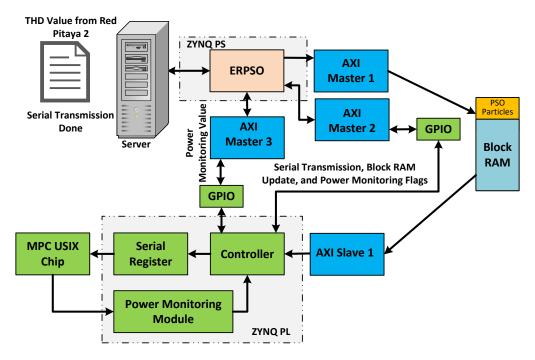

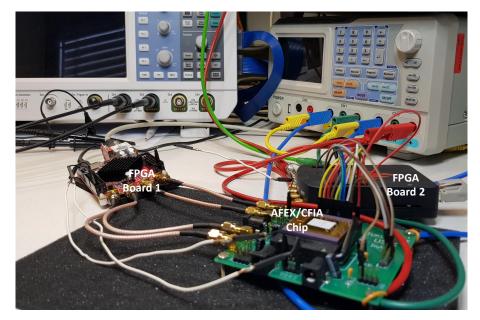

A block diagram of the intrinsic implementation for in-field optimization of the CFIA using the indirect measurement method is displayed in Figure 8. Two Red Pitaya boards are used in this experimental setup, the first one (FPGA board 1) is responsible for data acquisition, THD calculation using FFT, and transmitting data to the server. The second one (FPGA board 2) is responsible for the implementation of ERPSO, a serial data-transfer protocol of the configuration pattern to the CFIA, and calculating the signal frequency of the power-monitoring module.

Figure 8. A block diagram of the proposed in-field optimization of the reconfigurable CFIA circuit.

Since the analog outputs of the Red Pitaya board are referenced to 0 V, the FPGA board 1 is DC level shifted by 1.65 V to match the dynamic input range of the single supply operation of the CFIA powered by 3.3 V. Alternatively, to match the dynamic range between the FPGA board and the CFIA chip it is possible to use a transformer balun, such as PWB2010 from Coilcraft, or an active DC level shifter utilizing wide-bandwidth fully-differential amplifier circuits, such as LMH6553 from Texas Instruments or LTC6363 from Analog Devices. However, using a transformer would limit the experiment to higher frequencies, while the second solution is avoided to eliminate any uncertainty associated with adding another analog block in the chain of the prototyping demonstration.

Figures 9 and 10 show the detailed implementation of the proposed self-X architecture for the CFIA circuit on the Red Pitaya boards 1 and 2, respectively. The generation of necessary binary files for Red Pitaya boards, which enables the implementation of this architecture, is carried out by utilizing the Vivado design suite software provided by Xilinx. The RF DACs incorporated in the Red Pitaya boards are employed to generate fully-differentiated stimulus signals for assessing the CFIA circuit. Meanwhile, the RF ADCs are utilized to acquire the output response of the CFIA circuit. Both the ADC and DAC have a resolution of 14 bits. The ERPSO is executed on the Red Pitaya board 2, while the Red Pitaya board 1 is responsible for carrying out the THD measurement.

Figure 9. Detailed implementation of the self-X architecture for the Red Pitaya board 1.

Figure 10. Detailed implementation of the self-X architecture for the Red Pitaya board 2.

#### 3.2. Workflow of the Optimization Process

The optimization workflow, illustrated in Figure 11, is similar to Synopsys' performance optimization benchmarking platform [31]. The assessment unit comprises two Red Pitaya boards with the associated ADCs/DACs. The optimization goal is to find the best THD value with minimum power consumption using an agglomerative multi-objective optimization approach. The scalable elements in the CFIA circuit serve as tuning knobs. The algorithm reconfigures the system by passing the configuration pattern to the CFIA. In the next step, the output response of the CFIA is measured. The algorithm continues in this loop until the end condition is reached. The results are reported at the end of the optimization process.

Figure 11. Performance optimization workflow for smart sensory electronics.

The optimization process begins by serially writing the particle values of ERPSO to the shadow register of the CFIA using the Red Pitaya board 2. The CFIA is powered down during the data writing process on the shadow register to avoid the unknown transition state. After completing the data-writing process, the CFIA is turned on, and the Red Pitaya board 1 is acknowledged via the server to start performing the THD calculations for the corresponding ERPSO particle solution.

For the THD calculation task, the Red Pitaya board 1 applies the fully-differential sinusoidal stimulus to the input of the CFIA and acquires its output response by using the onboard RF DAC and ADC, respectively. In the next step, the acquired data samples are written to the shared dynamic random-access memory (DRAM) of the Red Pitaya board using an advanced eXtensible interface (AXI) stream to memory-mapped IP. The controller module sets the acknowledgment flag to report to the processing subsystems (PS) of the Red Pitaya board about the acquisition process completion. Subsequently, the THD calculation is performed on the acquired samples on the PS side of the Red Pitaya board 1. This THD value is passed to the Red Pitaya board 2 via the server for the ERPSO algorithm. After that,

the ERPSO activates the power-motioning module to measure the output frequency from the power-monitoring circuit of the CFIA to estimate the DC power consumption of the corresponding solution indirectly. It is worth noting that, during the THD calculation, the power monitoring process is deactivated to avoid transient pulse switching disturbances coupled to the analog outputs. The optimization process continues until the maximum number of iterations is reached. Figure 12 presents the experimental Lab setup of the proposed methodology. The four-layer PCB prototyping board is designed using Eagle Autodesk software. Separated power and ground plates with decoupling capacitors near the chip power pins are added to improve the system's noise performance.

Figure 12. Lab setup for the evaluation of the proposed methodology.

#### 4. Measurement Results

## 4.1. Shadow Register Verification

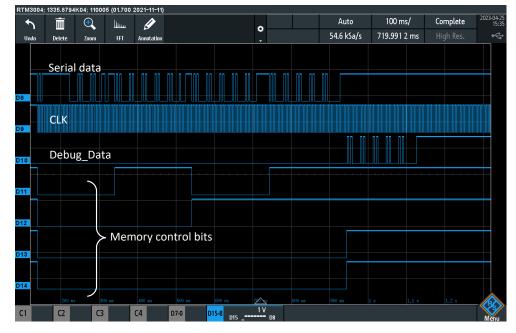

The initial verification step involves providing the CFIA circuit with the default configuration pattern, which was obtained from the post-layout extrinsic evaluation described in [36]. The configuration data is transferred serially from the Red Pitaya to the shadow register of the CFIA. The transfer rate is set to 1 Kb/s, utilizing a transfer mode similar to the SPI (serial peripheral interface) protocol mode 0. In this arrangement, the Red Pitaya and the chip function as master and slave devices, respectively. During the idle state, the clock polarity is set to a logical low level, while the shadow register samples data on the rising edge, and data transitions occur on the falling edge. Four bits are used to control the reading and writing operations on the shadow register, two bits to perform the writing operation, and two bits for the reading operation. Additionally, the most significant bit (MSB) from the register is connected to the "Dout\_Debug" pin of the chip, which is utilized for debugging the serial data of the register, as presented in [36]. Figure 13 illustrates the debugging process, wherein the data initially written to the first row of the register is read back successfully after the completion of the writing operation on all four rows, which demonstrates the successful transfer of the configuration data.

## 4.2. CFIA Testing Using the Default Configuration

While the circuit functioned correctly during the simulation with the RC extraction netlist, and passed the PVT (process, voltage, and temperature) verification by using Monte Carlo (MC) and worst-case (WC) simulations under an extended industrial temperature range (from -40 °C to 85 °C) and by considering  $\pm 10\%$  of supply voltage variation, actual measurements revealed that it suffers from instability. This instability may be attributed to

shifts in device characteristics induced by the fabrication and packaging process, although it has to be mentioned that a process variation of 6 sigma was considered during simulation.

Figure 13. Shadow-register-function verification using the debugging pin.

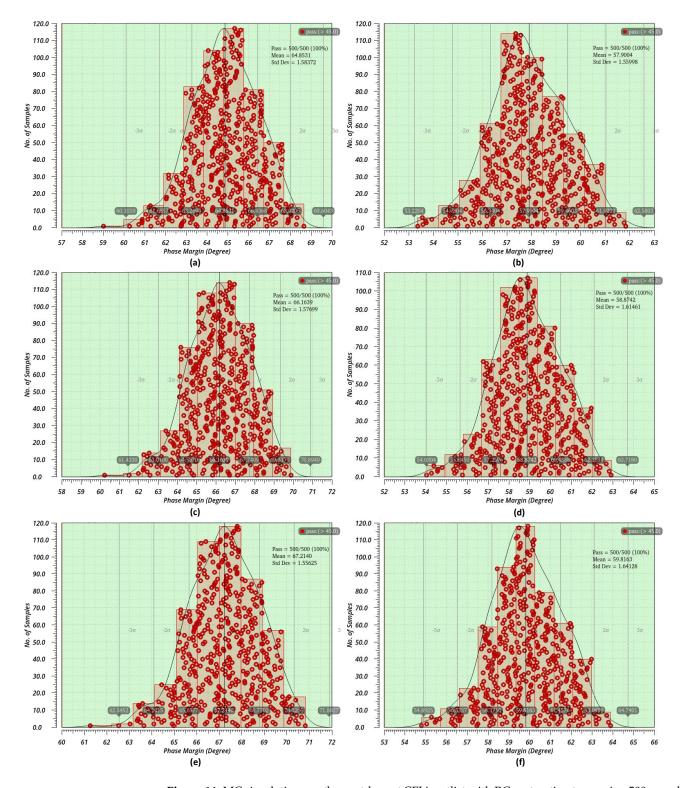

Figure 14 illustrates the MC post-layout simulation for evaluating the CFIA phase margin (PM) as an indicator of unity-gain closed-loop stability in the default configuration. The evaluation employed 500 samples and a Gaussian-distribution function to emulate the actual process profile. Both process and mismatch variations were considered for the entire CFIA circuit during the MC run. As depicted in the figure, the CFIA exhibited a safe PM at the extreme corners, achieving a 100% yield for a targeted PM above 45 degrees. Throughout the test, a 15 pF capacitive load and a 10 k $\Omega$  resistive load were connected to each differential output pair. It is important to note that the default configuration only employs the two least significant bits of the configurable compensation capacitor and consumes reduced power in the output stage. Consequently, there is available space for further PM enhancement, although it is not deemed necessary based on the simulation results.

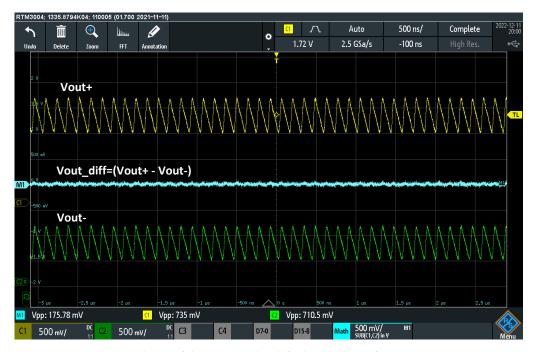

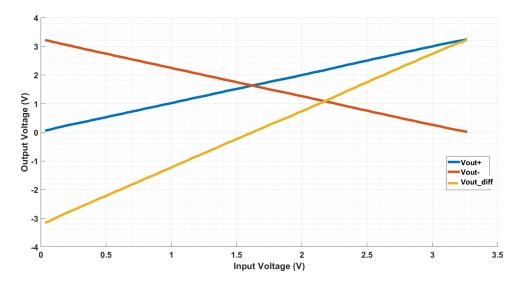

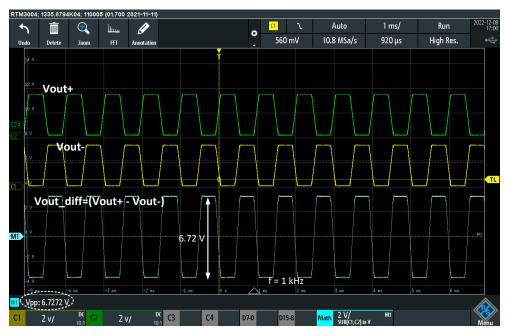

Figure 15 demonstrates the practical behavior observed at the outputs when both inputs are tied to the DC common-mode voltage (VCM) of 1.65 V. The input capacitance of the mixed-signal storage oscilloscope (MSO) from Rohde & Schwarz is 14 pF by the X10 channels with 10 M $\Omega$  impedance, which falls within the load capability range of the designed CFIA.

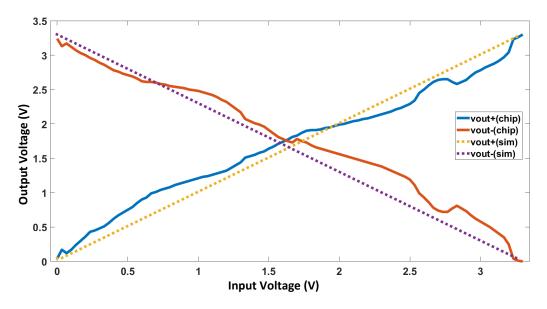

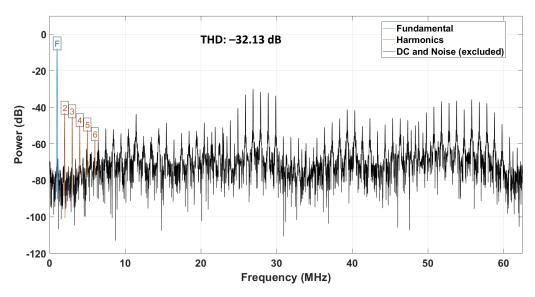

In contrast, the output signals convey valuable information, signifying that a symmetrically balanced layout implementation leads to even and in-phase outputs, thus achieving a high common-to-differential-mode rejection ratio. As a result, the differential output signal (Vout\_diff) exhibits a reduced oscillation amplitude. The fully differential circuit's ability to subtract common signals in noise amplitude levels is advantageous [68]. However, oscillatory behavior at the output indicates that the CFIA cannot respond linearly to the input signal. Figure 16 demonstrates this nonlinearity by showing the output DC characteristics of the CFIA when the inputs are swept linearly from 0 to 3.3 V with unity gain configuration and a step size of 33 mV. This behavior is compared with the characteristics derived from the post-layout simulation. Figure 17 illustrates the output's transient response to a fully differential sinusoidal input signal with a 1 Vp-p amplitude and a frequency of 1 MHz, highlighting the extent of distortion in the time domain. Additionally, Figure 18 displays the differential output signal in the frequency domain acquired through the execution of the FFT. The output nonlinearity introduces a harmonic distortion within the signal's frequency

spectrum. Consequently, the CFIA nonlinearity is correlated with the measured THD value. In this particular case, a THD value of -30 dB indicates substantial nonlinearity.

**Figure 14.** MC simulations on the post-layout CFIA netlist with RC exctraction type using 500 samples per corner: (a)  $V_{DD} = 3.0$  V and T = -40 °C; (b)  $V_{DD} = 3.0$  V and T = -85 °C; (c)  $V_{DD} = 3.3$  V and T = -40 °C; (d)  $V_{DD} = 3.3$  V and T = 85 °C; (e)  $V_{DD} = 3.6$  V and T = -40 °C; (f)  $V_{DD} = 3.6$  V and T = 85 °C.

Figure 15. Unstable condition of the CFIA under default pattern configuration.

The experiment described above was conducted for the first time on 15 chips received from the foundry, selected from a batch of 32 and numbered sequentially. In this experiment, chip numbers 1 and 3–16 were tested, all demonstrating similar characteristics. This may be attributed to their origin from the same wafer during the fabrication. In other words, if the circuit is designed using fixed-size elements, the entire batch of products may need to be discarded. The significance of configurable circuits with self-X properties becomes evident in addressing such issues. Consequently, in the subsequent experiment, the chip was subjected to in-field optimization using the ERPSO algorithm to explore the optimum configuration pattern that brings the CFIA into the optimum operating region.

**Figure 16.** Output DC characteristics of the unstable CFIA with unity gain configuration compared to the post-layout simulation.

**Figure 17.** The output's transient response to the fully differential sinusoidal signal under unstable conditions.

Figure 18. FFT output of the CFIA under unstable conditions.

#### 4.3. PMM Characterization

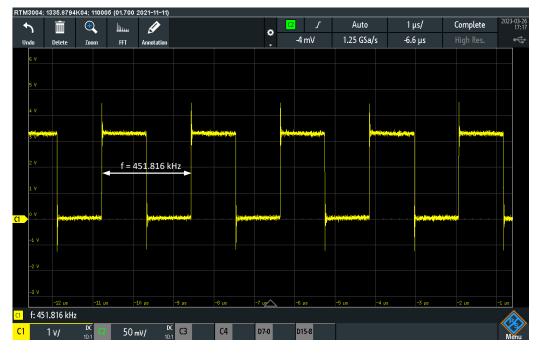

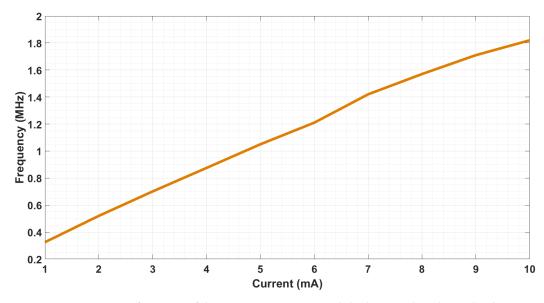

Prior to the optimization, the power monitoring circuit was evaluated by varying the CFIA biasing current through programming the current DAC, and subsequently monitoring the corresponding output-pulse frequency of the module. The PMM circuit is a current-to-frequency converter, generating a quasi-digital signal characterized by a 50% duty cycle as shown in Figure 19. The CFIA current is recorded using the current meter of the power supply unit (PeakTech 6181), which offers a resolution of 1 milliampere. A frequency-to-digital converter (FTD) was designed on the Red Pitaya to read the signal frequency from the PMM and convert it to a decimal value, as given in Table 1 via selected values. Upon detecting the initial rising edge of the output signal of the PMM circuit, the FTD module begins counting until the subsequent rising edge is identified, at which point the counter value corresponds to the relevant frequency. The FTD counter operates at a rate

of 125 MHz, synchronized with the Red Pitaya's system clock. Given that the maximum PMM frequency has been determined to be less than 10 MHz, the FTD's resolution proves adequate for this particular measurement.

Figure 19. Output signal of the integrated power monitoring module.

| Config Nr. | <b>Clock Frequency</b> | Decimal Equivalent | <b>CFIA Current</b> |

|------------|------------------------|--------------------|---------------------|

| 1          | 325 kHz                | 24,561             | 1 mA                |

| 2          | 520 kHz                | 15,372             | 2 mA                |

| 3          | 701 kHz                | 11,401             | 3 mA                |

| 4          | 875 kHz                | 9162               | 4 mA                |

| 5          | 1.05 MHz               | 7233               | 5 mA                |

| 6          | 1.21 MHz               | 6618               | 6 mA                |

| 7          | 1.42 MHz               | 5627               | 7 mA                |

| 8          | 1.57 MHz               | 4725               | 8 mA                |

| 9          | 1.71 MHz               | 4566               | 9 mA                |

| 10         | 1.82 MHz               | 4404               | 10 mA               |

| 11         | 4.45 MHz               | 1626               | 24 mA               |

| 12         | 4.53 MHz               | 1595               | 25 mA               |

| 13         | 4.86 MHz               | 1489               | 27 mA               |

Table 1. Recorded values of frequency-to-decimal conversion of the power monitoring module.

Figure 20 shows that the power monitoring scheme exhibits adequate linearity, facilitating the optimization algorithm by providing the necessary CFIA power data. This enables identifying and selecting the most efficient solution within the investigated range. Indeed, the linearity graph is influenced by the current measurement resolution.

## 4.4. CFIA Performance Optimization Using the Proposed Methodology

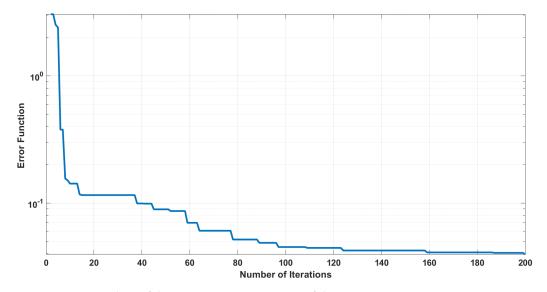

A fully differential sinusoidal signal, featuring an amplitude of 1 Vp-p and a frequency of 1 MHz, was generated by Red Pitaya 1 using the Digital Signal Synthesizer (DSS) offered by the Xilinx Vivado IP blocks. This signal functioned as the test stimulus for the optimization process. The Red Pitaya's ADC acquired the CFIA output at a sampling frequency of 125 MHz, which was beneficial for THD calculation through FFT. Moreover, the optimization algorithm employed 15 particles and 200 iterations. In the agglomerative multi-objective optimization approach, an 80% weight was assigned to the THD value, and a 20% weight was assigned to the power-monitoring aspect. To minimize the impact of random occurrences or lucky shots, the optimization process was performed for 10 independent runs on the chip marked as number 1. Comprehensive information on the optimization algorithm can be found in [37,63]. The mean value of the error-convergence curve for the optimization algorithm is illustrated in Figure 21. The CFIA was set to unity gain configuration for the most critical stability condition.

**Figure 20.** Linearity performance of the power-monitoring module showing the relationship between the frequency and the CFIA current.

Figure 21. Mean values of the error-convergence curve of the CFIA optimization.

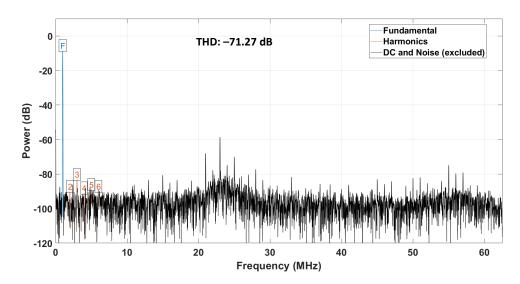

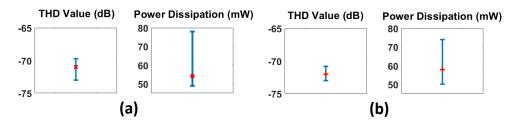

As illustrated in Figure 22, the FFT graph presents the frequency response corresponding to one of the solutions discovered by the algorithm. Upon completion of the optimization process, the mean THD value attained is -72 dB, accompanied by a power dissipation of 55 mW. This is visually represented through the error bar graph in Figure 23a for 10 independent trials. Concurrently, Figure 23b demonstrates the optimization statistics for a single optimization iteration across 15 distinct chips.

Figure 22. FFT output of the stable CFIA solution found using the optimization.

**Figure 23.** Box plots of the ERPSO algorithm (**a**) over 10 independent runs on a single chip. (**b**) A single run for 15 independent chips.

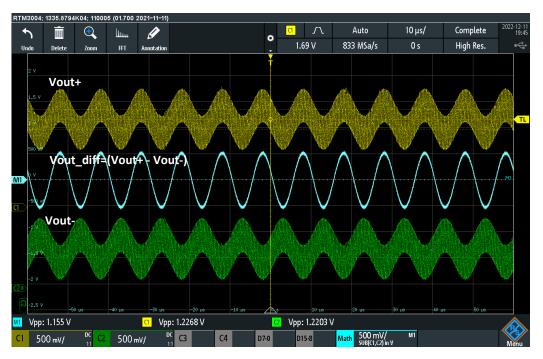

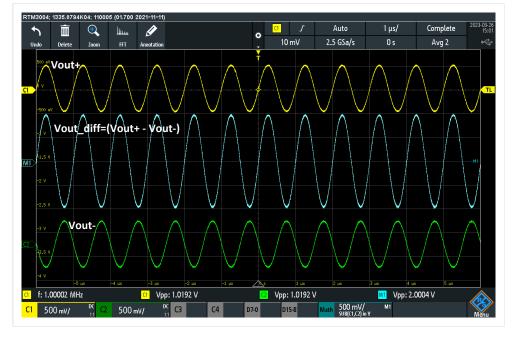

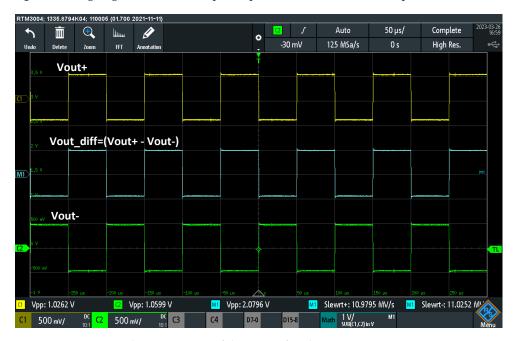

The sinusoidal output response is presented in Figure 24, and it is evident that the signal is devoid of oscillation. The measured slew rate from the impulse response analysis is approximately  $\pm 11 \text{ V/}\mu\text{s}$ . Moreover, in order to validate the stability, a step response test was conducted. The results, depicted in Figure 25, indicate that the rising and falling edge features exhibited a phase margin exceeding 60 degrees. The DC characteristics presented in Figure 26 demonstrate the dynamic input range at unity gain. This wide differential range effectively enables interfacing high-output differential sensor signals such as tunnel magneto-resistance (TMR). The AC response of the system is assessed at various programmed gain settings, as illustrated in Figure 27. However, it should be noted that the graph depicts a gain that was 6 dB lower than anticipated. This disparity is not an issue and can be attributed to the setup, which involved the acquisition of a singleended output during the bode plot. Incorporating a class-AB-complementary output stage, the CFIA circuit featured an output common-mode range that approached the supply rails, as depicted in Figure 28. During this test, a small sinusoidal signal with an amplitude of 250 mVp-p and a frequency of 1 kHz is utilized, while the CFIA gain is established at 16. It should be noted that the output-signal constraint is attributable to the output stage rather than the input characteristics.

The preceding discussion suggests that the nonlinear behavior of a CFIA or any CMOS amplifier can be indirectly estimated from the measured THD values. This is primarily due to the statistical interdependence of the various performance characteristics of the CFIA [28]. For instance, in Figures 16 and 17, the CFIA exhibited oscillatory behavior at the output, and its input range was entirely nonlinear. Consequently, as can be observed from Figure 18, its THD value was considerably reduced due to the presence of a harmonic distortion. However, after performing the self-X performance optimization loop, the THD value of the CFIA improved significantly, which indirectly indicates a linear output response, step and sinusoidal output response, and flat frequency response, as shown in Figures 22, 24, 25, 27 and 28. Therefore, it was demonstrated in practice that the proposed

THD-based optimization methodology can be effectively employed to optimize most of the performance characteristics of the CFIA simultaneously.

Figure 24. Large signal sinusoidal output response of the CFIA after the optimization.

Figure 25. Large signal-step response of the CFIA after the optimization.

Table 2 compares the CFIA performance between extrinsic and intrinsic evolution. The intrinsic differential DC gain is indirectly estimated from the closed-loop gain error, as it is not possible to disconnect the feedback network from the amplifier core. Overall, it is evident that there are differences between the extrinsic and intrinsic results. However, as mentioned earlier, this discrepancy is due to the shift after manufacturing. One possible reason could be the inductance effect of the package leads and the bonding wires that might put the CFIA in an oscillatory condition, and it is our first prototyping chip fabricated using the XFAB technology. The fourth column in the table illustrates the performance of the CFIA, utilizing the default configuration obtained from the extrinsic optimization

process. However, due to the inherent instability and oscillatory nature of the CFIA under this particular configuration, it is not feasible to accurately characterize its performance. Nonetheless, the optimization using the proposed approach successfully identified the optimal configuration pattern, resulting in satisfactory performance of the CFIA function. This difference in configuration patterns also accounts for the divergence between the simulated and measured power, as the algorithm attempts to find the stable solution by pushing the first nondominant pole from the CFIA driver stage away from the unitygain frequency point using higher currents. The output stage is designed with fixed-size transistors; therefore, shifting their associated poles is only possible by increasing the transconductance  $(g_m)$  through a higher current. Moreover, the algorithm tries to increase the compensation capacitor, which further explains the decrease in the measured slew-rate value. The compensation capacitor ranges from 0.35 pF to 2.35 pF with a step size of 0.25 pF. The average value obtained from the extrinsic evaluation was 0.850 pF, while the intrinsic evaluation yielded a mean value of 2 pF. It is worth mentioning that the primary purpose of this work was to develop a software and hardware concept for reconfigurable electronics to make degraded circuits recover with a minimum system performance setup cost.

**Figure 26.** Output DC characteristics of the stable CFIA with unity gain configuration after the optimization.

Figure 27. Small signal AC response of the optimized CFIA with different gain settings.

**Figure 28.** Output dynamic range of the CFIA showing the rail-to-rail properties of the class-AB output stage.

| <b>Table 2.</b> CFIA characteristics based on extrinsic and intrinsic optimization solutions ( $V_{DD} = 3.3 \text{ V}$ , |

|---------------------------------------------------------------------------------------------------------------------------|

| $V_{CM} = 1.65 \text{ V}, T_{simulation} = 27 ^{\circ}\text{C}, T_{measurement} = 22 ^{\circ}\text{C}).$                  |

| CFIA Design Parameter            | Schematic Level<br>Mean of 10     | Post-Layout Level<br>Mean of 10   | Chip Level before Optimization | Chip Level<br>Mean of 10         |

|----------------------------------|-----------------------------------|-----------------------------------|--------------------------------|----------------------------------|

| Differential DC gain $(A_{VD})$  | 94.80 dB                          | 94.73 dB                          | N/A                            | >80 dB                           |

| Gain–bandwidth product (GBW)     | 47.75 MHz                         | 39.41 MHz                         | N/A                            | >10 MHz *                        |

| Phase margin (PM)                | 73.22°                            | $60.47^{\circ}$                   | <0°                            | >60°                             |

| Slew rate (SR)                   | $\pm 63.38 \text{ V/}\mu\text{s}$ | $\pm 60.34 \text{ V/}\mu\text{s}$ | N/A                            | $\pm 11 \text{ V/} \mu \text{s}$ |

| PMM output frequency $(f_{ck})$  | 347.18 kHz                        | 377.48 kHz                        | 700 kHz                        | 3.1 MHz                          |

| Static power dissipation $(P_D)$ | 4.17 mW                           | 4.16 mW                           | 9.9 mW                         | 53 mW                            |

| Input Dynamic Range              | rail-to-rail                      | rail-to-rail                      | N/A                            | rail-to-rail                     |

| Output Dynamic Range             | rail-to-rail                      | rail-to-rail                      | N/A                            | rail-to-rail                     |

\* The Bode plot capability of the utilized MSO (Rohde & Schwarz 3004) is limited to 10 MHz due to its signal generator; therefore, the CFIA's gain bandwidth is expected to be higher.

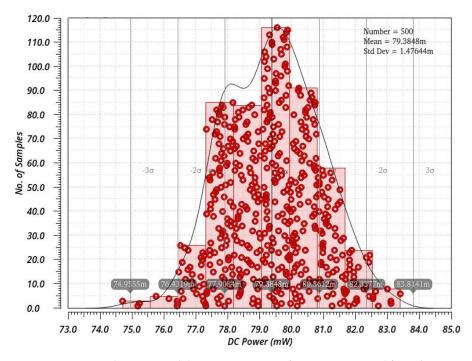

The optimization process was repeated without using a power monitoring approach, and the resulting mean value of the CFIA power consumption was found to be 80 mW for achieving the same THD value of -72 dB. This clearly indicates that incorporating power monitoring into the solution resulted in a 34% increase in power efficiency. This has significant advantages, especially for applications with limited power resources, such as sensor nodes powered by energy harvesting or batteries. Furthermore, reducing the current also improves the device's lifetime by avoiding the chip-interconnection currentdensity limitation. An excessive current could cause interconnection failure due to the electromigration. To validate the deviation between the designed and manufactured chips, a solution from the intrinsic optimization process was transferred to the extrinsic evaluation stage. The difference in performance becomes apparent when examining power consumption values. The specific configuration consumes 15 mA during the intrinsic run and 24 mA during the extrinsic evaluation. Table 3 presents the CFIA performance using this imported configuration, facilitating comparison with the values depicted in Table 2. It is important to note that extrinsic evaluation for this measurement was conducted at the typical mean corner of the process module, while the actual fabrication inherently differs. To render this comparison more realistic, a Monte Carlo simulation was performed around

this solution. Nevertheless, the deviation was observed to remain outside the intrinsic region, as can be seen from Figure 29 by recording the power dissipation.

It is important to highlight that the sensory measurement process experiences an interruption when the device is subject to optimization. However, two potential approaches can facilitate continuous measurement. The first approach involves implementing a real-time operating system (RTOS) or a time-triggered embedded system (TTES) on the Red Pitaya board when dealing with low-frequency sensor signals, such as a TMR sensor measuring the speed of a rotating shaft. This implementation allows for interleaving the calibration and measurement processes. The second approach, applicable to high-frequency sensor signals, involves adopting a ping-pong strategy, wherein one CFIA undergoes optimization while the other remains active and fully operational.

**Table 3.** Extrinsic evaluation of the intrinsically optimized configuration showing the deviation between the simulated and fabricated chip under the same measurement conditions ( $V_{DD} = 3.3$  V,  $V_{CM} = 1.65$  V, T = 22 °C).

| CFIA Design Parameter                   | Intrinsic Evaluation             | Extrinsic Evaluation             |  |

|-----------------------------------------|----------------------------------|----------------------------------|--|

| Differential DC gain (A <sub>VD</sub> ) | >80 dB                           | 100 dB                           |  |

| Gain-bandwidth product (GBW)            | >10 MHz                          | 39.5 MHz                         |  |

| Phase margin (PM)                       | >60°                             | 82°                              |  |

| Slew rate (SR)                          | $\pm 10.4 \text{ V/}\mu\text{s}$ | $\pm 71 \text{ V/} \mu \text{s}$ |  |

| PMM output frequency $(f_{ck})$         | 2.98 MHz                         | 5.72 MHz                         |  |

| Static power dissipation $(P_D)$        | 49 mW                            | 79.2 mW                          |  |

| Input Dynamic Range                     | rail-to-rail                     | rail-to-rail                     |  |

| Output Dynamic Range                    | rail-to-rail                     | rail-to-rail                     |  |

Figure 29. MC simulation around the optimization configuration imported from the intrinsic evaluation.

In comparison to the recent literature, the authors of [44] developed a fully differential CFIA circuit utilizing 180 nm CMOS technology for biomedical impedance-spectroscopy applications. With a fixed gain of four, the CFIA circuit achieved a -3 dB bandwidth of 5.83 MHz and slew rate of 8.3 V/µs while driving a 1.33 pF capacitive load. The measured THD value was -38 dB at a differential signal range of 60 mVp-p and a frequency of 10 kHz. The authors reported that the CFIA circuit's performance would be inferred when

the differential range approaches 100 mVp-p. Operating on a single 1.8 V supply, the circuit consumed a total power of 4.795 mW. In our study, the CFIA circuit demonstrated a THD value of -72 dB at a 1 Vp-p differential voltage and 1 MHz frequency. As depicted in Figure 27, the -3 dB CFIA bandwidth is approximately 3 MHz at a gain equal to four and a slew rate of 11 V/µs while driving a capacitive load of nearly 15 pF. Additionally, the proposed CFIA offers eight programmable gain levels but consumes 53 mW of power when powered by a 3.3 V supply operation. Due to the programmable devices, our proposed CFIA consumes a layout area of 1.6 mm  $\times$  0.38 mm compared to 119.5 µm  $\times$  254.6 µm in [44].

Compared to some commercial CFIA chips available in the market, the LMP8358 CFIA from Texas Instruments demonstrates a bandwidth of 8 MHz at a gain of 10, while driving a capacitive load of 10 pF and a resistive load of 10 k $\Omega$ . The device offers seven programmable gain levels, i.e, 20, 50, 100, 200, 500, and 1000, utilizing a parallel SPI protocol for communication. The configurable compensation capacitor is set automatically according to the selected gain to optimize the bandwidth. Capable of processing a differential signal of  $\pm 100 \text{ mVp-p}$ , the LMP8358 consumes an average power of 6.27 mW. With an offset-voltage correction below 10  $\mu$ V, the chip is apt for interfacing low-frequency differential sensor signals, even those with weak amplitudes, supported by its high gain capabilities. On the other hand, the MCP6N11 CFIA from Microchip offers five programmable gain levels, i.e., 1, 2, 10, and 100. The unity gain bandwidth is 500 kHz, and the device operates within a supply voltage range of 1.8 V to 5.5 V. When powered by a 3.3 V supply, the MCP6N11 consumes 2.64 mW. Additionally, the chip supports rail-to-rail input differential range.

## 5. Conclusions

A cost-effective and power-efficient approach is used for the intrinsic evolution of the configurable CFIA. The primary focus is to reduce the complexity of the performance evaluation setups required to support the AFE with self-X properties for in-field optimization. Initial testing, conducted prior to the intrinsic optimization process, was based on post-layout simulations using the configuration obtained from extrinsic optimization; it revealed degraded performance and unexpected instability within the CFIA circuit. Then, the in-field optimization, based on THD and a power-monitoring approach, successfully discovered the optimal configuration for the linear operation of the CFIA circuit using the ERPSO algorithm. This outcome underscores the benefits of implementing sensory electronic circuits with self-X properties for yield optimization. In essence, without the self-X capability, this manufactured batch may have been discarded, resulting in significant costs associated with its fabrication. The ERPSO algorithm is implemented at the hardware level, using Red Pitaya FPGA boards. During the optimization process, the DACs and ADCs of the Red Pitaya were utilized to assess and acquire data from the CFIA circuit. The THD optimization approach proved to be an effective tool in reducing the total number of assessment units required to optimize the performance of the CFIA or any other type of linear circuits. This is primarily due to the statistical correlation of the various performance characteristics of the amplifier on the measured THD value. Additionally, it has been observed that even the unstable circuit condition is correlated to the lower THD value. However, to ensure stability, a pulse test was conducted at the end of the optimization process. Therefore, the majority of the optimization process was conducted using a single sinusoidal signal stimulus, which was found to be an efficient method for improving amplifier performance. The power-monitoring technique was employed to help the ERPSO algorithm in identifying the power-efficient solution from the explored search space. This significantly improves the power efficiency of the solution, ultimately leading to a prolonged device lifetime and better energy utilization. The CFIA is optimized for a 1 MHz signal frequency and a 1 Vp-p dynamic input range. The achieved average optimized THD is equal to -72 dB with 34% more power efficiency than that of the optimization process without power monitoring. The output dynamic of the rail-to-rail was accomplished due to the use of the push-pull output stage. The chip was designed using the

XFAB 0.35 µm technology. The optimization carried out in this work was conducted under static conditions, specifically at room temperature; our future research will involve running the optimization across industrial temperature ranges using BINDER climate chambers. Additionally, future research will examine the use of CFIA for interfacing low-frequency and high-dynamic-range sensor signals, such as TMR sensors. The optimization will be aimed at reducing power consumption, as a smaller bandwidth is necessary to achieve the desired THD value in these lower-frequency applications.

**Author Contributions:** Conceptualization, A.K., S.A. and Q.Z.; methodology, A.K., S.A. and Q.Z.; software, Q.Z. and S.A.; validation, Q.Z. and S.A.; formal analysis, S.A. and Q.Z.; investigation, Q.Z. and S.A.; data curation, Q.Z. and S.A.; writing—original draft preparation, A.K., Q.Z. and S.A.; writing—review and editing, A.K.; visualization, Q.Z. and S.A.; supervision, A.K.; project administration, A.K. All authors have read and agreed to the published version of the manuscript.

Funding: This research received funding from DAAD by PhD grants.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Not applicable.

Acknowledgments: The authors would like to thank the DAAD (Deutscher Akademischer Austauschdienst) for sponsoring the PhD researchers. We also thank EUROPRACTICE for their support in providing design tools and MPW fabrication services for our prototype chip and research activity. The reported work and, in particular, the chip manufacturing was made possible due to funding by the BMBF (German Federal Ministry of research), obtained in the context of the program SElekt\_I40, and the concluded consortial project MoSeS-Pro, subproject 'Robuste adaptive integrierte Sensorelektronik und Informationsverarbeitung mit Self-X-Eigenschaften für zuverlässige Systeme der Industrie 4.0', grant no. 16ES0425 and is gratefully acknowledged.

Conflicts of Interest: The authors declare no conflicts of interest.

## Abbreviations

The following abbreviations are used in this manuscript:

| CMOS  | Complementary metal oxide semiconductor           |

|-------|---------------------------------------------------|

| AFE   | Analog-front-ends                                 |

| AFEX  | Analog-front-ends with self-X properties          |

| EHW   | Evolvable hardware                                |

| PSO   | Particle swarm optimization                       |

| ATE   | Automatic test equipment                          |

| CFIA  | Current-feedback in-amp                           |

| SIPO  | Serial-in, parallel-out register                  |

| PMM   | Power monitoring module                           |

| MHOAs | Meta-heuristic optimization algorithms            |

| ERPSO | Experience replay particle swarm optimization     |

| USIX  | Universal sensor interface with self-X properties |

| ADC   | Analog to digital converter                       |

| PM    | Phase margin                                      |

| GBW   | Gain-bandwidth product                            |

| SR    | Slew rate                                         |

| THD   | Total harmonic distortion                         |

| FFT   | Fast Fourier Transform                            |

| FPGA  | Field programmable gate array                     |

| SPI   | Serial peripheral interface                       |

| DAC   | Digital to analog converter                       |

|       |                                                   |

## References

- Diez-Olivan, A.; Del Ser, J.; Galar, D.; Sierra, B. Data fusion and machine learning for industrial prognosis: Trends and perspectives towards Industry 4.0. Inf. Fusion 2019, 50, 92–111. [CrossRef]

- 2. Ahmed, I.; Jeon, G.; Piccialli, F. From artificial intelligence to explainable artificial intelligence in industry 4.0: A survey on what, how, and where. *IEEE Trans. Ind. Inform.* 2022, *18*, 5031–5042. [CrossRef]

- Arrieta, A.B.; Díaz-Rodríguez, N.; Del Ser, J.; Bennetot, A.; Tabik, S.; Barbado, A.; García, S.; Gil-López, S.; Molina, D.; Benjamins, R.; et al. Explainable Artificial Intelligence (XAI): Concepts, taxonomies, opportunities and challenges toward responsible AI. *Inf. Fusion* 2020, *58*, 82–115. [CrossRef]

- Kagermann, H.; Helbig, J.; Hellinger, A.; Wahlster, W. Recommendations for Implementing the Strategic Initiative INDUSTRIE 4.0: Securing the Future of German Manufacturing Industry; final report of the Industrie 4.0 Working Group; Forschungsunion, National Academy of Science and Engineering (acatech): Berlin, Germany, 2013.

- 5. Wójcicki, K.; Biegańska, M.; Paliwoda, B.; Górna, J. Internet of Things in Industry: Research Profiling, Application, Challenges and Opportunities—A Review. *Energies* 2022, *15*, 1806. [CrossRef]

- 6. Trends, S. Trends in Future-Oriented Sensor Technologies; AMA Association for Sensor Technology: Berlin, Germany, 2014.

- Jamwal, A.; Agrawal, R.; Sharma, M.; Giallanza, A. Industry 4.0 technologies for manufacturing sustainability: A systematic review and future research directions. *Appl. Sci.* 2021, 11, 5725. [CrossRef]

- Lee, S.; Shi, C.; Wang, J.; Sanabria, A.; Osman, H.; Hu, J.; Sánchez-Sinencio, E. A built-in self-test and in situ analog circuit optimization platform. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2018, 65, 3445–3458. [CrossRef]

- 9. Lin, Y.B.; Lin, Y.W.; Lin, J.Y.; Hung, H.N. SensorTalk: An IoT device failure detection and calibration mechanism for smart farming. *Sensors* **2019**, *19*, 4788. [CrossRef]

- König, A. Integrated sensor electronics with self-x capabilities for advanced sensory systems as a baseline for industry 4.0. In Proceedings of the Sensors and Measuring Systems 19th ITG/GMA-Symposium, Nuremberg, Germany, 26–27 June 2018; pp. 1–4.

- 11. White paper on Industry 4.0, Join the Smart Revolution. Available online: https://www.displaytechnology.co.uk/assets/files/ industry\_4.0\_white\_paper.pdf (accessed on 19 April 2023).

- 12. Chu, P.P. FPGA Prototyping by Verilog Examples: Xilinx Spartan-3 Version; John Wiley & Sons: Hoboken, NJ, USA, 2011.

- 13. Kuhn, K.J.; Giles, M.D.; Becher, D.; Kolar, P.; Kornfeld, A.; Kotlyar, R.; Ma, S.T.; Maheshwari, A.; Mudanai, S. Process technology variation. *IEEE Trans. Electron. Devices* 2011, *58*, 2197–2208. [CrossRef]

- 14. Lewyn, L.L.; Ytterdal, T.; Wulff, C.; Martin, K. Analog circuit design in nanoscale CMOS technologies. *Proc. IEEE* 2009, 97, 1687–1714. [CrossRef]

- 15. Hiblot, G.; Liu, Y.; Van der Plas, G. Impact of packaging stress on thinned 6T SRAM die. *Int. J. Electron. Lett.* **2020**, *8*, 38–45. [CrossRef]

- 16. Semenov, O.; Vassighi, A.; Sachdev, M. Impact of self-heating effect on long-term reliability and performance degradation in CMOS circuits. *IEEE Trans. Device Mater. Reliab.* **2006**, *6*, 17–27. [CrossRef]

- 17. Sapatnekar, S.S. What happens when circuits grow old: Aging issues in CMOS design. In Proceedings of the 2013 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA). IEEE, Hsinchu, Taiwan, 22–24 April 2013; pp. 1–2.

- Yellepeddi, M.; Kelkar, A.; Waldrip, J. Analog Circuit Design Strategies for Reliability Tolerance: Planning for Reliability Effects While Designing Circuits in Modern CMOS Technologies. *IEEE Solid-State Circuits Mag.* 2020, 12, 79–85. [CrossRef]

- 19. Schaldenbrand, A. Analog Reliability Analysis for Mission-Critical Applications; White Paper; Cadence Design Systems, Inc.: San Jose, CA, USA, 2019.

- Li, X.; Taylor, B.; Chien, Y.; Pileggi, L.T. Adaptive post-silicon tuning for analog circuits: Concept, analysis and optimization. In Proceedings of the 2007 IEEE/ACM International Conference on Computer-Aided Design, IEEE, San Jose, CA, USA, 4–8 November 2007; pp. 450–457.

- 21. Du, D.; Odame, K.M. A bandwidth-adaptive preamplifier. IEEE J. Solid-State Circuits 2013, 48, 2142–2153.

- 22. Huang, Y.J.; Tzeng, T.H.; Lin, T.W.; Huang, C.W.; Yen, P.W.; Kuo, P.H.; Lin, C.T.; Lu, S.S. A self-powered CMOS reconfigurable multi-sensor SoC for biomedical applications. *IEEE J. Solid-State Circuits* **2014**, *49*, 851–866. [CrossRef]

- Thompson, A. An evolved circuit, intrinsic in silicon, entwined with physics. In Proceedings of the Evolvable Systems: From Biology to Hardware: First International Conference, ICES96 Tsukuba, Japan, 7–8 October 1996; Proceedings 1; pp. 390–405.

- 24. Abd, H.; König, A. Design of a CMOS memristor emulator-based, self-adaptive spiking analog-to-digital data conversion as the lowest level of a self-x hierarchy. *J. Sensors Sens. Syst.* **2022**, *11*, 233–262. [CrossRef]

- Tawdross, P.; Konig, A. Investigation of particle swarm optimization for dynamic reconfiguration of field-programmable analog circuits. In Proceedings of the Fifth International Conference on Hybrid Intelligent Systems (HIS'05), Rio de Janeiro, Brazil, 6–9 November 2005; p. 6.

- Shang, Q.; Chen, L.; Wang, D.; Tong, R.; Peng, P. Evolvable hardware design of digital circuits based on adaptive genetic algorithm. In Proceedings of the International Conference on Applications and Techniques in Cyber Intelligence ATCI 2019: Applications and Techniques in Cyber Intelligence 7, Huainan, China, 22–24 June 2019; pp. 791–800.

- Ramesham, R.; Kumar, N.; Mao, J.; Keymeulen, D.; Zebulum, R.S.; Stoica, A. Data converters performance at extreme temperatures. In Proceedings of the 2006 IEEE Aerospace Conference. IEEE, Big Sky, MT, USA, 4–11 March 2006; p. 12.

- Andraud, M.; Stratigopoulos, H.G.; Simeu, E. One-shot non-intrusive calibration against process variations for analog/rf circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 2022–2035. [CrossRef]

- In-Chip Monitoring and Sensing. Available online: https://www.synopsys.com/solutions/silicon-lifecycle-management/inchip-monitoring-and-sensing.html (accessed on 19 May 2022).

- Kashyap, R. Silicon lifecycle management (SLM) with in-chip monitoring. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–4. [CrossRef]

- Silicon Lifecycle Management: Actionable Silicon Insights Through Intelligent Measurement and Analysis. Available online: https://www.synopsys.com/solutions/silicon-lifecycle-management.html (accessed on 19 May 2022).

- Synopsys Expansion of Silicon Lifecycle Management Platform. Available online: https://www.eetasia.com/synopsys-acquiresmoortec-to-expand-silicon-lifecycle-management-platform/ (accessed on 19 May 2022).

- Variyam, P.N.; Cherubal, S.; Chatterjee, A. Prediction of analog performance parameters using fast transient testing. *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.* 2002, 21, 349–361. [CrossRef]

- 34. Stratigopoulos, H.G.; Mir, S. Adaptive alternate analog test. IEEE Des. Test Comput. 2012, 29, 71–79. [CrossRef]

- Andraud, M.; Verhelst, M. From on-chip self-healing to self-adaptivity in analog/RF ICs: challenges and opportunities. In Proceedings of the 2018 IEEE 24th International Symposium on On-Line Testing And Robust System Design (IOLTS), Platja d'Aro, Spain, 2–4 July 2018; pp. 131–134.

- Alraho, S.; Zaman, Q.; Abd, H.; König, A. Integrated Sensor Electronic Front-Ends with Self-X Capabilities. *Chips* 2022, 1, 83–120. [CrossRef]

- Zaman, Q.; Alraho, S.; König, A. Efficient transient testing procedure using a novel experience replay particle swarm optimizer for THD-based robust design and optimization of self-X sensory electronics in industry 4.0. *J. Sensors Sens. Syst.* 2021, 10, 193–206. [CrossRef]

- 38. Red Pitaya Doumentation. Available online: https://redpitaya.com/documentation/ (accessed on 23 April 2022).

- Stoica, A. Toward evolvable hardware chips: Experiments with a programmable transistor array. In Proceedings of the Proceedings of the Seventh International Conference on Microelectronics for Neural, Fuzzy and Bio-Inspired Systems, Granada, Spain, 9 April 1999; pp. 156–162. [CrossRef]

- 40. Tawdross, P.M.M. Bio-Inspired Circuit Sizing and Trimming Methods for Dynamically Reconfigurable Sensor Electronics in Industrial Embedded Systems. Doctoral Thesis, Technische Universität Kaiserslautern, Kaiserslautern, Germany, 2007.

- 41. Wu, R.; Huijsing, J.H.; Makinwa, K.A. *Precision Instrumentation Amplifiers and Read-Out Integrated Circuits*; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2012.

- 42. Han, K.; Kim, H.; Kim, J.; You, D.; Heo, H.; Kwon, Y.; Lee, J.; Ko, H. A 24.88 nV/Hz Wheatstone Bridge Readout Integrated Circuit with Chopper-Stabilized Multipath Operational Amplifier. *Appl. Sci.* 2020, *10*, 399. [CrossRef]

- 43. Fan, Q.; Makinwa, K.A.; Huijsing, J.H. Capacitively Coupled Chopper Instrumentation Amplifiers for Low-Voltage Applications. In *Capacitively-Coupled Chopper Amplifiers*; Springer: Berlin/Heidelberg, Germany, 2017; pp. 93–121.

- 44. Corbacho, I.; Carrillo, J.M.; Ausín, J.L.; Domínguez, M.Á.; Pérez-Aloe, R.; Duque-Carrillo, J.F. A Fully-Differential CMOS Instrumentation Amplifier for Bioimpedance-Based IoT Medical Devices. *J. Low Power Electron. Appl.* **2022**, *13*, 3. [CrossRef]

- 45. Brunner, E.; Gilbert, B. The active feedback amplifier. a versatile analog building block. In Proceedings of the NORTHCON'94, Seattle, WA, USA, 13 October 1994; pp. 131–136.

- Sackinger, E.; Guggenbuhl, W. A versatile building block: The CMOS differential difference amplifier. *IEEE J. Solid-State Circuits* 1987, 22, 287–294. [CrossRef]

- Matthus, C.D.; Buhr, S.; Kreißig, M.; Ellinger, F. High Gain and High Bandwidth Fully Differential Difference Amplifier as Current Sense Amplifier. *IEEE Trans. Instrum. Meas.* 2020, 70, 1–11. [CrossRef]

- 48. Pertijs, M.A.; Kindt, W.J. A 140 dB-CMRR current-feedback instrumentation amplifier employing ping-pong auto-zeroing and chopping. *IEEE J. Solid-State Circuits* 2010, 45, 2044–2056. [CrossRef]

- Choi, G.; Heo, H.; You, D.; Kim, H.; Nam, K.; Yoo, M.; Lee, S.; Ko, H. A Low-Power, Low-Noise, Resistive-Bridge Microsensor Readout Circuit with Chopper-Stabilized Recycling Folded Cascode Instrumentation Amplifier. *Appl. Sci.* 2021, 11, 7982. [CrossRef]

- Ng, K.A.; Chan, P.K. A CMOS analog front-end IC for portable EEG/ECG monitoring applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 2335–2347. [CrossRef]

- 51. Zuo, S.; Heidari, H.; Farina, D.; Nazarpour, K. Miniaturized magnetic sensors for implantable magnetomyography. *Adv. Mater. Technol.* **2020**, *5*, 2000185. [CrossRef]

- Alraho, S.; König, A. Wide input range, fully-differential indirect current feedback instrumentation amplifier for self-x sensory systems/Symmetrischer Instrumentierungsverstärker mit indirekter Stromgegenkopplung und hoher Eingangsignalspanne für integrierte Sensorsysteme mit Self-x-Eigenschaften. *Tm-Tech. Mess.* 2019, *86*, 62–66.

- Alzaher, H.; Ismail, M. A CMOS fully balanced differential difference amplifier and its applications. *IEEE Trans. Circuits Syst. II Analog Digit. Signal Process.* 2001, 48, 614–620. [CrossRef]

- 54. Valencia-Ponce, M.A.; Tlelo-Cuautle, E.; de la Fraga, L.G. On the sizing of CMOS operational amplifiers by applying manyobjective optimization algorithms. *Electronics* **2021**, *10*, 3148. [CrossRef]

- Circuit Sizing and Optimization Tools. Available online: https://www.muneda.com/circuit-sizing-and-optimization-tools/ (accessed on 23 April 2023).

- 56. Kammara, A.C.; Palanichamy, L.; König, A. Multi-objective optimization and visualization for analog design automation. *Complex Intell. Syst.* **2016**, *2*, 251–267. [CrossRef]

- 57. Alraho, S.; Zaman, Q.; König, A. Reconfigurable Wide Input Range, Fully-Differential Indirect Current-Feedback Instrumentation Amplifier with Digital Offset Calibration for Self-X Measurement Systems. *Tm-Tech. Mess.* **2020**, *87*, s85–s90. [CrossRef]

- Neag, M.; Kovács, I.; Oneţ, R.; Câmpanu, I. Design options for high-speed OA-based fully differential buffers able to drive large loads. *Microelectron. J.* 2021, 114, 105115. [CrossRef]

- 59. Hogervorst, R.; Tero, J.P.; Eschauzier, R.G.; Huijsing, J.H. A compact power-efficient 3 V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries. *IEEE J. Solid-State Circuits* **1994**, *29*, 1505–1513. [CrossRef]

- 60. Sanabria-Borbón, A.C.; Sánchez-Sinencio, E. Synthesis of High-Order Continuously Tunable Low-Pass Active-R Filters. *IEEE Trans. Circuits Syst. I: Regul. Pap.* 2021, *68*, 1841–1854. [CrossRef]

- 61. Instruments, Texas. *Simplifying Current Sensing: How to Design with Current Sense Amplifiers*; 2019. Available online: https://www. allaboutcircuits.com/industry-white-papers/simplifying-current-sensing-how-to-design-with-current-sense-amplifiers/ (accessed on 23 April 2023).

- 62. Cimino, M.; Lapuyade, H.; Deval, Y.; Taris, T.; Begueret, J.B. Design of a 0.9 V 2.45 GHz Self-Testable and Reliability-Enhanced CMOS LNA. *IEEE J. Solid-State Circuits* **2008**, *43*, 1187–1194. [CrossRef]

- Zaman, Q.; Alraho, S.; Koenig, A. Low-Cost Efficient Indirect Power Monitoring Method for Optimization of Reconfigurable Analog Readout Circuits with Self-X Capabilities. In Proceedings of the Sensors and Measuring Systems, 21th ITG/GMA-Symposium, Nuremberg, Germany, 10–11 May 2022; pp. 1–5.

- Shekhar, C.; Qureshi, S. Design and analysis of current starved vco targeting scl 180 nm cmos process. In Proceedings of the 2018 IEEE International Symposium on Smart Electronic Systems (iSES)(Formerly iNiS), Hyderabad, India, 17–19 December 2018; pp. 86–89.

- 65. Lin, L.J. Self-improving reactive agents based on reinforcement learning, planning and teaching. *Mach. Learn.* **1992**, *8*, 293–321. [CrossRef]

- 66. Schaul, T.; Quan, J.; Antonoglou, I.; Silver, D. Prioritized experience replay. arXiv 2015, arXiv:1511.05952.

- 67. Sutton, R.S.; Barto, A.G. Reinforcement Learning: An Introduction; MIT Press: Cambridge, MA, USA, 2018.

- 68. Paul, A.; Ramirez-Angulo, J.; Vázquez-Leal, H.; Huerta-Chua, J.; Diaz-Sanchez, A. Fully Differential Miller Op-Amp with Enhanced Large-and Small-Signal Figures of Merit. *J. Low Power Electron. Appl.* **2022**, *12*, 9. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.