# Article Data Verification in the Agent, Combining Blockchain and Quantum Keys by Means of Multiple-Valued Logic

Alexey Yu. Bykovsky \* and Nikolay A. Vasiliev

P.N. Lebedev Physical Institute RAS, Leninsky pr. 53, 119991 Moscow, Russia \* Correspondence: bykovskiyay@lebedev.ru

**Abstract**: Network control of autonomous robotic devices involves a vast number of secured data coding, verification, and identification procedures to provide reliable work of distant agents. Blockchain scheme provides here the model of the extended linked list for the verification of critical data, approved by quasi-random hash values assigned by external network nodes. And quantum lines are the source of high-quality quasi-random keys used as hash values. Discrete multiple-valued logic in such procedures is a simple and flexible tool to form the logic linked list, combining critical internal parameters of agents with data taken from external nodes. Such combination enlarges the set of possible schemes for data protection from illegal modifications and for data restoration.

Keywords: data verification; agent; multiple-valued logic; blockchain; linked list; quantum key

# 1. Introduction

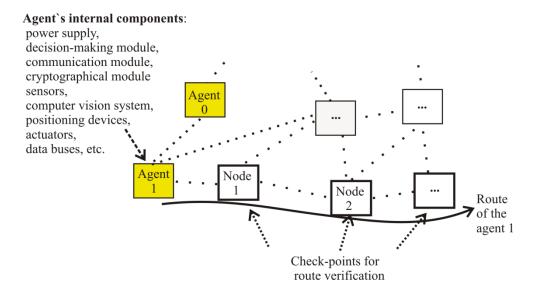

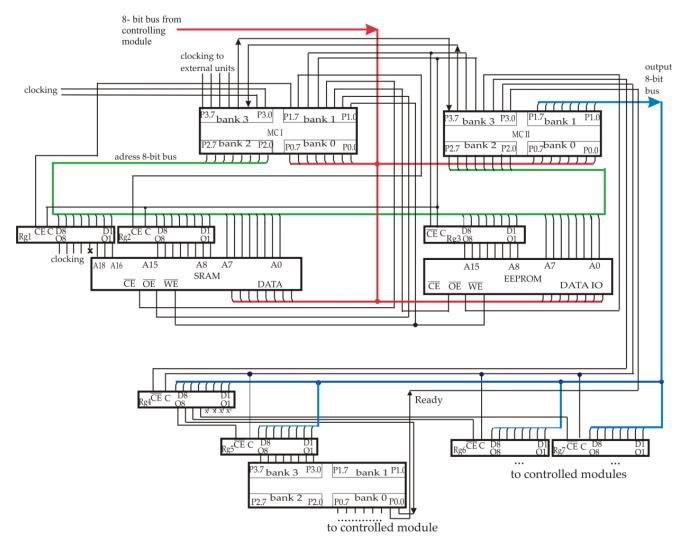

Modern concepts of communication networks include such collective robotic components as autonomous vehicles (or Internet of Vehicles, IoV) [1,2], logistics [3], industrial machinery [4], and Internet of Things (IoT) [5,6]. As autonomous agents are based on traditional microprocessors and embedded platforms [7], then attacks of eavesdroppers are quite possible and efficient distant monitoring plays critical role. Discussions of possible methods for distant data verification has included special network protocols for mobile agents [8-10], quantum cryptography [11,12], schemes of distributed computing [13], blockchain (BC) methods [14–16], position-based cryptography [17], and non-binary k-valued discrete logic [18]. Interest to blockchain technologies for network agents can be attributed to the problem of low availability of trusted network nodes for mass robotics, as trusted systems for communication networks discussed e.g., in [19] need special equipment, personnel, and intensive monitoring procedures. At the same time, the integration of fiber-optics and wireless quantum key distribution (QKD) lines [12,20] in communication networks provides new possibilities to raise security, although QKD is a complicated and expensive tool, which has its specific vulnerabilities and can be suppressed by intensive optical noise. QKD schemes and quantum random number generators (QRNG) [21] are the high quality sources of one-time quasi-random keys, which provide the base for various data protection schemes. That is why they are also expected to raise the security level of autonomous robotic systems based on artificial intellect (AI) methods [22], which are strongly associated with the concept of collectives of intellectual agents or multi-agent systems (MAS) [23]. In Figure 1 a local network of hardware agents 0, 1, . . . is a part of nodes of the communication network, and can include mobile and static agents. As autonomous agents should be able to work without permanent personnel control due to the imitation of human abilities by means of AI algorithms [19], various verification procedures are quite actual for them, including schemes based on BC [24–26]. However, data protection of internal subsystems in autonomous agents is a separate problem, as an agent, see Figure 1 to the left, may include subsystems with different throughput, software and hardware complexity [27]. As a result, hardware platform for autonomous agents can be very complicated [27,28], and model debugging and data verification is the difficult problem.

Citation: Bykovsky, A.Y.; Vasiliev, N.A. Data Verification in the Agent, Combining Blockchain and Quantum Keys by Means of Multiple-Valued Logic. *Appl. Syst. Innov.* **2023**, *6*, 51. https://doi.org/10.3390/asi6020051

Academic Editor: Subhas Mukhopadhyay

Received: 6 March 2023 Revised: 25 March 2023 Accepted: 28 March 2023 Published: 6 April 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

**Figure 1.** Communication network includes usual stationary nodes and autonomous mobile robotic agents 0, 1, . . . , which are the participants of a multi-agent system (MAS) and can follow some given route like agent 1. Nodes called checkpoints are to approve identity of the mobile agent and to give access to a requested service. Such nodes optionally may be participants of the trusted local network.

For the position–based cryptography task [17] and agents following the given route, verification procedures [29] should combine authentication, identification and secret coding. It is necessary to check identity and access rights of the mobile agent by verification of parols, pin-codes, licenses, digital images, and prehistory of carried out agent's tasks, what involves either the design of trusted check-points [29] or needs the estimation of trust models [30,31]. Besides this, schemes based on BC principles [32–34] were already designed for the collective verification of data in energy power networks, as static network agents of dishonest users can declare false data.

#### 1.1. Modern Platforms for Robotics Positioning and Communications

Localization or positioning was considered in reviews [35,36] as a process to obtain tracked objects information concerning multiple reference points within a predetermined area, i.e., it is a procedure to identify the position of mobile/fixed devices, including smartphones, drones, watch, beacons, and vehicles using some fixed nodes and mobile computing devices. Global navigation satellite system (GNSS) in such tasks can use signals produced by global positioning system (GPS), global navigation satellite system (GLONASS), Galileo and Beidou. As the GPS device loses substantial power in an indoor setting due to signal attenuation, such systems cannot be used for indoor localization of devices. Alternative possibilities refer to ZigBee, Bluetooth, Radio Frequency Identification (RFID), cellular networks (including LTE and 5G), ultrawideband (UWB), frequency modulation (FM), inertial sensors and Wi-Fi. Some hybrid approaches are also possible. Most common techniques for localization include time-of-flight (TOF) measurements and received signal strength indicator (RSSI) signal measurements, utilizing the distance between known fixed stations and the target device, or fingerprint-based location estimation.

Vehicular ad-hoc network (VANET) [37] was based on the link-layer communication (IEEE 802.11p) and has included the data exchange between the high-speed vehicles in the licensed band of 5.9 GHz (5.850–5.925 GHz). VANET differs from other ad-hoc networks by high mobility, dynamic topology, frequent data exchange, unbounded network size, unlimited battery power, and predictable movement (which happens only on the road). It may use two types of nodes: (1) mobile nodes attached to onboard units, and (2) static nodes like traffic lamp posts, signboards, and roadside units. This network of mobile agents has provided connections vehicle-to-vehicle, vehicle-to-infrastructure, and infrastructure-to-

infrastructure. Used performance metrics were hop length, minimum energy, link lifetime, route breakage, and bandwidth.

Very actively investigated field of autonomous robotics refers to flying unmanned aerial systems (UAVs). The authors of the review [38] have analyzed flying ad-hoc networks (FANETs), which can be deployed either individually or may be incorporated into traditional wireless local area networks (WLANs). Its main application fields include search and rescue, mailing and delivery, traffic monitoring, precision agriculture, and surveillance applications. Unmanned service of FANETs is actual in case of natural disasters, hazardous gas intrusions, wildfires, avalanches, and search of missing persons. As routing is the most challenging job in FANETs due to such attributes of UAVs, as high mobility, 3D movement, and rapid topology changes, then a predictive method should be used for path planning and navigation in order to prevent possible collisions and to ensure the safety of the FANET. However, the data aggregated by a small UAV can be too large to be processed and stored onboard [39]. Small UAVs in FANETs also suffer from security vulnerabilities, as their limited storage and computing capabilities do not allow to perform computational-intensive tasks locally [40,41]. An intruder intending to attack the network UAV [38] can transmit massive reservation requests, eavesdrop instructions, and modify the information. UAVs connected to Wi-Fi are considered as less secured in comparison with cellular networks, due to unreliable links and poor security methods. False transmitter can be attached to a UAV and may send fake instructions, in addition to this UAVs can become a luring target for physical attacks [39,41]. In such instances, an attacker can dissemble the captured UAV to get access to internal data via interfaces and USB ports.

GPS spoofing, see e.g., [38] is another major security threat for small UAVs. An adversary can transmit fake GPS signals to an intended UAV with enlarged power than the actual GPS signals. Thus, localization system must verify actual positions of neighboring UAVs and associated distances in order to avoid the GPS spoofing attacks.

The detection and identification of vulnerabilities for UAVs refers to popular shortrange wireless networking technologies like Wi-Fi (IEEE 802.11), ZigBee (IEEE 802.15.4), Bluetooth (IEEE 802.15.1), LoRaWAN, and Sigfox [38,42], differing by the range and the throughput for licensed or unlicensed spectrum types. Wi-Fi provides a set of specifications for radio bands of 2.4, 3.6, 5, and 60 GHz. IEEE 802.11a/b/g/n/ac is the first choice to provide the transmission of medium size video and images for distances of approximately 100 m, but unlicensed versions can provide up to few hundred meters. A multi-hop networking scheme may expand the transmission range to kilometers. An alternative to Wi-Fi is the use of low-cost and low-power methods like Bluetooth and ZigBee. Bluetooth (IEE 802.15.1) is a low cost and low power variant, which operates in an unlicensed band of 2.4 GHz with a contact range of 10 to 100 m and uses a distributed frequency-hopping transmission spectrum.

Licensed 5G and 6G generation technologies are expected [38] to offer improved data rates and coverages in linking of FANETs, to provide high device mobility and integration of a massive number of UAVs in an ultra-reliable way, to serve multi-access edge computing, and to incorporate cloud computing. Low-power wide area networks (LPWAN) can be another good option for UAVs which consumes less energy and offers a wide range of connectivity. LPWAN allows transmitting data for a longer duration of time and without much loss of energy resources. For IoT users, LoRaWAN [43] has been designed as a technology for the management of low energy consumption transmissions, using a novel network paradigm for bidirectional connectivity, localization, and mobility management. It provides a new framework for LPWAN execution, providing long-range communications in the band 868/900 MHz with data rates ranging from 0.3 kbps to 50 kbps and network coverage from 5 to 15 km. Sigfox, similar to LoRaWAN, is a low-speed, but low-power and long-range solution for UAVs, it supports open-sight up to 30 km of range in the same band as LoRaWAN.

Another modern trend for enhancement of data privacy and integrity in UAV communication networks is the aerial blockchain, especially supported by 5G and 6G [38,44]. Blockchain-based software for UAV is expected to provide flexibility, dynamics, and onthe-fly decision capabilities. UAVs can be integrated potentially into the Internet network, providing access to cloud computing and web technologies for the realization of smart IoT systems.

#### 1.2. Blockchain-Based Verification Schemes for Network Agents

Principally, methods of data verification for agents and MAS can include various traditional technologies [12], including parity bits checking, cryptography algorithms and biometrics, as well as exhausted methods of model checking [45], temporal logic and Kripke diagrams [46,47]. Unfortunately, known BC schemes [14,16,32] designed for crypto currencies mining scarcely can be directly used for data protection of robotic agents and their internal subsystems, mainly due to energy expenses, high cost, limited throughput of microprocessors, and incompatibility of specialized technical tasks of robots with basic Proof-of-Work and less expensive Proof-of-Sake schemes [48,49]. Respectively, the design of secured and reliable agent's devices for mass robotics, IoT, and IoV stimulates the search of more simple and flexible verification schemes for distant monitoring of static and mobile agent's behavior. It is substantial, that BC-based schemes for trust parameters estimation of stationary agents in power grid networks [32–34] has already demonstrated the effectiveness of collective detection of dishonest user's nodes by means of polling of neighboring nodes and evaluation of the trust parameters by collaborating network nodes.

#### 1.3. Multiple-Valued Logic for Data Verification Based on Blockchain Scheme

Multiple-valued logic (MVL) version of the linked list [19] has used partially the BC scheme [14–16,32–34,48,49] and was aimed at data verification in case of faults. Such method bases on original property of *k*-valued Allen-Givone algebra (AGA) [50] to aggregate correctly arbitrary variables into logic functions, to form logic linked lists of entries, and to obtain protective logic expressions, preventing from illegal modification of logic product terms. It is substantial, that MVL-based linked list (MVLL) [19] can also model quantum verification protocol of position-based cryptography [51], thus demonstrating the possibility to combine quantum and classic verification procedures. Further research of AGA model [19,29] was also motivated by some earlier papers like [52,53] and e.g., by MVL scheme [54] based on lattice models and the theory of sets.

MVLL [19] is the model for distributed or collective data storage of entries  $e = \{e_1, \ldots, e_p\}$ , containing sets of p critical parameters of the mobile or the stationary agent, verified by collaborating agents and network nodes, participating in the collective protocol. Here the difference between collaborating agents and nodes mainly refers to levels of trust assigned to interacting devices. e.g., for route verification task trusted check points always should be assigned the highest trust and priority level, as other collaborating network nodes are motivated to take part in the joint protocol by mutual service or fee, and should be appreciated by lower trust values. But before the detailed design of trust estimation schemes for mobile robots one should work out adequate verification procedures involving all possible resources of agents and network nodes.

#### 1.4. Internal and External Data Verification Procedures of the Network Agent

Distant control of autonomous robotic agents involves at least two types of tasks greatly differing by the time response. Such basic AI tasks as e.g., logistics, building work, following the route, interaction with check-points, takes long time intervals (days, weeks, months etc.) and the time moment for the end of task can't always be predicted precisely. Also verification procedures for digital licenses and documents may be requested optionally by other participants of the network. In contrast to this, the second type of control processes refers to internal systems of the agent, which typically use rigid short time work cycles ( $\mu$ s, ms, s) [55] for control of numerous sensors and actuators. Thus, complex data verification procedure of the autonomous agent should include both types of time processes. In order to make verification data unpredictable for possible eavesdroppers, verified parameters

should be masked or even secretly coded by one-time quasi-random keys, traditionally used in the most reliable one-time cipher pad method of secret coding [56], which is the final aim of any QKD line realization [12]. For internal systems such quasi-random codes also can be done one-time and actual only for short time intervals, i.e., they should be renewed for a selected or every new work cycle. Then quasi-random keys are preferably to be generated by either a QKD line [20], or by a quantum random number generator (QRNG) [21] and random oracle [57] for simplified and less protected variants. Used for verification hash values from external and internal components of the agent are to be mixed with technical parameters written in the distributed linked list. But in contrast to blockchain schemes in cryptocurrency mining [25,26,48,49] and software bots for stock trading [58], autonomous hardware robots can provide very limited resources for additional verification as they are initially intended to carry out highly specialized work. Thus, the possibility of data verification inside the agent strongly depends on its internal structure of subsystems, whose most typical examples are listed in Figure 1 to the left. Here the simple way to unite various internal and external verification schemes in one agent seems to be based on the earlier proposed MVLL model of the distributed ledger or the linked list [19], which is to be additionally approved by some internal and external technical parameters besides externally assigned hash values.

#### 1.5. Possible Sources of Quasi-Random Keys for Hashing Procedures

As any computerized device the distant autonomous agent can be damaged by a physical impact on its embedded computer, or can be infected by a computer virus [12]; possible attacks [59,60] can be also aimed at internal data buses, memory and service devices. These hardships makes actual involvement of QKD lines, as the interest to quantum keys for wireless network robotics bases on the principles of modern cryptography, according to which the well-known Vernam code or close to it one-time cipher pad method [56] with random one-time keys is the most reliable cryptography scheme. Due to the non-cloning theorem [61] QKD lines are in fact the way to exclude long-range distant storage of secret keys by means of their quick enough generation for every new communication session. But as the throughput of quantum lines is not enough for massive stream secret coding, and its length is limited by  $\sim 100$  km [12], this method has now mainly nice applications, its drawbacks are the high cost and the possibility of suppression by intensive noise, what is especially actual for wireless robotics communications. Also QKD line itself can be vulnerable to some specific types of quantum and classical attacks [12], and the access of non-loyal personnel to agent's equipment can cause data leakages. Besides this, attempts to design purely quantum verification schemes for position-based cryptography in mobile systems [17,62] has given only partial improvement and unconditional security was not still obtained, as well as quantum bit commitment schemes still were not realized. Also it is the too expensive and complicated tool to be used in internal data buses in the agent. However, the research of QKD lines [20] has drawn conjugated investigations of quantum random number generators (QRNG) [21] and the position-based cryptography (PBC) scheme [57], involving random oracle model [17] based on memory device and MVL function learned by a QRNG. Such method was adapted for the verification of visits of mobile agents to check-points, conjugated with the quantum protocol by D. Unruh [51] using entangled photon pairs. The principal possibility to apply random oracle as a more simple alternative source of quasi-random keys for MVLL is a way to design new verification procedures and to avoid partially the use of trusted checkpoints. However, before the design of future schemes to estimate the trust level of mobile agents and static check-points, one should work out effective non-quantum methods to keep reliably critical data in distant agents and consequently to verify data written in them, as well as to check prehistory of agent's work activity and passed routes.

#### 1.6. Heterogeneous Logic Models in Modern Controllers

The motive to apply heterogeneous logic models in the agent [18,19] and to combine Boolean and MVL logic in it is determined by the fact, that verification procedures in a robotic agent refers not only to PC's microprocessors, but also to controller devices based on the closed loop control and equipped with own microprocessors [55] with lower throughput. Traditional types of such devices are mostly represented by proportional-integraldifferential (PID) [63] and fuzzy logic controllers [64–66]. However, modern investigations reveal the stable trend to further integration of PID and fuzzy logic in controllers, see e.g., [64]; respectively, this paper has demonstrated the actuality of heterogeneous logic models not only for agents level [18], but also for the level of internal controllers. The socalled fuzzy-fractional order-proportional-integral-differential controller (FFOPID) in [64] has provided improved non-linear characteristics modelled by non-linear polynomials. Fuzzy logic in this FFOPID scheme has provided fast approximate computing and simple learning of the system, but has needed correct emulation of specific operators of the fuzzy logic.

#### 1.7. The Goal of the Paper

The final goal of the proposed further extended version of the MVLL [19] is to combine more complicated and intellectual robotic data procession procedures with BC-based schemes, secured from illegal modifications and capable for self-checks and self-restoration in case of fails and faults. The scheme disclosed in this paper is the step to approve critical task parameters and control signals of internal subsystems of the agent by external network nodes. Such distributed storage of verification data is necessary in cases, when data taken from different sources contradict each other and need detailed verification. Then the sequential matching of data copies extracted from external and internal backups can help to restore reliable work and avoid blocking of the robot.

The aim of the proposed paper is to design the new data verification scheme for mobile agents, complementing earlier proposed version of the MVLL by the documented data exchange between external nodes and internal data storages. The expected advantage here is the diversity of verification methods in case of faults and errors.

#### 2. Methods: MVL Linked List as the Data Protection Model

MVLL method [19] bases on discrete -valued logic and partially uses the idea of mixing data blocks in BC schemes by combining quasi-random hash values with real values of variables in the last and in one of previously formed entries.

#### 2.1. Logic Functions of the Multiple-Valued Allen-Givone Algebra

Detailed description of basic calculations within discrete *k*-valued Allen-Givone algebra (AGA) [50] was given in, e.g., [18,19]. The choice of this version of logic calculus was determined by the simplicity of its basic operators and the flexibility of design of multiparametrical functions. In contrast to binary Boolean logic, AGA function  $y = f(x_1, ..., x_n)$  can be given by *n* input variables  $x_1, ..., x_n$  and one output variable *y*, which may be assigned *k* discrete truth levels, i.e.,  $x_1, x_2, ..., x_n, y$   $L = \{0, 1, ..., k-1\}$ . The complete set of its logic operators [50]

$$< 0, 1, \dots, k-1, X(a,b), \star, +>$$

(1)

guarantees the possibility to represent arbitrary function  $y = f(x_1, ..., x_n)$  as some combination of logic constants 0, 1, ..., k - 1, binary operators  $Min(x_i, x_j)$  marked by ( $\star$ ) and  $Max(x_i, x_j)$  marked by (+); also unary operator X(a, b) is being used, which is called Literal. Operators Min and Max, respectively, choose either the minimal value in the pair  $x_i$  and  $x_j$ , or the maximal one. Literal is defined as Exp. (2)

$$X(a,b) = \begin{cases} 0, & if \ b < x < a \\ k - 1, if \ a \le x \le b \end{cases}$$

(2)

where for any X(a, b) always  $b \ge a$ , and  $a, b \in L = \{0, 1, \dots, k-1\}$ .

For verification procedures the advantage of AGA [18,19] is namely the guaranteed possibility to obtain correct logic expression for arbitrarily given data, where the only possible algorithm for calculation of MVL functions excludes alternative illegal procedures for eavesdroppers. The drawback of such functions is some unpredictability of calculation time for unknown sets of data, as the minimization for MVL is very wasteful [50].

MVL truth table [50], see Table 1, partially resembles the Boolean ones, but contains much more rows whose number attains  $k^n - 1$ , where k—is the number of discrete logic levels, and n is the number of input variables. If one has composed MVL truth table, then every its row has equivalent logic expression written to the right of Table 1. The column for output variable  $F(x_1, ..., x_n)$  should be arbitrarily filled in by logic constants from the set  $C = \{0, 1, ..., k - 1\}$ . Respectively, if constant F is 0, then the product term of this row is also equal to 0. Note that Literal operators to the right to Table 1 includes equal values a and b.

**Table 1.** Truth table of a AGA function. Equivalent product term for every row with nonzero output value ) is given to the right.

|             | Input Variables                                      |     |       |                    |                           | Output Variable               |                                                                                  |  |

|-------------|------------------------------------------------------|-----|-------|--------------------|---------------------------|-------------------------------|----------------------------------------------------------------------------------|--|

| INrow       | N <sub>row</sub> $x_1$ $x_2$ $\dots$ $x_{n-1}$ $x_n$ |     | $x_n$ | $F(x_1\ldots x_n)$ | Equivalent Product Terms: |                               |                                                                                  |  |

| 0           | 0                                                    | 0   |       | 0                  | 0                         | F(0, 0,, 0)                   | $F(0,0,\ldots,0) \star X_1(0,0) \star X_2(0,0) \star \ldots \star X_n(0,0)$      |  |

| 1           | 1                                                    | 0   |       | 0                  | 0                         | $F(1,0,\ldots,0) \rightarrow$ | $F(1,0,\ldots,0) \star X_1(1,1) \star X_2(0,0) \star \ldots \star X_n(0,0)$      |  |

|             |                                                      |     |       |                    |                           |                               |                                                                                  |  |

| $k^{n} - 1$ | k-1                                                  | k-1 |       | k-1                | k-1                       | $F(k-1,\ldots,k-1)$           | $F(k-1,k-1,,k-1) \star X_1(k-1,k-1) \star X_2(k-1,k-1) \star \star X_n(k-1,k-1)$ |  |

Resulting Exp. (3) can be written as:

$$F(x_1, \dots, x_n) = F(0, 0, \dots, 0) \star X_1(0, 0) \star \dots \star X_n(0, 0) + F(0, 0, \dots, 1) \star X_1(1, 1) \star \dots \star X_n(0, 0) + F(k-1, k-1, \dots, k-1) \star X_1(k-1, k-1) \star \dots \star X_{in}(k-1, k-1).$$

(3)

MVL minimization procedure by means of consensus method [40] involves transformation of parameters (a, b) in Literals and can shorten the number of product terms, but it is a wasteful enough procedure, which bases on the subsuming of product terms and the method of "don't care states" [50]. One can find its detailes in [18].

If one use equivalent matrix representation of MVL function [29], which was formed by data taken from the truth table (Table 1), then matrix C in exp. (4) will have only one-column, and exp. (3) can be written as arrays

$$A = \begin{pmatrix} a_{11} & \dots & a_{1n} \\ \dots & \dots & \dots \\ a_{k^n - 1, 1} & \dots & a_{k^n - 1, n} \end{pmatrix}, B = \begin{pmatrix} b_{11} & \dots & b_{1n} \\ \dots & \dots & \dots \\ b_{k^n - 1, 1} & \dots & b_{k^n - 1, n} \end{pmatrix}, C = \begin{pmatrix} F(0, \dots, 0) \\ \dots \\ F(k - 1, \dots, k - 1) \end{pmatrix},$$

(4)

where  $b_{ij} \ge a_{ij}$ , *n*—the number of input variables, *k*—the number of truth levels. Matrixes  $A_u$  and  $B_u$  in Exp. (4) define parameters *a* and *b* in Literals  $X_j(a, b)$ . Due to very large possible number of rows in the MVL truth table [50], the real system scarcely can use all possible  $k^n$  rows.

As MVL minimization by consensus method [50] for composed MVL function can shorten the number of product terms and change parameters in matrixes A,B,C, it can hide illegal modifications done in memory. In any way, all possible transformations of AGA expressions are based on the subsuming property of MVL product terms [50].

**Definition 1,** cited from [50]. *Product term*  $r_1 \star X_1(a_1, b_1) \star \ldots \star X_n(a_n, b_n)$  subsumes another product term  $r_2 \star X_1(c_1, d_1) \star \ldots \star X_n(c_n, d_n)$ , if and only if conditions (1) and (2) are true:

(1)  $r_1 \leq r_2$ ,

(2)  $c_i \leq a_i \leq b_i \leq d_i$  for  $all X_i, i = 1, ..., n$ .

For examplelogic expression taken for k = 256 truth levels  $-57 * X_1(24,24) * X_2(127,1275) * X_3(317, 331) +$  $+80 * X_1(24,24) * X_2(1275,1275) * X_3(317, 331) =$

$= 80 * X_1(2, 24) * X_2(1275, 1290) * X_3(317, 331)$  contains three product terms with constants 57, 80. As according to condition (1) in Definition 1 relation 57  $\leq$  80 is true, and according to condition (2)  $c_i = a_i \leq b_i = d_i$  for all  $X_i$ , i = 1, 2, 3, respectively the first product term (shown above) will subsume the second one and can be crossed out. That is why data protection for AGA model need monitoring of the number of product terms and values of parameters in matrixes A, B, C.

#### 2.2. Possible Attacks Aimed at MVL Product Terms and the Role of Subsuming

As cheaters potentially can modify AGA formalisms written in the memory of the agent, then all possible illegal modifications of MVL function are grouped in Table 2.

Table 2. Possible attacks aimed at MVL functions. (Abbrev. PT-tags product term).

| N  | Attack Type                                                                                        | Consequences, Scheme of Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|    |                                                                                                    | (1) If $C^* \ge C$ (e.g., $38 > 12$ ), then<br>$PT_{real} + PT_{fake} = \frac{12 * X_1(2,4) * X_2(75,175) * X_3(31, 34)}{12 + 38 * X_1(2,4) * X_2(75,175) * X_3(31, 34)}$ .                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 1. | Adding of one new PT with<br>fake logic constant C* and<br>previously used real                    | Result: Subsuming of the real PT by the fake one and incorrect logic values for real data of variables $x_1$ , $x_2$ , $x_3$ .<br>Protection: Monitoring of the set of logic constants C for all PTs.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|    | parameters <i>a</i> , <i>b</i> .                                                                   | (2) If $C^* < C$ ( <i>e.g.</i> , 11 < 12), then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|    | 1                                                                                                  | $PT_{real} + PT_{fake} = 12 * X_1(2,4) * X_2(75,175) * X_3(31,34) +$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|    |                                                                                                    | $+11 * X_1(2,4) * X_2(75,175) * X_3(31, 34).$<br>Result: Guaranteed subsuming of the fake PT by the real one. No danger!                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 2. | Adding of one new product<br>term (PT) with real constant<br>C and fake parameters<br>$a^*, b^*$ . | <ul> <li>PT<sub>real</sub> + PT<sub>fake</sub> = 12 * X<sub>1</sub>(2,4) * X<sub>2</sub>(75,175) * X<sub>3</sub>(31, 34) + +12 * X<sub>1</sub>(2,6) * X<sub>2</sub>(75,177) * X<sub>3</sub>(31, 36).</li> <li>Result: Subsuming of the real PT by the fake one, logic value 12 will be incorrectly assigned to the widened set of values for variables x<sub>1</sub>, x<sub>2</sub>, x<sub>3</sub>, but not only to real ones. Protection:</li> <li>Method of blocking logic terms [19] for a*, b* beyond the real band.</li> <li>Monitoring of a set of of real parameters a, b.</li> </ul> |  |  |  |

| 3. | Adding of one new product term with fake logic constant <i>C</i> and fake values $a^*, b^*$ .      | <ul> <li>Result: Simultaneous impact of NNs 1 and 2 given above.</li> <li>Protection:</li> <li>1. Method of blocking logic terms for <i>a</i>*, <i>b</i>* beyond the real band.</li> <li>2. Monitoring of sets of real logic constants C and parameters a,b.</li> </ul>                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 4. | Deleting of the PT, i.e.,<br>replacement of the logic<br>constant <i>C</i> by $C^* = 0$ in PT.     | Result: Deleting of the whole PT will cause the change in the overall number $N_{pt}$ of PTs in the MVL function.<br>Protection: Monitoring of numbers: <i>m</i> of product terms, real logic constants C, and parameters <i>a</i> , <i>b</i> .                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Ν  | Attack Type                                                                                                          | Consequences, Scheme of Protection                                                                                                                                                                                                  |

|----|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5. | Replacement of the logic constant <i>C</i> by fake $C^* \neq 0$ in some PT, parameters <i>a</i> , <i>b</i> are real. | Result: Values of fake C <sup>*</sup> are assigned to correct values of a,b:<br>$PT_{fake} = C^* * X_1(2,4) * X_2(75,77) * X_3(31, 34).$<br>Protection: Monitoring of sets of real constants C and parameters <i>a</i> , <i>b</i> . |

| 6. | Replacement of real $a$ , $b$ by fake ones $a^*$ , $b^*$ in Literals $X_i(a, b)$ of one PT.                          | Result: Incorrect values of C are assigned to fake values.<br>Possible protection: Method of blocking logic terms for $a^*$ , $b^*$ beyond the real band.                                                                           |

Product terms, subsumed after possible attacks are shown crossed out in Table 2. The analysis of given schemes of attacks aimed at MVL formal expressions shows the necessity to combine at least two basic schemes for data protection. Three types of attacks (NNs 2,3,6 in the Table 2) can be protected by the earlier proposed method of blocking product terms [19], describing all possible intermediate rows of the truth table located between two given rows. However, other types of attacks 1,4,5 need methods to monitor integrity of parameters of MVL functions. But here MVL version of BC-based schemes gives the method to form the protected from modifications linked list with confirmation by distributed external and internal parameters. Advantage of AGA functions calculations is that they are based on logic primitives and always use the only possible algorithm, thus they has no specific vulnerabilities for traditional attacks [12,18,19].

#### 2.3. MVL Scheme of the Linked List

Principally, initial MVLL scheme [19] includes two protective tools:

(1) duplicating notation of the same message in the last and in the previous entries like in BC schemes [25,26], and (2) the approval of data by quasi–random values of the hash function, assigned by the set of external distant nodes. Any attempt to modify data in the MVLL will need to modify at least two rows in the truth table of the linked list, approved before by two sets of externally assigned hash values. That is why the first way to use MVLL is to detect attacks 1,4,5 in Table 2 by comparison of entries, written in internal and different external parts of the linked list. The second way is to use blocking terms [19] preventing from 2,3,6, types of attacks.

In order to write the new entry *e* to MVLL [19], the mobile agent (called the prover in route verification tasks [41]) declares the new entry to *Q* collaborating nodes (or verifiers) by sequential mailing according to the list of participants of the protocol. First of them assigns the time stamp *t*, and each of verifiers should assign its quasi-random hash value *h* to the received entry *e*. These hash values are to be preliminary generated by QKD lines and accumulated in nodes in order to provide maximal unpredictability of data. One of assigned hash values should be used as the output value of the MVLL function, confirming every entry in the MVLL. After the acquisition of external hash values, mobile agent sends the complete set of data *m*, *t*,  $e_m = \{e_{1,m}, \ldots, e_{n,m}\}$ , and  $h = \{h_1, \ldots, h_Q\}$  to external participants (i.e., "witnesses") for their backup storage copies, formed individually according to known common rules. The absence of the verifier's reply due to faults and switched–off mode is to be fixed by zero.

In general case one can form the linked list function  $F_{ll}$  [19] by product terms, containing pairs of entries obtained at different time moments  $t_m$  and  $t_{m-s}$ , where *m* is the number of the last entry; *s* is the shift of the number for the previous entry. Function  $F_{ll}$  responds to Definition 1 and Exp. (5).

**Definition 2.** cited from [19]. Logic ledger function or a linked list of logic entries is given within AGA as a hash function

$$h^{(out)} = F_{ll}(m,s, t, e_{1,m}, \dots, e_{p,m}, e_{1,m-s}, \dots, e_{p,m-s}, h_{1,m}, \dots, h_{Q,m}, h_{1,m-s}, \dots, h_{Q,m-s}),$$

(5)

or in the compact notation  $h^{(m,s)} = F_{ll}(m, s, t, e_m, e_{m-s}, h_m, h_{m-s})$ .

In Exp. (5) *m* is the number of the last entry; *s* is the shift of the number for the previous entry; *t* is the time stamp corresponding to the last entry;  $e_{1,m}, \ldots, e_{p,m}$  are the parameters of the last entry  $e_m$ ;  $e_{1,m-s}, \ldots, e_{p,m-s}$  refer to parameters of the earlier received entry  $e_{m-s}$ ;  $h_{1,m}, \ldots, h_{Q,m}$  are the hash values assigned by network verifiers to the last entry  $e_m$ ;  $h_{1,m-s}, \ldots, h_{Q,m-s}$  are the hash values of the earlier received entry  $e_{m-s}$ ; and *q* is the number of a verifier,  $q = 1, \ldots, Q$ . All these parameters are natural numbers. For simplicity, in [19] MVLL has used only the shift s = 1. Respectively, the truth table for MVLL can be given by Table 3.

**Table 3.** Truth table of the MVLL hash function  $h^{(out)} = F_{ll}(\mathbf{m}, \mathbf{t}, \mathbf{e_m}, \mathbf{e_{m-1}}, \mathbf{h_m}, \mathbf{h_{m-1}})$  contains the newcomer entry  $\mathbf{e_m} = (\mathbf{e_{1,m}}, \dots, \mathbf{e_{p,m}})$ , previous entry is  $\mathbf{e_{m-1}} = (\mathbf{e_{1,m-1}}, \dots, \mathbf{e_{p,m-1}})$ , and their sets of hash values  $\mathbf{h_m} = (\mathbf{h_{1,m}}, \dots, \mathbf{h_{Q,m}})$  and  $\mathbf{h_{m-1}} = (\mathbf{h_{1,m-1}}, \dots, \mathbf{h_{Q,m-1}})$ , attributed to time moments  $t_m$  and  $t_{m-1}$ .

|              |                                        |                                            |                  |                  |                         | Input | Variable                                    | s                                |                                              |                           |                                                                | Output                   |

|--------------|----------------------------------------|--------------------------------------------|------------------|------------------|-------------------------|-------|---------------------------------------------|----------------------------------|----------------------------------------------|---------------------------|----------------------------------------------------------------|--------------------------|

| n            | t                                      | <b>e</b> <sub>1,t</sub>                    |                  | e <sub>p,t</sub> | <b>h</b> <sub>1,t</sub> |       | h <sub>q,t</sub>                            | <b>e</b> <sub>1,<i>t</i>-1</sub> | <br>$e_{p,t-1}$                              | <b>h</b> <sub>1,t-1</sub> | <br>$\mathbf{h}_{\mathbf{q},t-1}$                              | h <sup>(out)</sup>       |

| 1            | $t_1$                                  | e <sub>1,1</sub>                           |                  | e <sub>p,1</sub> | h <sub>1,1</sub>        |       | h <sub>Q,1</sub>                            | e <sub>1,0</sub>                 | e <sub>p,0</sub>                             | h <sub>1,0</sub>          | <br>h <sub>Q,0</sub>                                           | h <sup>(1,1)</sup>       |

| <br>m-1<br>m | <br>t <sub>m-1</sub><br>t <sub>m</sub> | <br>e <sub>1,m-1</sub><br>e <sub>1,m</sub> | · · · ·<br>· · · |                  | 1.                      |       | $\dots h_{\mathrm{Q},m-1}$ h_{\mathrm{Q},m} |                                  | <br>e <sub>p,m-2</sub><br>e <sub>p,m-1</sub> |                           | $\begin{array}{c} \dots \\ h_{Q,m-2} \\ h_{Q,m-1} \end{array}$ | $_{h^{(m-1,1)}}^{\dots}$ |

Equivalent representation of Table 3 by product terms is given by Exp. (6) based on definitions given in [50]:

# $h^{(out)} =$

$$\begin{split} h^{(1,1)} * X_m(1,1) * X_t(t_1,t_1) * X_{e,1,1}(e_{11},e_{11}) * \ldots * X_{e,p,1}(e_{p,1},e_{p,1}) * X_{h,1,1}(h_{1,1},h_{1,1}) * \ldots * \\ X_{h,Q,1}(h_{Q,1},h_{Q,1}) * X_{e,1,0}(e_{1,0},e_{1,0}) * \ldots * X_{e,p,0}(e_{p,0},e_{p,0}) * X_{h,1,0}(h_{1,0},h_{1,0}) * \ldots * \\ X_{h,Q,0}(h_{Q,m-1},h_{Q,m-1}) + \ldots + h^{(m-1,1)} * X_m(m-1,m-1) * X_t(t_{m-1},t_{m-1}) * \\ X_{e,1,m-1}(e_{1,m-1},e_{1,m-1}) * \ldots * X_{e,p,m-1}(e_{p,m-1},e_{p,m-1}) * X_{h,1,m-1}(h_{1,m-1},h_{1,m-1}) * \ldots * \\ X_{h,Q,m-1}(h_{Q,m-1},h_{Q,m-1}) * X_{e,1,m-2}(e_{1,m-2},e_{1,m-2}) * \ldots * X_{e,p,m-2}(e_{p,m-2},e_{p,m-2}) * \\ X_{h,1,m-2}(e_{1,m-2},e_{1,m-2}) * \ldots * X_{h,Q,m-2}(h_{Q,m-2},h_{Q,m-2}) + h^{(m,1)} * X_m(m,m) * X_t(t_m,t_m) * \\ X_{e,1,m}(e_{1,m},e_{1,m}) * \ldots * X_{e,p,m}(e_{p,m},e_{p,m}) * X_{h,1,m}(h_{1,m},h_{1,m}) * \ldots * X_{h,Q,m}(h_{Q,m},h_{Q,m}) * \\ X_{e,1,m-1}(e_{1,m-1},e_{1,m-1}) * \ldots * X_{e,p,m-1}(e_{p,m-1},e_{p,m-1}) * X_{h,1,m-1}(h_{1,m-1},h_{1,m-1}) * \ldots * \\ X_{h,Q,m-1}(h_{Q,m-1},h_{Q,m-1}). \end{split}$$

#### 2.4. Method of Additional Blocking Product Terms in the Linked List

This method [19] can prevent from attacks 2,3,6, based on adding of fake constants and excessive Literal parameters, given in Table 2. It uses the scheme to generate blocking product terms  $PT^-$ , providing subsuming of all illegally added product terms located in the truth table between any two given rows e.g., between entries  $e_m$  and  $e_{m-1}$ . In order to apply it, the participants of the protocol should by default use constant k - 1 only as the selected parameter for minimization procedures [18], which will always subsume all added product terms with any lower constants. For practice it is more comfort to represent steps 4 and 6, which were used in Algorithm 2 in the paper [19], as an Exp. (7) for i-th Literal, where indexed parameters *a*, *b* are written as  $\overline{x}_i, \overline{\overline{x}}_i$  for both entries:

$$\begin{split} \widetilde{X_{i}}\left(\overline{x}_{i},\overline{\overline{x}}\right) &= \\ \begin{cases} X_{i}\left(MIN\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right)+1,Max\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right)-1\right), \ if \ Max\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right)-MIN\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right) \geq 2 \\ X_{i}\left(MIN\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right),Max\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right)\right), if \ Max\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right)-MIN\left(\overline{x}_{i},\overline{\overline{x}}_{i}\right) < 2 \end{split}$$

(7)

As it is not correct to mix operators of AGA and Boolean logic [18], here operations MIN and MAX are considered as Boolean emulations of exp. (2) combined with adding or subtraction of 1. Then basing on definitions and Algorithm 2 [19] one can write logic expression, which combines two real product terms  $PT_{m-1}^+$  and  $PT_m^+$ , responding to entries with logic constants equal to numbers *m* and *m* – 1, and the blocking term  $PT_{m-1,m}^-$  with the logic constant *k* – 1. Final exp. (8) obtained e.g., for 3 variables will be

$$PT_{m-1}^{+} + PT_{m-1,m}^{-} + PT_{m}^{+} =$$

$$= h_{m-1} \star X_{1}(\overline{x}_{1}, \overline{x}_{1}) \star X_{2}(\overline{x}_{2}, \overline{x}_{2}) \star X_{3}(\overline{x}_{3}, \overline{x}_{3}) +$$

$$(k-1) \star \widetilde{X}_{1}\left(\overline{x}_{1}, \overline{\overline{x}}_{2}\right) \star \widetilde{X}_{2}\left(\overline{x}_{1}, \overline{\overline{x}}_{2}\right) \star \widetilde{X}_{e,1}\left(\overline{x}_{1}, \overline{\overline{x}}_{2}\right) +$$

$$h_{m} \star X_{1}\left(\overline{\overline{x}}_{1}, \overline{\overline{x}}_{1}\right) \star X_{2}\left(\overline{\overline{x}}_{2}, \overline{\overline{x}}_{2}\right) \star X_{3}\left(\overline{\overline{x}}_{3}, \overline{\overline{x}}_{3}\right),$$

(8)

where any  $\widetilde{X}_i(\overline{x}_i, \overline{\overline{x}})$  is given by Exp. (7).

As additional blocking segment  $PT_{m-1,m}^-$  will enlarge the overall number of product terms and the computing time for ~50%, it may be reasonable to use it as a separate page (or a part) of the MVLL.

## 3. Results: Combined Hashing Scheme for MVL Linked List

In contrast to the paper [19], the modified MVLL scheme additionally uses:

(1) data, calculated by internal subsystems of the agent, (2) binary *XOR* hashing of data of internal subsystems, and (3) selected parameters of external nodes.

#### 3.1. Modified MVLL with Mixing Data from Internal Subsystems and External Nodes

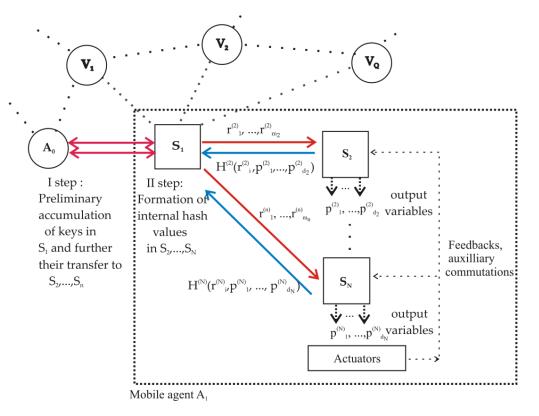

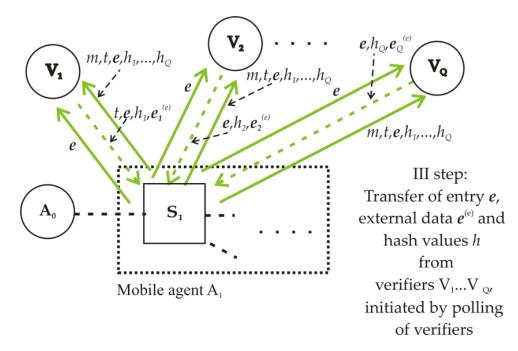

The proposed scheme of data transfer for the network mobile agent is given in Figures 2 and 3, it involves partner agents  $A_0$  and  $A_1$  and Q collaborating network nodes  $V_q$ , considered as verifiers V like in [29,51]. It suppose three basic procedures I, II, and III marked by red, blue and green arrows. Steps I and II are shown in Figure 2, and step III is given in Figure 3.

The main task of step I in Figure 2 is to provide agent  $A_1$  by the set of quasi-random keys by means QKD line, and to transform the finally processed quantum key into the subset of fragmented quasi-random keys written in subsystems  $S_2, \ldots, S_N$ . Thus, data flow I (red) supposes periodic loading of the mobile agent by quasi-random keys, received via the wireless QKD line [67,68], connecting agent  $A_0$  with mobile agent  $A_1$  in the trusted service zone providing appropriate level of security. The generated key is to be further fragmented to the set of 8-bit one-time quasi-random keys in order to adapt the system for 8-bit microcontrollers. These keys are to be accumulated and used for internal verification procedures, the needed throughput of quasi-random numbers source may be even less than  $\sim 1$  Kbit/s. In the considered verification scheme the source of so-called entangled photons from route verification scheme [29] is not obligatory, and can be changed for any low-throughput QKD line, providing generation of quasi random one-time keys. For simplicity internal subsystem  $S_1$  is shown as one supervisor module to control data exchange between external and internal devices.

**Figure 2.** Steps I and II of the procedure to obtain the set of verification data for the joint linked list in the agent  $A_1$ , combining data of internal subsystems  $p_1^{(n)}, \ldots, p_{d_N}^{(n)}$  and quasi-random keys  $r_i^{(n)} b$ . y means of hashing functions  $H^{(2)}, \ldots, H^{(N)}$ .

**Figure 3.** Step III of the procedure to obtain the set of verification data for the joint linked list. It discloses the interaction of agent  $A_1$  with external verifiers  $V_1, V_2, \ldots, V_Q$ , combining data of internal subsystems and external verifiers.

When the set of shortened fragmentary quasi-random keys is formed, then the supervisor module  $S_1$  chooses the time moment to generate the new entry for MVLL according to the agent's task. This moment may e.g., respond to the visit to the next check-point. Then module  $S_1$  activates the step II (tagged by blue arrows) to form the new entry, which includes the sequential polling of internal subsystems  $S_2, \ldots, S_N$  to receive preliminary selected parameters for the external backup. Further internal hashing procedure should approve these data. Here for simplicity we do not consider any routine communications between the agent and external nodes which may interrupt the process.

Step III of the procedure is shown in Figure 3 and refers to the external distributed storage formation [19], which partially use blockchain scheme [25,26] with network protocols like e.g., [69,70]. In contrast to MVLL version proposed in [19], the new one may use more verification data from external nodes. E.g., space coordinates (x, y, z) of the mobile checkpoint node can be useful to approve the passed route of the mobile agent. Polling of Q free collaborating nodes (first green arrow) is to be done according to the initially given list of participants, and the reply transfer (backward oriented green arrow in middle) returns assigned quasi-random hash values and possible additional technical parameters. After the polling procedure the agent  $A_1$  should resend the completed new entry to all involved participants (third green arrow). Data extraction from distributed external storages is supposed to be especially requested.

#### 3.2. Possible Sources of Short Fragmented Keys

As QKD line can be blocked by intensive optical noize of any nature, alternative sources of quasi-random keys principally can be included into the scheme. These variants with lower level of privacy principally can be realized by the MVL–based scheme of the random oracle [57] or by a quantum random number generator [21]. Such alternatives does not disturb MVLL procedures.

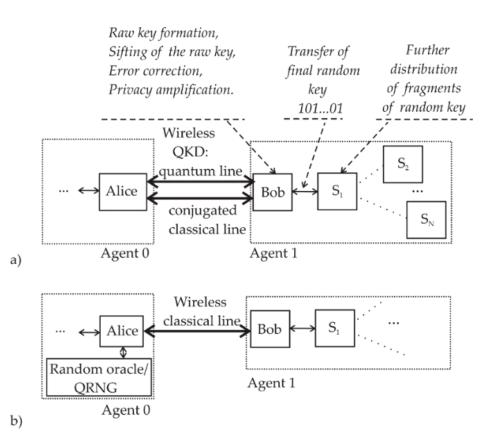

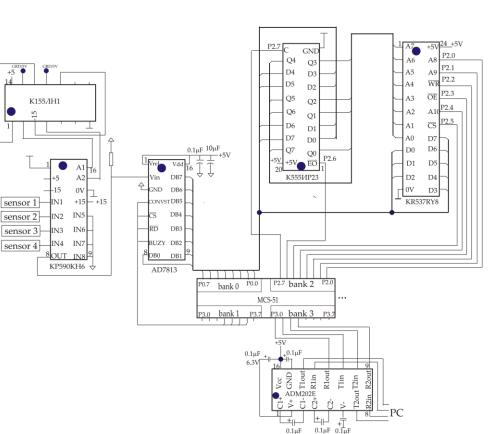

Step I (red arrows) in Figure 2 basically suppose the periodical work of the wireless QKD line, providing quantum keys distribution for agents  $A_0$  and  $A_1$ . The most secured level of QKD line is due to quantum mechanics and non-cloning theorem [61], which guarantees that if all basic protocols were carried out exactly, the generated key is known only to a pair of interacting abonents Alice and Bob with small enough probability of errors (see, e.g., review [12]). Modules Alice and Bob, see Figure 4a, use the conjugated pair of quantum and classical data lines and exploit specialized procedures, reglamented by cryptography standards by NIST [71], what limits the possibility to get inside and to add any additional verification procedures. Alice's and Bob's modules are to be integrated into internal subsystems of interacting agents, but MVLL procedures scarcely can be added into Bob module, and the separate verification subsystem  $S_1$  is needed. As all certificated QKD lines provide at least NIST tests for randomness [71,72], the "block" test passing is guaranteed including 8- bit variant. Then the procedure for fragmenting of quantum data array into 8-bit fragmented keys can be choosen arbitrarily. Less protected versions, shown in Figure 4b, refer to alternative sources of quasi-random numbers like AGA-based random oracle [57] and QRNG [21].

#### 3.3. Acquisition of Internal Parameters of the Agent and Their Hashing

Algorithm for acquisition of internal verification data is proposed in Algorithm 1. Every of subsystems modules  $S_2, \ldots, S_N$  shown earlier in Figure 2 receives randomly given fragmented keys and uses them in calculation of hashing function  $H^{(n)}(\mathbf{r},\mathbf{p})$ , where p includes current values of output variables of the subsystem n, and r is a fragmented key. Components of p are preferably to be written in internal SRAM of a subsystem during the verification procedure, in order to be extracted in case of the detailed check. Coded by hashing procedure output variables are to be returned back from  $S_2, \ldots, S_N$  to the verification module  $S_1$ , this process is shown by the blue arrows in Figure 2. Such mapping is to prevent direct illegal data reading from digital buses and is to check the operability of the subsystem in the coded form.

**Figure 4.** (a) Wireless QKD line can be regarded as the most secured source of quasi-random numbers for the pair of autonomous agents 0 and 1 of the MAS. (b) Less protected schemes may include QRNG and AGA-based random oracle.

According to Figure 2 MVLL is to include some variables of internal subsystems  $S_2, \ldots, S_N$  and hash values assigned by  $S_1$ , optionally accompanied by some technical parameters of external nodes e.g., their coordinates. One can avoid here the direct use of internal time variable, as subsystems sequentially output values of variables  $p_1^{(2)}, \ldots, p_{d_2}^{(2)}, \ldots, p_1^{(N)}, \ldots, p_{d_N}^{(N)}$  with much greater rate than external messages are received. Here for simplicity we suppose that all variables are calculated sequentially, where the sequence of operation responds to values n = 1, 2..., N, although the real time grid of their outputs can be more complex.

# 3.4. Two-Steps XOR Hashing in Agent's Subsystems

It seems more appropriate to use in internal subsystems (where possible!) simple and well-known binary logic hash functions in order to apply commercial modules and to shorten calculations. Principally, for hashing procedures one can design some MVL functions, but this seems to give advantages only in combination with specially planned AI procedures for subsystems, which are not discussed here. As it is being widely used in classic and quantum cryptography procedures [51], the well-known binary operator *XOR* ( $\oplus$ ) [73,74] can be the first recommended variant for internal hashing, combining one-time quasi-random fragmented key  $r_d^{(n)}$  and the set of  $w_n$  output parameters  $p_{w_n}^{(n)}$  of the subsystem  $S_n$ . Operator *XOR* is typically included into specifications of microcontrollers [74] and needs only 1 work cycle; it is oftenly tagged as *XRL* in microassembler specifications. Such two-stage hashing procedure is shown in the Table 4. The first step is to be calculated in internal subsystems  $S_2, \ldots, S_N$ . of the agent  $A_1$ . The second step of hashing is to be done in the supervisor module  $S_1$  in order to minimize additional calculations in  $S_2, \ldots, S_N$ .

| Algorit | hm 1: Acquisition of inte                                                                                                                                                                                                                                          | ernal hashing parameters $H^{(n)}$ for $S_2, \ldots, S_N$ .                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input:  | $\begin{array}{cccc} k \leftarrow & N \leftarrow & N \leftarrow & \\ & M \leftarrow & \\ & d_n \leftarrow & \\ & w_2, \ldots, w_N \leftarrow & \\ r_1^{(2)}, \ldots, r_{d_2}^{(2)} & \\ & \ldots & \leftarrow \\ & r_1^{(N)}, \ldots, r_{d_N}^{(N)} & \end{array}$ | Number of truth levels (not obligatory equal to 256);<br>Number of internal subsystems $S_1, \ldots, S_N$ of the agent $A_1$ ;<br>Maximal possible number of entries in MVLL;<br>Number of documented parameters of the subsystem,<br>$d_n = 1, \ldots, D$ ;<br>Numbers of output parameters in subsystems $S_2, \ldots, S_N$ ;<br>Sets of fragmented keys, preliminary prepared in subsystem $S_1$<br>for the new session of documentation in MVLL;                                |

| 1.      | Subsystem $S_1$                                                                                                                                                                                                                                                    | assigns counter $n = 2$ ; As $S_1$ is the service subsystem!                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.      | Subsystem $S_1$                                                                                                                                                                                                                                                    | sets clocking signal ("write") to $S_n$ ;<br>transfer $r_{d_n}^{(n)}$ to subsystem $S_n$ ;                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.      | Subsystem S <sub>n</sub>                                                                                                                                                                                                                                           | writes transferred $r_{d_n}^{(n)}$ ;<br>assigns $n = n + 1$ ;                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.      | Subsystem S <sub>1</sub>                                                                                                                                                                                                                                           | checks if $n = N$ , if yes goes to step 5,<br>otherwise goes to step 2;<br>calculates the set of all its output variables $\{p_1^{(n)}, \ldots, p_{w_n}^{(n)}\}$ ;<br>writes $\{p_1^{(n)}, \ldots, p_{w_n}^{(n)}\}$ in its internal memory;                                                                                                                                                                                                                                         |

| 5.      | Subsystem S <sub>n</sub>                                                                                                                                                                                                                                           | calculates hash function $H^{(n)}(r_{d_n}^{(n)}, p_1^{(n)}, \dots, p_{d_n}^{(n)})$ ;<br>sets clocking signal ("write") to $S_1$ ;<br>transfer hash value $H(r_{d_n}^{(n)}, p_1^{(n)}, \dots, p_{d_n}^{(n)})$ to $S_1$ ;<br>(*) Hash function is discussed in Section 3.4<br>(**) Enlargement of n from 2 up to n responds to the basic sequence of<br>operation for subsystems in the agent $A_1$<br>writes transferred $H^{(n)}(r_{d_n}^{(n)}, p_1^{(n)}, \dots, p_{d_n}^{(n)})$ ; |

| 6.      | Subsystem $S_1$                                                                                                                                                                                                                                                    | assigns $n = n + 1$ ;<br>checks if $n = N$ , if yes goes to Exit—step 7,<br>otherwise goes to step 5;                                                                                                                                                                                                                                                                                                                                                                               |

| 7.      |                                                                                                                                                                                                                                                                    | Exit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | <b>Output:</b> $H^{(n)} \rightarrow$                                                                                                                                                                                                                               | The set of data for the second step of hashing                                                                                                                                                                                                                                                                                                                                                                                                                                      |

As it was shown in Section 2.2, several types of attacks aimed at MVL model can be based on modification of parameters of logic functions, written in the general format exp. (2) as arrays *A*, *B*,*C* describing subsystems of the agent. That is why *XOR* hashing can be directly used for data protection of such arrays. This procedure is more visually shown in Figure 5, where quasi-random key  $s r_{d_n}^{(n)}$  may be either given as additional matrix elements in rows, or processed as additional separate column. Calculation of *XOR* hash values is firstly to be done for rows and then for column, it is the most simple and universal procedure to verify illegal modifications of the MVL function.

**Table 4.** Two steps of the internal hashing procedure of the agent  $A_1$ .

|         | Involved Subsystem                                  | Expression                                                                                                                             |  |  |

|---------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I Step  |                                                     | $H^{(n)}(r, p) = r_d^{(n)} \oplus p_1^{(n)} \oplus p_2^{(n)} \oplus \ldots \oplus p_{w_n}^{(n)},$                                      |  |  |

|         | Hash value for $S_2$                                | n = 2, N<br>$H^{(2)}(r, p)$ , calculated in $S_2$                                                                                      |  |  |

|         | $\dots$ Hash value for $S_N$                        | $H^{(N)}(r, p)$ , calculated in $S_N$                                                                                                  |  |  |

| II step | Integral hash value for all subsystems of the agent | $H^{(int)}(r, \mathbf{p}) ==$ $H^{(2)}(r, \mathbf{p})H^{(3)}(r, \mathbf{p}) \dots H^{(N)}(r, \mathbf{p})$ calculated in S <sub>1</sub> |  |  |

Figure 5. The general scheme to apply two step hashing to verification of MVL.

3.5. Formation of Modified MVLL with Internal and External Parameters

According to Figure 2 the entry for the modified version of MVLL should contain number *m*, time tag *t*, parameters  $e_m = \{e_{1,m}, \ldots, e_{p,m}\}$ , and externally assigned hash values  $h=\{h_1, \ldots, h_Q\}$ . It also should include external and internal parameters  $e_m = \{e_m^{(int)}, e_m^{(ext)}\}$  instead of the set  $e_m = \{e_{1,m}, \ldots, e_{p,m}\}$ , i.e., subsets  $e_m^{ext} = \{e_{1,m}^{ext}, \ldots, e_{m}^{ext}\}$  and  $e_m^{int} = \{e_{1,m}^{int}, \ldots, e_{p,m}\}$ . For comfort we will use shortened notation  $e_m^{ext} = e_m^{(e)}$  and  $e_m^{int} = e_m$ . Besides this, entry should contain internal hash functions  $H^{(int)}(r, p)$  of the last and of the previous entry  $e_{m-1}$ . The identifier of the agent and its license number are also actual parameters. Thus, modified MVLL function containing entries with numbers from 1 up to *m* has the structure  $h^{(out)} = F_{ll}(m, t, e_m, e_m^{(e)}, H_m^{(int)}h_{1,m}, \ldots, h_{Q,m}, e_{m-1}, e_{m-1}^{(e)}, H_{m-1}^{(int)}h_{1,m-1}, \ldots, h_{Q,m-1})$ . Then final logic expression will respond to Exp. (9):

Note that data for external ledger should respond to 32–64 bit format of data, as internal microcontrollers or FPGA for IoT devices can mainly use 8-bit or sometimes 16-bit formats [75]. In any way, proposed formal procedures leave enough freedom of choice either to complement data by 0s for the necessary number of elder bits, or to sequentially unite bytes of several variables into one variable, or to combine both variants.

$$\begin{split} h^{(out)} &= \\ h^{(1,1)} \star X_{m}(1,1) \star X_{t}(t_{1},t_{1}) \star X_{e,1,1}(e_{11},e_{11}) \star \ldots \star X_{e,p,1}(e_{p,1},e_{p,1}) \\ \star X_{e^{(e)},1,1}\left(e_{11}^{(e)},e_{11}^{(e)}\right) \star \ldots \star X_{e^{(e)},v,1}\left(e_{v,1}^{(e)},e_{v,1}^{(e)}\right) \star X_{h,1,1}(h_{1,1},h_{1,1}) \star \ldots \\ \star X_{h,Q,1}(h_{Q,1},h_{Q,1}) \star X_{e,1,0}(e_{1,0},e_{1,0}) \star \ldots \star X_{e,p,0}(e_{p,0},e_{p,0}) \\ \star X_{e^{(e)},1,0}\left(e_{10}^{(e)},e_{10}^{(e)}\right) \star \ldots \star X_{e^{(e)},v,0}\left(e_{v,0}^{(e)},e_{v,0}^{(e)}\right) \star X_{h,1,0}(h_{1,0},h_{1,0}) \star \ldots \\ \star X_{h,Q,0}(h_{Q,m-1},h_{Q,m-1}) + \ldots + h^{(m-1,1)} \star X_{m}(m-1,m-1) \star X_{t}(t_{m-1},t_{m-1}) \\ \star X_{e^{(1)},m-1}(e_{1,m-1},e_{1,m-1}) \star \ldots \star X_{e,p,m-1}(e_{p,m-1},e_{p,m-1}) \\ \star X_{e^{(e)},1,m-1}\left(e_{1,m-1}^{(e)},e_{1,m-1}^{(e)}\right) \star \ldots \\ \star X_{h,Q,m-1}(h_{Q,m-1},h_{Q,m-1}) \star X_{e,1,m-2}(e_{1,m-2},e_{1,m-2}) \star \ldots \\ \star X_{h,Q,m-1}(h_{Q,m-1},h_{Q,m-1}) \star X_{e^{(e)},1,m-2}\left(e_{1,m-2}^{(e)},e_{1,m-2}^{(e)}\right) \star \ldots \\ \star X_{e^{(e)},v,m-2}\left(e_{v,m-2},e_{v,m-2}\right) \star X_{e^{(e)},1,m-2}\left(e_{1,m-2},e_{1,m-2}\right) \star \ldots \\ \star X_{e^{(e)},v,m-2}\left(e_{v,m-2}^{(e)},e_{v,m-2}^{(e)}\right) \star X_{h,1,m-2}(e_{1,m-2},e_{1,m-2}) \star \ldots \\ \star X_{e^{(e)},v,m-2}\left(e_{v,m-2}^{(e)},h_{Q,m-2}\right) + h^{(m,1)} \star X_{m}(m,m) \star X_{t}(t_{m},t_{m}) \\ \star X_{e,1,m}(e_{1,m},e_{1,m}) \star \ldots \star X_{e,p,m}(e_{p,m},e_{p,m}) \star X_{e^{(e)},1,m}\left(e_{1,m}^{(e)},e_{1,m}^{(e)}\right) \star \ldots \\ \star X_{e^{(e)},v,m}\left(e_{v,m}^{(e)},e_{v,m}^{(e)}\right) \star X_{h,1,m}(h_{1,m},h_{1,m}) \star \ldots \star X_{h,Q,m}(h_{Q,m},h_{Q,m}) \\ \star X_{e,1,m-1}\left(e_{1,m-1}^{(e)},e_{1,m-1}^{(e)}\right) \star \ldots \star X_{e,p,m-1}\left(e_{p,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \\ \star X_{e^{(e)},v,m-1}\left(e_{1,m-1}^{(e)},e_{1,m-1}^{(e)}\right) \star \ldots \star X_{e^{(e)},v,m-1}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \star \ldots \star X_{e^{(e)},v,m-1}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \\ \star X_{e^{(e)},v,m}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \star \ldots \star X_{e^{(e)},v,m-1}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \\ \star X_{e^{(e)},v,m}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \star \ldots \star X_{e^{(e)},v,m-1}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \\ \star X_{e^{(e)},v,m}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \star \ldots \star X_{e^{(e)},v,m-1}\left(e_{v,m-1}^{(e)},e_{v,m-1}^{(e)}\right) \\$$

# 4. Results: MVLL Scheme for Route Verification Task

As position verification methods may combine GPS, lidar, and computer vision systems, the route planning and the tracking estimation for mobile agents involves the problem of precision of data [76], influenced by the speed of mobile agents and satellites disposition. The controlled range for space coordinates can vary from centimeters up to thousands of km, and it is necessary to provide enough accuracy for all possible distances. First variant here is to apply correlated variables in the discrete *k*-valued logic model of AGA [18,19], where one can represent space coordinate *x* e.g., as 1560 m = 1 km + 500 m + 60 m+.... by the summation

$$x = x^{(1)} \times 1 + x^{(2)} \times 10 + \dots x^{(p)} \times 10^{p}.$$

(10)

However, for the MVLL in route verification task there is the second possible scheme to apply purely formal representation excluding summation as in Exp. (13). It is based on the fact, that the distributed backup storage of MVLL should only measure and approve the correctness of data, as the value of coordinates discrepancy is required further at the stage of decision-making. Thus, verification or comparison of data from different storages mainly includes formal checks equal/non-equal, and further procedures are the another task. So that if unique GPS coordinates are represented [77] by a popular format, say, 57"45,4682, one can write it e.g., as the set of numbers {57}, {45}, {4682} = #{00111001}b, #{00101101}b, #{0010101}b, fixing by default the position of separating tags. Advantage of formal AGA model is that for any bit format of space coordinates they can be quickly represented by several bytes in logic expressions with known by default rules for reverse reconstruction of geographical degrees, minutes, and seconds.

For the route vefification task the difference between the given and the real route should be finally described by the deviation function  $F_{eval}$ , which should estimate the difference between space coordinates x, y for the planned route and measured coordinates  $x^{(e)}, y^{(e)}$ :  $F_{eval} = F(N_{agent}, N_{license}, x, y, x^{(e)}, y^{(e)})$ . Close case here is the comparison of coordinates obtained by different GPS receivers, installed in navigation systems of the check-point and the mobile agent. Then the simplest way is to use MVLL with formal representation of coordinates. Realistic version of 8-bit MVLL seems to be represented by the entry described by Exp. (11)

$$\boldsymbol{e}_{m} = \{m, t, ID_{agent}, N_{lic}, x^{(1)}, x^{(2)}, x^{(3)}, x^{(4)}, H^{(int)}, x^{(e1)}, x^{(e2)}, x^{(e3)}, x^{(e4)}, h_{1}, \dots, h_{Q}\},$$

(11)

where *m* is the entry number in the ledger, *t*—time of registration by the first of external verifying nodes,  $ID_{agent}$ —digital identifier of the agent (for simplicity we suppose it to be 1 byte),  $N_{lic}$ —license number (also 1 byte),  $x^{(1)}, x^{(2)}, x^{(3)}, x^{(4)}$  describe 4 bytes of space coordinates, and data marked by (<sup>e</sup>) refer to another source of data, e.g., to the check-point. Here every set  $x^{(1)}, x^{(2)}, x^{(3)}, x^{(4)}$  includes both the latitude and the longitude (N and E) in NMEA-0183 [78]). Variable  $H^{(int)}$  in Exp. (11) describes values of internal hash function. Thus, entry  $e_m$  in AGA can be written as the logic product term Exp. (12):

$$\begin{aligned} \mathbf{e}_{m} &= \\ h^{(m,1)} \star X_{m}(m,m) \star X_{t}(t_{m},t_{m}) \star X_{ID \ agent}(ID,ID) \star X_{lic}(N_{lic},N_{lic}) \star X_{H^{(int)}}\left(H^{(int)},H^{(int)}\right) \star \\ \star X_{x^{(1)}}\left(x_{m}^{(1)},x_{m}^{(1)}\right) \star X_{x^{(2)}}\left(x_{m}^{(2)},x_{m}^{(2)}\right) \star X_{x^{(3)}}\left(x_{m}^{(3)},x_{m}^{(3)}\right) \star X_{x^{(4)}}\left(x_{m}^{(4)},x_{m}^{(4)}\right) \star \\ \star X_{x^{(e1)}}\left(x_{m}^{(e1)},x_{m}^{(e1)}\right) \star X_{x^{(e2)}}\left(x_{m}^{(e2)},x_{m}^{(e2)}\right) \star X_{x^{(e3)}}\left(x_{m}^{(e3)},x_{m}^{(e3)}\right) \star X_{x^{(e4)}}\left(x_{m}^{(e4)},x_{m}^{(e4)}\right) \star \\ \star X_{h,1,m}(h_{1,m},h_{1,m}) \star \dots \star X_{h,Q,m}(h_{Q,m},h_{Q,m}) \star \\ \star X_{m-1}(m-1,m-1) \star X_{t}(t_{m-1},t_{m-1}) \star X_{ID \ agent}(ID,ID) \star X_{lic}(N_{lic},N_{lic}) \star X_{H^{(int)}}\left(H^{(int)},H^{(int)}\right) \star \\ \star X_{x^{(1)}}\left(x_{m-1}^{(1)},x_{m-1}^{(1)}\right) \star X_{x^{(2)}}\left(x_{m-1}^{(2)},x_{m-1}^{(2)}\right) \star X_{x^{(3)}}\left(x_{m-1}^{(3)},x_{m-1}^{(3)}\right) \star X_{x^{(4)}}\left(x_{m-1}^{(4)},x_{m-1}^{(4)}\right) \star \\ \star X_{x^{(e1)}}\left(x_{m-1}^{(e1)},x_{m-1}^{(e1)}\right) \star X_{x^{(e2)}}\left(x_{m-1}^{(e2)},x_{m-1}^{(e2)}\right) \star X_{x^{(e3)}}\left(x_{m-1}^{(e3)},x_{m-1}^{(e3)}\right) \star X_{x^{(e4)}}\left(x_{m-1}^{(e4)},x_{m-1}^{(4)}\right) \star \\ \star X_{h,1,m-1}(h_{1,m-1},h_{1,m-1}) \star \dots \star X_{h,Q,m-1}(h_{Q,m-1},h_{Q,m-1}). \end{aligned}$$