Article

# **Observation of Large Threshold Voltage Shift Induced by Pre-applied Voltage to SiO<sub>2</sub> Gate Dielectric in Organic Field-Effect Transistors**

Yifu Guo<sup>1</sup>, Junyang Deng<sup>2,3</sup>, Jiebin Niu<sup>2</sup>, Chunhui Duan<sup>4</sup>, Shibing Long<sup>1</sup>, Mengmeng Li<sup>2,3,\*</sup> and Ling Li<sup>2</sup>

- <sup>1</sup> School of Microelectronics, University of Science and Technology of China, Hefei 230026, China

- <sup>2</sup> Key Laboratory of Microelectronic Devices and Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China

- <sup>3</sup> University of Chinese Academy of Sciences, Beijing 100049, China

- <sup>4</sup> Institute of Polymer Optoelectronic Materials & Devices, State Key Laboratory of Luminescent Materials and Devices, South China University of Technology, Guangzhou 510640, China

- \* Correspondence: limengmeng@ime.ac.cn; Tel.: +86-10-8299-5580

Abstract: Field-effect transistors based on organic semiconducting materials (OFETs) have unique advantages of intrinsically mechanical flexibility, simple preparation process, low manufacturing cost, and large-area preparation. Through the innovation of new material design and device structures, the performance of device parameters such as mobility, on–off current ratio, and the threshold voltage (V<sub>TH</sub>) of OFETs continues to improve. However, the V<sub>TH</sub> shift of OFETs has always been an important problem restricting their practical applications. In this work, we observe that the V<sub>TH</sub> of polymer OFETs with the widely investigated device structure of a SiO<sub>2</sub> bottom-gate dielectric is noticeably shifted by pre-applying a large gate voltage. Such a shift in V<sub>TH</sub> remains to a large extent, even after modifying the surface of the SiO<sub>2</sub> dielectric using a hexamethyldisilazane (HMDS) self-assembled monolayer. This behavior of V<sub>TH</sub> can be ascribed to the charge trappings at the bulk of the SiO<sub>2</sub>. In addition, the generality of this observation is further proven by using two other conjugated polymers including p-type PDPP3T and n-type PTzNDI-2FT, and a similar trend is obtained.

Keywords: organic field-effect transistor; threshold voltage shift; charge trapping; pre-applied voltage

## 1. Introduction

With the rapid development of the Internet of Things (IOT), smart electronic devices such as automatic sweeping machines, intelligent monitoring, and other IOT products greatly facilitate everyone's daily life. To make these devices smarter and more convenient, there has been a flurry of research into wearable and flexible electronics. Organic semiconductor material-based field-effect transistors (OFETs) have attracted considerable attention due to their intrinsically bendable and stretchable flexibility, good biocompatibility, and the advantages of large-area fabrication through solution processing methods at low temperatures. Therefore, they hold great application potentials in the fields of health detection, physiological information processing, and flexible electronics [1–9].

In the last two decades, great efforts have been devoted to improving the device performances of OFETs, including the on–off current ratio [10–12], field-effect mobility [12–15], subthreshold swing [16–18], and threshold voltage ( $V_{TH}$ ) [19–21]. Among the above parameters,  $V_{TH}$  is the key to determining whether the transistor works at the expected operation voltage. However, the capture and release of charge carriers by defects or traps in the devices typically lead to the  $V_{TH}$  shift. Trapped charges provide an additional electric field to the conduction channel, which directly alters the carrier concentration within the channel and, thus, critically affects the value of  $V_{TH}$  [22–24]. Furthermore,  $V_{TH}$  shifts in bias stress testing are considered to be one of the most important indicators to measure the stability of OFETs. A constant voltage is continuously applied to the gate electrode

**Citation:** Guo, Y.; Deng, J.; Niu, J.; Duan, C.; Long, S.; Li, M.; Li, L. Observation of Large Threshold Voltage Shift Induced by Pre-applied Voltage to SiO<sub>2</sub> Gate Dielectric in Organic Field-Effect Transistors. *Electronics* **2023**, *12*, 540. https:// doi.org/10.3390/electronics12030540

Academic Editor: Antonio Di Bartolomeo

Received: 20 December 2022 Revised: 5 January 2023 Accepted: 17 January 2023 Published: 20 January 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). of OFETs, and the time-dependent  $V_{TH}$  is compared in order to evaluate the stability of the transistor. The smaller the difference in  $V_{TH}$ , the better the stability of the device. This bias stress effect for OFETs is generally attributed to defects or charge traps at the interface between the dielectric and semiconductor [25–28]. This  $V_{TH}$  shift has detrimental impacts on the practical applications of OFETs.

On the other hand, the floating-gate strategy is an efficient way to precisely control  $V_{TH}$  and the consequent operation state for both traditional Si-based transistors and OFETs [29]. Usually, a floating-gate transistor differs from a field-effect transistor structure by the insertion of an additional floating-gate electrode into the dielectric. The floating gate is charged by a large external electric field. After the external electric field is removed, the charges stored in the floating gate attract or repel the carriers in the channel of the transistor, resulting in  $V_{TH}$  shifts. For the flash memory, the range of threshold voltage change is expected to be as large as possible, which means a wider memory window and facilitates the reading or writing process of stored information. High density, low power, and high speed are three important indicators in CMOS flash memory [30]. Organic non-volatile memory based on floating-gate structures has also been realized [31–33].

In this article, a bottom-gate bottom-contact OFET based on a Si/SiO<sub>2</sub> substrate is fabricated. When a bias voltage is pre-applied to the Si gate, an obvious shift in  $V_{TH}$  is observed, which can be attributed to the defects or traps at the bulk of the SiO<sub>2</sub> and is different from the stress bias effect and floating-gate transistors. This hypothesis is supported by the surface modification of SiO<sub>2</sub> gate dielectrics with a hexamethyldisilazane (HMDS) self-assembled monolayer (SAM), which is generally considered to be an efficient way to reduce defects or charge traps on the surface of SiO<sub>2</sub>, and the V<sub>TH</sub> shift still remains for the HMDS-modified transistors. In addition, the impact of semiconducting materials on such a phenomenon is excluded by fabricating OFETs using two other polymers including p-type PDPP3T and n-type PTzNDI-2FT, and similar trends are obtained.

### 2. Results and Discussion

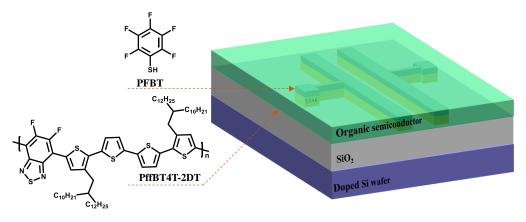

Benefiting from their atomically flat surface, simplified processing procedure, and good insulation for low leakage current, heavily p-doped Si wafers with 300 nm thick thermally grown SiO<sub>2</sub> are widely utilized to fabricate back-gate OFETs [34–40]. Here, we use the same substrate with SiO<sub>2</sub> as the gate dielectric and doped Si as the back gate for the OFET, as shown in Figure 1. A p-type conjugated polymer, PffBT4T-2DT, is used as the organic semiconducting material. In order to minimize the contact resistance between the semiconductor and metal electrodes, a 2,3,4,5,6-pentafluorothiophenol (PFBT) SAM was functionalized onto Au electrodes before dynamic spin-coating with PffBT4T-2DT film [41,42].

**Figure 1.** Chemical structures of PFBT (top) and PffBT4T-2DT (bottom) and schematic structure of the fabricated OFET.

The fabricated transistor shows a typical linear/saturation behavior, and a high on–off current ratio of  $10^7$  is achieved (Figure S1). In this saturation regime, drain current (I<sub>DS</sub>) can be described using Equation (1):

$$I_{DS} = \frac{1}{2} \mu C_{OX} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(1)

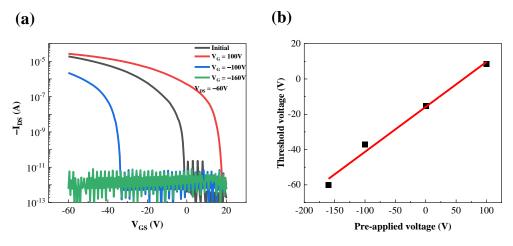

where  $\mu$  represents the mobility of carriers and V<sub>GS</sub> is the gate voltage. C<sub>OX</sub> is the unit-area capacitance of the dielectric. W and L represent the width and length of the transistor channel. The intercept of the square root of  $I_{DS}$  is utilized to extract  $V_{TH}$ , and the value of -15.3 V is obtained for the PffBT4T-2DT transistor. We find that a pre-applied voltage to the Si gate has a remarkable influence on  $V_{TH}$ . For example, by pre-applying 100 V to the gate electrode for 10 s,  $V_{TH}$  shifts towards the positive direction compared to the initial state, and  $V_{TH} = 8.4$  V is observed. On the other hand, we also apply a negative voltage of -100 V to the gate electrode. In this case, the transfer curve shifts to the negative direction, and  $V_{TH}$  moves to -37.1 V. The transfer curves at various pre-applied voltages are shown in Figure 2a, and the saturated mobility is almost independent of the pre-applied voltage (Figure S2). Figure 2b summarizes the relationship between the pre-applied voltage and the threshold voltage, and a near-linear relation is obtained. It is evident that, as the preapplied gate voltage increases, the V<sub>TH</sub> shift becomes clearer. The threshold voltage shift is 45 V by pre-applying a gate voltage of +100 V or -100 V, while this value is significantly enhanced to over 70 V by using the pre-applied voltage of -160 V. Interestingly, such a threshold voltage shift remains almost unchanged when pre-applying a constant gate voltage multiple times (Figure S3). Additionally, it is found that PFBT functionalization on Au electrodes has a negligible impact on such a phenomenon (Figure S4).

**Figure 2.** (a) Transfer curves at different pre-applied voltages to the gate electrode; (b) Threshold voltage shift as a function of pre-applied voltage to the gate electrode.

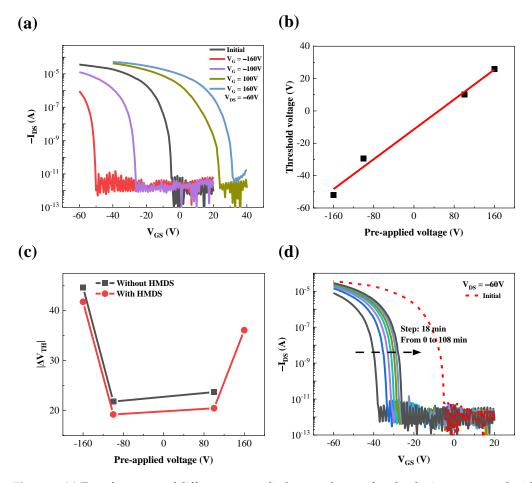

It has been widely reported that defects or traps at the interface between the organic semiconductor and the gate dielectric contribute to the shift of the transfer curve [43–45], and surface modification using HMDS SAM is an efficient method that helps reduce the defects of the SiO<sub>2</sub> surface and improves the performance of OFETs. Before spin-coating organic semiconductor thin films, the surface of the SiO<sub>2</sub> was exposed to an HMDS vapor for 3 min to passivate the surface [23,46]. It is evident that the HMDS modification of the SiO<sub>2</sub> surface efficiently reduces the density of trapping sites at the semiconductor/dielectric interface (Figure S5).

Under the same pre-applied gate voltage conditions mentioned above, the transfer curve of the device that is treated by HMDS is shown in Figure 3a. It is clear that there is still a large  $V_{TH}$  shift phenomenon, and a clear dependence on the pre-applied voltage remains (Figure 3b). Compared with the experimental results without HMDS modification,

the shift in threshold voltage ( $\Delta V_{TH}$ ) is slightly lower than that of HMDS-modified OFETs under the same pre-applied gate voltage (Figure 3c), which can be attributed to the reduced trapping sites at the interface between the organic semiconductor and SiO<sub>2</sub> dielectric, to a certain extent because of HMDS modification. Despite this, for HMDS treated devices, a pre-applied 100 V gate voltage still induces V<sub>TH</sub> move up to 10.2 V ( $\Delta V_{TH} = 20.45$  V). Therefore, it can be concluded that the large V<sub>TH</sub> shift we observed in this work did not originate from the interfacial trappings (bias stress effect), and the defects or trappings in the SiO<sub>2</sub> bulk might be the main contributor. Particularly, for the HMDS-treated transistor, the transfer curve was tested every 18 min after a voltage of -140 V was pre-applied to the gate electrode. The transfer curve slowly moved towards the initial position over time, as shown in Figure 3d. Although the large V<sub>TH</sub> shift observed in this work does not belong to the bias stress effect, this time-dependent V<sub>TH</sub> can still be described using the stretched exponential model [26,47] (Figure S6).

**Figure 3.** (a) Transfer curves of different pre-applied gate voltages after the device was treated with HMDS; (b) Threshold voltage shift as a function of pre-applied voltage to the gate electrode; (c) The relationship of  $\Delta V_{TH}$  with pre-applied gate voltage with (red line) and without (black line) HMDS modification; (d) With a pre-applied –140 V gate voltage, the transfer curves of the HMDS-treated device with time.

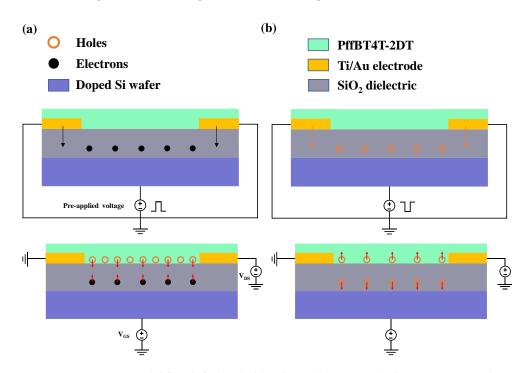

Considering the above experimental results, the main reason for this phenomenon can be explained using Figure 4. When pre-applying a large positive gate voltage, electrons are injected from the source and drain electrodes into the gate dielectric [48]. After removing the pre-applied gate voltage, a certain portion of electrons are trapped in the bulk of the SiO<sub>2</sub>. This process seems similar with floating-gate transistors, where the injected electrons "charge up" the dielectric. Those "charged up" electrons provide an additional electric field to the conduction channel, resulting in a large  $V_{TH}$  shift in the positive direction. As time

goes on, the trapped electrons are released to the channel slowly and gradually in the form of leakage current, causing the threshold voltage of the OFET to gradually recover over time, like the trend shown in Figure 3d. On the contrary, a negative pre-applied voltage leads to "injected" holes into the SiO<sub>2</sub> gate dielectric, trapped in the bulk of the dielectric after removal of the pre-applied gate voltage. These trapped holes repel the carriers within the conducting channel, causing V<sub>TH</sub> shift in the negative direction.

**Figure 4.** Operation model for shift threshold voltage: (**a**) pre-applied positive gate voltage and (**b**) negative voltage.

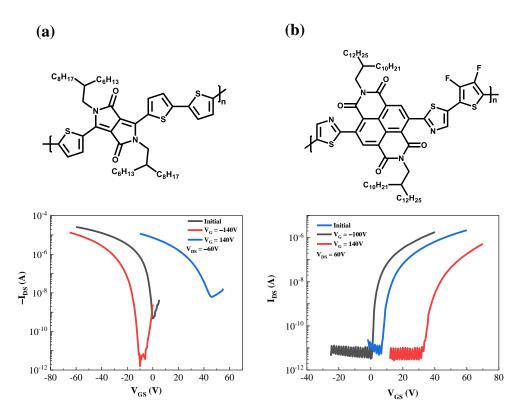

In addition, we also used other two conjugated polymers including p-type PDPP3T [49,50] and n-type PTzNDI-2FT to verify the generality of our observation of V<sub>TH</sub> shift, where the surface of the SiO<sub>2</sub> dielectric is functionalized using HMDS SAM. Typical linear/saturation behaviors are observed for both transistors (Figures S5b and S7). The transfer curves of those two OFETs after pre-applied gate voltage are shown in Figure 5. It can be seen that, for both polymers, there still exists a large threshold voltage shift phenomenon after a pre-applied large gate electrode voltage, independent of semiconducting materials. For p-type PDPP3T, the pre-applied voltage of 140 V results in the V<sub>TH</sub> shift from 4.8 V to 36.5 V, while the voltage of -140 V leads to  $V_{TH} = -19.4$  V. In comparison,  $V_{TH}$  of n-type PTzNDI-2FT is shifted from 16.8 V to 46.1 V when pre-applying 140 V to the gate electrode, and moves to 7.4 V with the pre-applied voltage of -100 V. As explained in Figure 4, these behaviors should be ascribed to the charge trappings in the bulk of the 300 nm thick SiO<sub>2</sub> dielectric, which creates an additional electric field and critically affects the charge transport in the conduction channel.

**Figure 5.** Chemical structures and transfer curves at different pre-applied gate voltages for (**a**) PDPP3T and (**b**) PTzNDI-2FT OFET.

### 3. Conclusions

In conclusion, we observe a large  $V_{TH}$  shift when pre-applying a voltage to the SiO<sub>2</sub> gate dielectric. Interestingly, such behavior remains even after surface modification of SiO<sub>2</sub> using HMDS SAM. It is assumed that the traps inside the SiO<sub>2</sub> bulk lead to the capture and release of electrons/holes under the condition of large pre-applied gate voltage, which affects the carrier concentration in the channel and causes the transistor threshold voltage to shift by about 80 V. This large  $V_{TH}$  shift induced by pre-applied gate voltage is further verified by using two other conjugated polymers. These results offer a new consideration for the design of OFETs and a new idea to further improve the stability of OFETs.

#### 4. Experiments

Materials: PffBT4T-2DT was purchased from Nanjing Zhiyan Ltd. PDPP3T and PTzNDI-2FT were synthesized according to the literature [51,52].

PFBT modification: After activation by using oxygen plasma for 30 s, the Au electrodes were functionalized with PFBT SAM by immersing the cleaned substrates into 10 mM PFBT solution in ethanol for 6 h. After this, the device surface was cleaned twice with ethanol and blown dry under nitrogen.

HMDS modification: The substrate was placed in a vacuum chamber and heated up to 130 °C. Exposure to HMDS vapor was maintained for 3 min.

Transistor fabrication and characterization: The substrates for OFET fabrication were purchased from Tianjin Semiconductor Technology Research Institute Ltd., in which heavily p-type doped silicon with 300 nm thick thermally grown SiO<sub>2</sub> was used as back-gate electrodes and the dielectric layer. Source and drain electrodes were defined by photolithography to obtain a channel length of 10 um and channel width of 200 um. Titanium with a thickness of 5 nm and gold with a thickness of 30 nm were sequentially deposited on the substrate through electron beam evaporation as the source and drain electrodes of the OFETs. 5 nm thick titanium was used for enhancing the adhesion of gold electrodes to substrates. The Au electrodes were functionalized with PFBT modification. After the PFBT SAM functionalization, the SiO<sub>2</sub> substrate was treated with HMDS modification to passivate the surface. Different organic semiconductor thin films were deposited by spin-coating at 1500 rpm for 60 s. After thin film deposition, the substrates were annealed at 100 °C for 30 min in a glovebox under a nitrogen atmosphere to remove the residual solvent. All electrical test results were measured using a Keithley-4200 Semiconductor Analyzer in a nitrogen atmosphere glovebox.

**Supplementary Materials:** The following supporting information can be downloaded at: https: //www.mdpi.com/article/10.3390/electronics12030540/s1, Figure S1: The transfer (a) and output (b) curves of the PffBT4T-2DT transistor; Figure S2: (a)  $I_{DS}^{0.5}$  vs  $V_{GS}$  plotting, where the data are from Figure 2 (a); (b) Saturation mobility at different pre-applied voltages.; Figure S3: (a) PffBT4T-2DT transistor transfer curves of -100 V and 100 V pre-applied voltage at the gate electrode for multiple times; (b) The transfer curves obtained by repeatedly pre-applied different voltages to the gate and drain electrodes simultaneously; Figure S4: Transfer curves of PffBT4T-2DT transistor without PFBT modification at different pre-applied voltages to the gate electrode. Figure S5: Hysteresis behaviors of PffBT4T-2DT (a) and PDPP3T (b) transistors before and after HMDS modification; Figure S6. (a) Preapplied a -140 V gate voltage, the relationship of HMDS treated device transfer curve with time; (b) Fitting the threshold voltage over time after a pre-applied -140 voltage by stretched exponential model; Figure S7: Output curves of PTzNDI-2FT transistor.

**Author Contributions:** Conceptualization, M.L., Y.G.; investigation, Y.G., J.D.; writing—review and editing, M.L., Y.G., J.N., C.D., S.L., L.L.; supervision, M.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the National Key R&D Program of China (Grant Nos. 2019YFA0706100, 2020YFA0210800, and 2021YFA0909400), the National Natural Science Foundation of China (Grant Nos. 62074163, 61890944, 61888102, 61720106013, and 22025402), and the Strategic Priority Research Program of the Chinese Academy of Sciences (Grant Nos. XDB30030000, XDB30030300, and XDB44000000).

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author.

Acknowledgments: M.L. acknowledges Rene Janssen for providing PDPP3T.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Schwartz, G.; Tee, B.C.K.; Mei, J.; Appleton, A.L.; Kim, D.H.; Wang, H.; Bao, Z. Flexible polymer transistors with high pressure sensitivity for application in electronic skin and health monitoring. *Nat. Commun.* 2013, *4*, 1859. [CrossRef] [PubMed]

- Sugiyama, M.; Uemura, T.; Kondo, M.; Akiyama, M.; Namba, N.; Yoshimoto, S.; Noda, Y.; Araki, T.; Sekitani, T. An ultraflexible organic differential amplifier for recording electrocardiograms. *Nat. Electron.* 2019, 2, 351–360. [CrossRef]

- Wang, W.; Wang, S.; Rastak, R.; Ochiai, Y.; Niu, S.; Jiang, Y.; Arunachala, P.K.; Zheng, Y.; Xu, J.; Matsuhisa, N.; et al. Straininsensitive intrinsically stretchable transistors and circuits. *Nat. Electron.* 2021, 4, 143–150. [CrossRef]

- 4. Dai, Y.; Hu, H.; Wang, M.; Xu, J.; Wang, S. Stretchable transistors and functional circuits for human-integrated electronics. *Nat. Electron.* **2021**, *4*, 17–29. [CrossRef]

- Yokota, T.; Nakamura, T.; Kato, H.; Mochizuki, M.; Tada, M.; Uchida, M.; Lee, S.; Koizumi, M.; Yukita, W.; Takimoto, A.; et al. A conformable imager for biometric authentication and vital sign measurement. *Nat. Electron.* 2020, *3*, 113–121. [CrossRef]

- 6. Wang, S.; Xu, J.; Wang, W.; Wang, G.J.N.; Rastak, R.; Molina-Lopez, F.; Chung, J.W.; Niu, S.; Feig, V.R.; Lopez, J.; et al. Skin electronics from scalable fabrication of an intrinsically stretchable transistor array. *Nature* **2018**, 555, 83–88. [CrossRef]

- Luo, Z.; Peng, B.; Zeng, J.; Yu, Z.; Zhao, Y.; Xie, J.; Lan, R.; Ma, Z.; Pan, L.; Cao, K.; et al. Sub-thermionic, ultra-high-gain organic transistors and circuits. *Nat. Commun.* 2021, 12, 1928. [CrossRef]

- Li, M.; Wang, J.; Xu, W.; Li, L.; Pisula, W.; Janssen, R.A.J.; Liu, M. Noncovalent semiconducting polymer monolayers for high-performance field-effect transistors. *Prog. Polym. Sci.* 2021, 117, 101394. [CrossRef]

- Deng, J.; Zheng, L.; Ding, C.; Guo, Y.; Xie, Y.; Wang, J.; Ke, Y.; Li, M.; Li, L.; Janssen, R.A.J. Determinant Role of Solution-State Supramolecular Assembly in Molecular Orientation of Conjugated Polymer Films. *Adv. Funct. Mater.* 2022, *3*, 2209195. [CrossRef]

- Dogan, T.; Verbeek, R.; Kronemeijer, A.J.; Bobbert, P.A.; Gelinck, G.H.; van der Wiel, W.G. Short-Channel Vertical Organic Field-Effect Transistors with High On/Off Ratios. *Adv. Electron. Mater.* 2019, *5*, 1900041. [CrossRef]

- Dahal, D.; Paudel, P.R.; Kaphle, V.; Radha Krishnan, R.K.; Lüssem, B. Influence of Injection Barrier on Vertical Organic Field Effect Transistors. ACS Appl. Mater. Interfaces 2022, 14, 7063–7072. [CrossRef] [PubMed]

- Chang, J.F.; Hou, K.S.; Yang, Y.W.; Wang, C.H.; Chen, Y.X.; Ke, H. Da Enhanced mobility for increasing on-current and switching ratio of vertical organic field-effect transistors by surface modification with phosphonic acid self-assembled monolayer. *Org. Electron.* 2020, *81*, 105689. [CrossRef]

- Teixeira da Rocha, C.; Haase, K.; Zheng, Y.; Löffler, M.; Hambsch, M.; Mannsfeld, S.C.B. Solution Coating of Small Molecule/Polymer Blends Enabling Ultralow Voltage and High-Mobility Organic Transistors. *Adv. Electron. Mater.* 2018, 4, 1800141. [CrossRef]

- 14. Haase, K.; Teixeira da Rocha, C.; Hauenstein, C.; Zheng, Y.; Hambsch, M.; Mannsfeld, S.C.B. High-Mobility, Solution-Processed Organic Field-Effect Transistors from C8-BTBT:Polystyrene Blends. *Adv. Electron. Mater.* **2018**, *4*, 1800076. [CrossRef]

- 15. Fratini, S.; Nikolka, M.; Salleo, A.; Schweicher, G.; Sirringhaus, H. Charge transport in high-mobility conjugated polymers and molecular semiconductors. *Nat. Mater.* **2020**, *19*, 491–502. [CrossRef] [PubMed]

- Zhao, J.; Tang, W.; Li, Q.; Liu, W.; Guo, X. Fully Solution Processed Bottom-Gate Organic Field-Effect Transistor with Steep Subthreshold Swing Approaching the Theoretical Limit. *IEEE Electron. Device Lett.* 2017, 38, 1465–1468. [CrossRef]

- Yang, F.; Sun, L.; Han, J.; Li, B.; Yu, X.; Zhang, X.; Ren, X.; Hu, W. Low-Voltage Organic Single-Crystal Field-Effect Transistor with Steep Subthreshold Slope. ACS Appl. Mater. Interfaces 2018, 10, 25871–25877. [CrossRef]

- Zschieschang, U.; Klauk, H. Low-voltage organic transistors with steep subthreshold slope fabricated on commercially available paper. Org. Electron. 2015, 25, 340–344. [CrossRef]

- Zessin, J.; Xu, Z.; Shin, N.; Hambsch, M.; Mannsfeld, S.C.B. Threshold Voltage Control in Organic Field-Effect Transistors by Surface Doping with a Fluorinated Alkylsilane. ACS Appl. Mater. Interfaces 2019, 11, 2177–2188. [CrossRef]

- Shin, N.; Zessin, J.; Lee, M.H.; Hambsch, M.; Mannsfeld, S.C.B. Enhancement of n-Type Organic Field-Effect Transistor Performances through Surface Doping with Aminosilanes. *Adv. Funct. Mater.* 2018, 28, 1802265. [CrossRef]

- 21. Kim, J.B.; Lee, D.R. Significance of the gate voltage-dependent mobility in the electrical characterization of organic field effect transistors. *Appl. Phys. Lett.* **2018**, *112*, 173301. [CrossRef]

- Gholamrezaie, F.; Andringa, A.M.; Roelofs, W.S.C.; Neuhold, A.; Kemerink, M.; Blom, P.W.M.; De Leeuw, D.M. Charge trapping by self-assembled monolayers as the origin of the threshold voltage shift in organic field-effect transistors. *Small* 2012, *8*, 241–245. [CrossRef] [PubMed]

- Mathijssen, S.G.J.; Spijkman, M.J.; Andringa, A.M.; Van Hal, P.A.; McCulloch, I.; Kemerink, M.; Janssen, R.A.J.; De Leeuw, D.M. Revealing buried interfaces to understand the origins of threshold voltage shifts in organic field-effect transistors. *Adv. Mater.* 2010, 22, 5105–5109. [CrossRef] [PubMed]

- Ahmed, R.; Kadashchuk, A.; Simbrunner, C.; Schwabegger, G.; Baig, M.A.; Sitter, H. Geometrical structure and interface dependence of bias stress induced threshold voltage shift in C60-based OFETs. ACS Appl. Mater. Interfaces 2014, 6, 15148–15153. [CrossRef] [PubMed]

- Choi, H.H.; Lee, W.H.; Cho, K. Bias-stress-induced charge trapping at polymer chain ends of polymer gate-dielectrics in organic transistors. *Adv. Funct. Mater.* 2012, 22, 4833–4839. [CrossRef]

- 26. Gomes, H.L.; Stallinga, P.; Dinelll, F.; Murgia, M.; Biscarini, F.; De Leeuw, D.M.; Muck, T.; Geurts, J.; Molenkamp, L.W.; Wagner, V. Bias-induced threshold voltages shifts in thin-film organic transistors. *Appl. Phys. Lett.* **2004**, *84*, 3184–3186. [CrossRef]

- Iqbal, H.F.; Ai, Q.; Thorley, K.J.; Chen, H.; McCulloch, I.; Risko, C.; Anthony, J.E.; Jurchescu, O.D. Suppressing bias stress degradation in high performance solution processed organic transistors operating in air. *Nat. Commun.* 2021, 12, 2352. [CrossRef]

- Park, S.; Kim, S.H.; Choi, H.H.; Kang, B.; Cho, K. Recent Advances in the Bias Stress Stability of Organic Transistors. *Adv. Funct. Mater.* 2020, 30, 1904590. [CrossRef]

- 29. Kahng, D.; Sze, S.M. A floating gate and its application to memory devices. Bell Syst. Tech. J. 1967, 46, 1288–1295. [CrossRef]

- 30. Kim, M.K.; Kim, I.J.; Lee, J.S. CMOS-compatible ferroelectric NAND flash memory for high-density, low-power, and high-speed three-dimensional memory. *Sci. Adv.* **2021**, *7*, eabe1341. [CrossRef]

- Baeg, K.J.; Khim, D.; Kim, J.; Yang, B.; Do Kang, M.; Jung, S.W.; You, I.K.; Kim, D.Y.; Noh, Y.Y. High-performance top-gated organic field-effect transistor memory using electrets for monolithic printed flexible nand flash memory. *Adv. Funct. Mater.* 2012, 22, 2915–2926. [CrossRef]

- Lee, S.; Seong, H.; Im, S.G.; Moon, H.; Yoo, S. Organic flash memory on various flexible substrates for foldable and disposable electronics. *Nat. Commun.* 2017, *8*, 725. [CrossRef] [PubMed]

- 33. Sekitani, T.; Yokota, T.; Zschieschang, U.; Klauk, H.; Bauer, S.; Takeuchi, K.; Takamiya, M.; Sakurai, T.; Someya, T. Organic nonvolatile memory transistors for flexible sensor arrays. *Science* **2009**, *326*, 1516–1519. [CrossRef] [PubMed]

- Di, C.A.; Wei, D.; Yu, G.; Liu, Y.; Guo, Y.; Zhu, D. Patterned graphene as source/drain electrodes for bottom-contact organic field-effect transistors. *Adv. Mater.* 2008, 20, 3289–3293. [CrossRef]

- Baeg, K.J.; Noh, Y.Y.; Ghim, J.; Kang, S.J.; Lee, H.; Kim, D.Y. Organic non-volatile memory based on pentacene field-effect transistors using a polymeric gate electret. *Adv. Mater.* 2006, *18*, 3179–3183. [CrossRef]

- Yang, S.Y.; Shin, K.; Park, C.E. The effect of gate-dielectric surface energy on pentacene morphology and organic field-effect transistor characteristics. *Adv. Funct. Mater.* 2005, 15, 1806–1814. [CrossRef]

- Noh, Y.Y.; Kim, J.J.; Yase, K.; Nagamatsu, S. Organic field-effect transistors by a wet-transferring method. *Appl. Phys. Lett.* 2003, 83, 1243–1245. [CrossRef]

- Li, M.; Marszalek, T.; Zheng, Y.; Lieberwirth, I.; Müllen, K.; Pisula, W. Modulation of Domain Size in Polycrystalline n-Type Dicyanoperylene Mono- and Bilayer Transistors. ACS Nano 2016, 10, 4268–4273. [CrossRef]

- 39. Li, M.; An, C.; Marszalek, T.; Baumgarten, M.; Müllen, K.; Pisula, W. Impact of Interfacial Microstructure on Charge Carrier Transport in Solution-Processed Conjugated Polymer Field-Effect Transistors. *Adv. Mater.* **2016**, *28*, 2245–2252. [CrossRef]

- Li, M.; Hinkel, F.; Müllen, K.; Pisula, W. Self-assembly and charge carrier transport of solution-processed conjugated polymer monolayers on dielectric surfaces with controlled sub-nanometer roughness. *Nanoscale* 2016, *8*, 9211–9216. [CrossRef]

- 41. Di, C.; Liu, Y.; Yu, G.; Zhu, D. Interface Engineering: An Effective Approach toward High-Performance Organic Field-Effect Transistors. *Acc. Chem. Res.* 2009, 42, 1573–1583. [CrossRef] [PubMed]

- 42. Asadi, K.; Wu, Y.; Cholamrezaie, F.; Rudolf, P.; Blom, P.W.M. Single-layer pentacene field-effect transistors using electrodes modified with self-assembled monolayers. *Adv. Mater.* **2009**, *21*, 4109–4114. [CrossRef]

- 43. Egginger, M.; Bauer, S.; Schwödiauer, R.; Neugebauer, H.; Sariciftci, N.S. Current versus gate voltage hysteresis in organic field effect transistors. *Mon. Fur Chem.* **2009**, *140*, 735–750. [CrossRef]

- Tsai, T.; Da Chang, J.W.; Wen, T.C.; Guo, T.F. Manipulating the hysteresis in poly(vinyl alcohol)-dielectric organic field-effect transistors toward memory elements. *Adv. Funct. Mater.* 2013, 23, 4206–4214. [CrossRef]

- Orgiu, E.; Locci, S.; Fraboni, B.; Scavetta, E.; Lugli, P.; Bonfiglio, A. Analysis of the hysteresis in organic thin-film transistors with polymeric gate dielectric. Org. Electron. 2011, 12, 477–485. [CrossRef]

- 46. Bürgi, L.; Sirringhaus, H.; Friend, R.H. Noncontact potentiometry of polymer field-effect transistors. *Appl. Phys. Lett.* **2002**, *80*, 2913–2915. [CrossRef]

- Mathijssen, S.G.J.; Cölle, M.; Gomes, H.; Smits, E.C.P.; De Boer, B.; McCulloch, I.; Bobbert, P.A.; De Leeuw, D.M. Dynamics of threshold voltage shifts in organic and amorphous silicon field-effect transistors. *Adv. Mater.* 2007, *19*, 2785–2789. [CrossRef]

- Park, D.W.; Lee, C.A.; Jung, K.D.; Park, B.G.; Shin, H.; Lee, J.D. Low hysteresis pentacene thin-film transistors using SiO<sub>2</sub>/crosslinked poly(vinyl alcohol) gate dielectric. *Appl. Phys. Lett.* 2006, 89, 263507. [CrossRef]

- 49. Yoo, H.; Ghittorelli, M.; Lee, D.K.; Smits, E.C.P.; Gelinck, G.H.; Ahn, H.; Lee, H.K.; Torricelli, F.; Kim, J.J. Balancing Hole and Electron Conduction in Ambipolar Split-Gate Thin-Film Transistors. *Sci. Rep.* **2017**, *7*, 5015. [CrossRef]

- 50. Yoo, H.; Lee, S.B.; Lee, D.K.; Smits, E.C.P.; Gelinck, G.H.; Cho, K.; Kim, J.J. Top-Split-Gate Ambipolar Organic Thin-Film Transistors. *Adv. Electron. Mater.* 2018, *4*, 1700536. [CrossRef]

- 51. Turbiez, M.; Leeuw, D.M.; De Janssen, A.J. Poly (diketopyrrolopyrrole—Terthiophene) for Ambipolar Logic and Photovoltaics. *Am. Chem. Soc.* 2009, 131, 16616–16617. [CrossRef]

- 52. Zhang, L.; Deng, W.; Wu, B.; Ye, L.; Sun, X.; Wang, Z.; Gao, K.; Wu, H.; Duan, C.; Huang, F.; et al. Reduced Energy Loss in Non-Fullerene Organic Solar Cells with Isomeric Donor Polymers Containing Thiazole π-Spacers. ACS Appl. Mater. Interfaces 2020, 12, 753–762. [CrossRef] [PubMed]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.