# **Brief Report Direct-Grown Helical-Shaped Tungsten-Oxide-Based Devices** with Reconfigurable Selectivity for Memory Applications

Ying-Chen Chen <sup>1,\*</sup>, Yifu Huang <sup>2</sup>, Sumant Sarkar <sup>3</sup>, John Gibbs <sup>4</sup> and Jack Lee <sup>2</sup>

- <sup>1</sup> Department of Electrical and Computer Engineering, Northern Arizona University, Flagstaff, AZ 86011, USA

- <sup>2</sup> Department of Electrical and Computer Engineering, The University of Texas at Austin,

- Austin, TX 78712, USA

- <sup>3</sup> Lam Research, Tualatin, OR 94538, USA

- <sup>4</sup> Department of Applied Physics and Materials Science, Northern Arizona University, Flagstaff, AZ 86011, USA

- \* Correspondence: ying-chen.chen@nau.edu

**Abstract:** In this study, a direct-grown helical-shaped tungsten-oxide-based (h-WO<sub>x</sub>) selection device is presented for emerging memory applications. The selectivity in the selection devices is from 10 to  $10^3$  with a low off-current of 0.1 to 0.01 nA. In addition, the selectivity of volatile switching in the h-WO<sub>x</sub> selection devices is reconfigurable with a pseudo RESET process on the one-time negative voltage operations. The helical-shaped selection devices with the glancing angle deposition (GLAD) method show good compatibility, low power consumption, good selectivity, and good reconfigurability for next-generation memory applications.

Keywords: helices; memristor; RRAM; selector; volatile switching

Citation: Chen, Y.-C.; Huang, Y.; Sarkar, S.; Gibbs, J.; Lee, J. Direct-Grown Helical-Shaped Tungsten-Oxide-Based Devices with Reconfigurable Selectivity for Memory Applications. *J. Low Power Electron. Appl.* 2022, *12*, 55. https:// doi.org/10.3390/jlpea12040055

Academic Editor: Andrea Acquaviva

Received: 25 August 2022 Accepted: 13 October 2022 Published: 15 October 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

## 1. Introduction

With high-demand computing, the emerging memory with high-density storage and computational functions attracts attention. An inevitable issue needs to be solved before enabling the high-density crossbar array, called "sneak path currents (SPC)", i.e., the crosstalk effect resulting from the leakage current contributed by the neighboring memory cells subverting the development of crossbar arrays [1,2]. Currently, the configuration of one transistor–one memory (1T-1R) is utilized to solve the SPC issue, which relies on the rectifying behavior of the three-terminal transistor to suppress the SPC and mitigate the programming errors in the memory array [3–6]. However, this approach with a three-terminal transistor integration increases the cost and fabrication complexity while limiting the scalability per bit and the whole memory array. The self-rectified memory and good performance selection device are in pressing need of development [6–8].

Recently, self-rectified memory applications without the integration of the selection devices were published. However, the filamentary-based memory has an intrinsic high off-current ( $\sim 10^{-6}$ ) after electroforming, which leads to the bottleneck of energy efficiency as well as noise immunity in the current self-rectified memory [9–12]. To mitigate the development gap between 1T-1R and self-rectified memory, the novel two-terminal selection device is proposed and demonstrated with simplified fabrication, low operation energy, and scalability. To investigate the system level's latency and writing energy, SPICE modeling on 1T-1R, dynamic random-access memory (DRAM), and resistive random-access memory (RRAM) ( $\sim 1$  Gb) have been reported [13]. The 2T-1R and 3T-1R configurations are also published to mitigate the SPC-induced operation errors while reducing the energy consumption [14–17]. Despite there are breakthroughs in circuit- and system-level studies, the device-level RRAM characteristics still lack investigation. To overcome the limitations on device-level memory development, the power consumption and SPC-induced errors in the array operation need an urgent solution. In this study, the direct-grown two-terminal selection device that uses the nano helical structures is presented with reconfigurable

selectivity. The results present the reconfigurable volatile switching (VS) behaviors of  $WO_x$  helical-shaped films, which is suggested as the solution for the SPC issue without compromising the structure simplicity, which enables the low power, high density, CMOS compatible technology towards the crossbar memory array applications.

#### 2. Results and Discussion

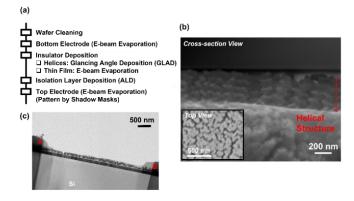

The fabrication process is shown in Figure 1a. After the wafer cleaning process, 100 nm of gold (Au) was deposited as the bottom electrode (BE) using a physical vapor deposition (PVD) method while keeping the substrate at an angle of 0 degree. The  $WO_x$  helices were grown using the glancing angle deposition (GLAD) method (Figure 1b) [18]. Briefly, the WO<sub>x</sub> source material (WO<sub>x</sub> pellet, Kurt J. Lesker) was kept in a Mo crucible, and e-beam deposition method was used to deposit the material on the substrate, while the substrate was rotated. Furthermore, the substrate was kept at an angle of 86 degrees with respect to the vapor plume, to achieve the shadow effect needed by GLAD to create helices. The helical-shaped thin film, i.e., insulator layers has been deposited by the e-beam evaporation including helical  $WO_x$  (h- $WO_x$ ). The total helical wire length was designed to be modified from 50 nm, 100 nm, 200 nm (approximately 1 full turn, and 4 turns of helix). The height of the helical structure is examined to be approximately 60 to 80% of the total wire length [19]. The growth of the helices occurred at a rate of around 0.7 Å/s. This was monitored using an in-vacuo quartz-crystal microbalance (Inficon, Bad Ragaz, Switzerland). Then, 5 nm of  $SiO_x$  has been deposited by atomic layer deposition (ALD) for isolating the top electrode from the bottom electrode and preventing the shortened circuit. The devices without the SiO<sub>x</sub> capping layer are fabricated as references. The Keysight B1500 with EPS probe station is utilized for electrical characterization and analysis.

**Figure 1.** (a) Fabrication process for helical-shaped nanostructure, (b) cross-section image of the helical structure by SEM image (inset: top view of as-deposited helical structures), (c) helical structure deposited and fill in the via opening by shadow masks.

The uniformity of the helical structure deposition is investigated. Figure 1b inset shows the top view by scanning electron microscopy (SEM) for 200 nm h-WO<sub>x</sub> thin film deposition without 5 nm of SiO<sub>x</sub> thin film. To investigate the coverage of the helical shape structure, the shadow mask in the sizes of 15, 50, 100  $\mu$ m in diameter was used during the depositing process. The cross-section of the via is shown with the helical structures, which demonstrates the good coverage with the GLAD method (Figure 1c). Noted the A-B is the cross-section of the via size with a diameter of 15  $\mu$ m designed shadow mask.

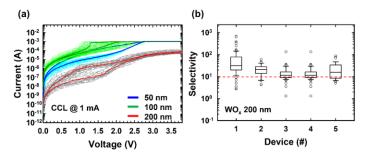

Figure 2a shows the current–voltage (I–V) characteristics in h-WO<sub>x</sub>-based devices of 50 nm, 100 nm, and 200 nm. The 100 DC cycles are tested with the SET compliance current limit (CCL) operation. The volatile switching behaviors are shown in helical-shaped WO<sub>x</sub>-based devices. The on-current reaches SET CCL of 1 mA in the devices with a helical layer of 50 and 100 nm (blue and green curves), while the self-compliance is observed in the device of 200 nm helical layer (red curve). The selectivity (S.L.) is defined as the current at on-voltage (i.e., 1 V) divided by the current at off-voltage (i.e., 0.3 V). The device

with a higher selectivity represents superior performance in reducing the SPC noise and crosstalk. The results show the h-WO<sub>x</sub> selection devices with active layers of 50 nm and 100 nm require the external current clamping circuit, and the power consumption in which is higher than those in devices of 200 nm h-WO<sub>x</sub> layer.

**Figure 2.** (a) I–V characteristics of volatile switching in WOx-based helical devices, (b) selectivity of WOx-based selection devices.

The off-current at the read voltage of 0.1 V is  $8 \times 10^{-8}$ ,  $2 \times 10^{-6}$ ,  $1.4 \times 10^{-9}$  A for 50 nm, 100 nm, 200 nm devices, respectively. That is, the standby power is reduced with thicker h-WO<sub>x</sub> thin film, while the device is idle without operations of reading and writing. Although the drive-on voltage of h-WO<sub>x</sub> device at 1.52 V which is around three times of the transistor device in 1T-1R (e.g., 0.6 V), the power is reduced by two orders of magnitude. The power consumption is reduced 14 nW with h-WO<sub>x</sub> selection devices, as compared with 3 mW in 1T-1R configuration. Figure 2b shows the device-to-device (D2D) variation for the selection devices with h-WO<sub>x</sub> of 200 nm. The selectivity is in the range from 10 to  $10^3$ , and the median selectivity of 50 cycles for each device is above order of magnitude. Noted the selectivity larger than an order of magnitude to maximum of  $10^3$  is sufficient for rectifying the non-volatile memory cell in the crossbar array. Future research on improving the selectivity [20,21] will continue by tailoring materials and device designs.

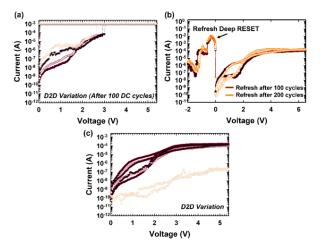

On the other hand, device reliability is the critical factor in evaluating the selection of devices. Figure 3a shows the one-time non-volatile switching after 100 DC cycling in four h-WO<sub>x</sub> (200 nm) selection devices at SET CCL of 1 mA, called the "pseudo SET process". The SET process with positive sweeping forms the conductive filament (i.e., low resistance state, LRS), and the RESET process with negative sweeping ruptures the filament (i.e., high resistance state, HRS) in a standard bipolar resistance random access memory (RRAM) device [22]. Herein, volatile switching is normally performed in devices before this pseudo SET process. That is, the starting current ranges from  $10^{-8}$  to  $10^{-10}$  A at 0.01 V. Notably, there is no forming process required in this helical-shaped device for volatile switching. That is, the volatile switching as shown in Figure 2a in the first cycle. The CCL of the electroforming process does not affect the device performance when it is below 1 mA. The forming CCL effect resulting in potential conductance quantization [23] will be discussed in our future work. In the memory crossbar array, the total due to leakage path from neighboring cells is still of micro-ampere scale which is the bottleneck the researchers tried to solve recently [24,25]. The volatile switching devices presented in this study show low current operation (<1  $\mu$ A) using helical-shaped microstructures for future low-power memory applications.

With the DC cycling, the device is suggested under continuous bias stress and reaches SET CCL of 1 mA at around 3 V. Despite the pseudo SET process occurring, the vs. of the selection device is reconfigurable. Figure 3b shows the one-time refresh pseudo-RESET process, which shows a two-step conductance drop in the negative polarity sweeping process. The pseudo SET process occurs after the 100 cycles of vs. behaviors at positive sweeping (Figure 2a), the deep RESET process is performed once in negative polarity sweeps (i.e., dark red curve in negative polarity, Figure 3b). Then, the vs. behaviors have been recovered as the dark red curve in positive polarity in Figure 3b for the next 100 cycles as the selection device. The second "one-time refresh pseudo-RESET process brings the

vs. behaviors in h-WO<sub>x</sub> selection devices (i.e., light orange curve, Figure 3b). Noted the sweeping step of 10 mV was performed in the negative pseudo-RESET process from 0 to -2 V. Figure 3c shows the reconfigured volatile switching after the pseudo-RESET process in the identical four devices as in Figure 3a. In short, the volatile switching as the selection device using a helical-shaped active layer is low-power, recoverable and reconfigurable with an effortless pseudo RESET. This is thought to be suggested the confinement of the WO<sub>x</sub> helices which mitigates the vertical electrical field stress as compared with the continuous thin film devices. Future work will be performed to understand the physical mechanisms in discontinuous helical-shaped active layer for two-terminal vertical selection devices.

**Figure 3.** (a) Shorted one-time non-volatile switching (SET CCL: 1 mA), (b) refreshed one-time deep RESET cycle after 100 and 200 DC cycles, (c) device-to-device variation (median of 100 cycles).

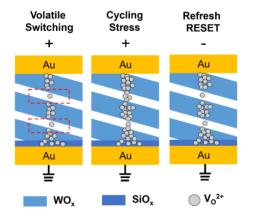

The schematic diagram shows the possible mechanism of filamentary structure evolution during the volatile switching, cycling stressing, and the fresh RESET cycle on the helical-shaped microstructure (Figure 4). The helical structure is a non-continuous structure in 2-dimensional direction, and a continuous structure in 3-dimensional direction (i.e., spiral structure). The discontinuous oxygen vacancy distribution leads to the non-uniform filamentary formation (left panel) during the positive polarity DC sweep, where the SiO<sub>x</sub> thin film of 5 nm is as the oxygen reservoir. After a number of DC cycling which stresses the device with the repeating operation, the filamentary structure is suggested to be connected, i.e., LRS. Since the filamentary structure in the pitch between each helical-turn in cross section, the filament is not as robust as in WO<sub>x</sub> continuous helical-wire structure (blue). With refreshing RESET cycle, the filament ruptured at the pitch between each helical turn, and recovered the volatile switching based on the discontinuous filament. An investigation on materials and physical modeling will be the scope of future work.

Figure 4. Schematics for filamentary structure under operation conditions.

### 3. Conclusions

For the first time, a direct-grown helical-shaped h-WO<sub>x</sub> selection device with volatile switching behaviors for emerging memory applications is presented. The selectivity of volatile switching in the h-WO<sub>x</sub> selection devices is recoverable and reconfigurable with a one-time pseudo-RESET process on the negative voltage sweeping operation. The helical-shaped selection devices with the GLAD method are demonstrated with good compatibility, simple fabrication, low power, good selectivity, and good reliability for future embedded functional memory and security applications in the BEOL process.

Author Contributions: Conceptualization, Y.-C.C.; methodology, J.G.; validation, Y.-C.C., S.S. and Y.H.; formal analysis, Y.-C.C.; investigation, Y.-C.C.; resources, Y.H. and J.L.; data curation, S.S., Y.H. and Y.-C.C.; writing—original draft preparation, Y.-C.C.; writing—review and editing, Y.-C.C. and J.L.; visualization, Y.-C.C.; supervision, Y.-C.C. and J.G.; project administration, Y.-C.C.; funding acquisition, Y.-C.C. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Not applicable.

Acknowledgments: We acknowledge the support and consultation provided from Yao-Feng Chang (Intel Corporation) and Chao-Cheng Lin (Taiwan Semiconductor Research Institute).

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Kannan, S.; Rajendran, J.; Karri, R.; Sinanoglu, O. Sneak-path testing of crossbar-based nonvolatile random access memories. *IEEE Trans. Nanotechnol.* **2013**, *12*, 413–426. [CrossRef]

- Huang, J.J.; Tseng, Y.M.; Hsu, C.W.; Hou, T.H. Bipolar nonlinear Ni/TiO<sub>2</sub>/Ni selector for 1S1R crossbar array applications. *IEEE Electron Device Lett.* 2011, 32, 1427–1429. [CrossRef]

- Banerjee, W.; Hwang, H. Understanding of Selector-Less 1S1R Type Cu-Based CBRAM Devices by Controlling Sub-Quantum Filament. Adv. Electron. Mater. 2020, 6, 2000488. [CrossRef]

- Ambrogio, S.; Balatti, S.; Milo, V.; Carboni, R.; Wang, Z.Q.; Calderoni, A.; Ramaswamy, N.; Ielmini, D. Neuromorphic learning and recognition with one-transistor-one-resistor synapses and bistable metal oxide RRAM. *IEEE Trans. Electron Devices* 2016, 63, 1508–1515. [CrossRef]

- Cassuto, Y.; Kvatinsky, S.; Yaakobi, E. Sneak-path constraints in memristor crossbar arrays. In Proceedings of the 2013 IEEE International Symposium on Information Theory, Istanbul, Turkey, 7–12 July 2013.

- Chou, C.T.; Hudec, B.; Hsu, C.W.; Lai, W.L.; Chang, C.C.; Hou, T.H. Crossbar array of selector-less TaOx/TiO<sub>2</sub> bilayer RRAM. *Microelectron. Reliab.* 2015, 55, 2220–2223. [CrossRef]

- Jeon, K.; Kim, J.; Ryu, J.J.; Yoo, S.-J.; Song, C.; Yang, M.K.; Seok, D.; Kim, G.H. Self-rectifying resistive memory in passive crossbar arrays. *Nat. Commun.* 2021, 12, 2968. [CrossRef] [PubMed]

- Lin, C.Y.; Chen, P.H.; Chang, T.C.; Huang, W.C.; Tan, Y.F.; Lin, Y.H.; Chen, W.C.; Lin, C.C.; Chang, Y.F.; Chen, Y.C.; et al. A comprehensive study of enhanced characteristics with localized transition in interface-type vanadium-based devices. *Mater. Today Phys.* 2020, *13*, 100201. [CrossRef]

- 9. Hsu, Y.L.; Chang, Y.F.; Chung, W.M.; Chen, Y.C.; Lin, C.C.; Leu, J. SiCxNy-based resistive and threshold switching by using single precursor plasma-enhanced atomic layer deposition. *Appl. Phys. Lett.* **2020**, *116*, 213502. [CrossRef]

- Chen, Y.C.; Lin, C.C.; Chang, Y.F. Post-moore memory technology: Sneak path current (spc) phenomena on rram crossbar array and solutions. *Micromachines* 2021, 12, 50. [CrossRef] [PubMed]

- 11. Qin, L.; Cheng, S.; Xie, B.; Wei, X.; Jie, W. Co-existence of bipolar nonvolatile and volatile resistive switching based on WO3 nanowire for applications in neuromorphic computing and selective memory. *Appl. Phys. Lett.* **2022**, 121, 093502. [CrossRef]

- Lee, H.D.; Kim, S.G.; Cho, K.; Hwang, H.; Choi, H.; Lee, J.; Lee, S.H.; Lee, H.J.; Suh, J.; Chung, S.O.; et al. Integration of 4F2 selector-less crossbar array 2Mb ReRAM based on transition metal oxides for high density memory applications. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 151–152.

- Mao, M.; Cao, Y.; Yu, S.; Chakrabarti, C. Optimizing latency, energy, and reliability of 1T1R ReRAM through appropriate voltage settings. In Proceedings of the 2015 33rd IEEE International Conference on Computer Design (ICCD), New York, NY, USA, 18–21 October 2015; pp. 359–366.

- Mehra, R.; Nibhanupudi, S.S.T.; Kulkarni, J.P. Statistical Analysis of 2T1R Gain-Cell RRAM Bitcell for Area Efficient, High-Performance, and Reliable Multi-level Cell Operation. In Proceedings of the 2022 Device Research Conference (DRC), Columbus, OH, USA, 26–29 June 2022; pp. 1–2.

- Yousefi, A.; Eslami, N.; Moaiyeri, M.H. A Reliable and Energy-Efficient Nonvolatile Ternary Memory Based on Hybrid Fin-FET/RRAM Technology. *IEEE Access* 2022, 10, 105040–105051. [CrossRef]

- Wang, L.; Ye, W.; Lai, J.; Liu, J.; Yang, J.; Si, X.; Huo, C.; Dou, C.; Xu, X.; Liu, Q.; et al. A 14nm 100Kb 2T1R Transpose RRAM with >150X resistance ratio enhancement and 27.95% reduction on energy-latency product using low-power near threshold read operation and fast data-line current stabling scheme. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2.

- Zhang, W.; Wang, S.; Li, Y.; Xu, X.; Dong, D.; Jiang, N.; Wang, F.; Guo, Z.; Fang, R.; Dou, C.; et al. Few-shot graph learning with robust and energy-efficient memory-augmented graph neural network (MAGNN) based on homogeneous computing-in-memory. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022; pp. 224–225.

- Sarkar, S.; Behunin, R.O.; Gibbs, J.G. Shape-dependent, chiro-optical response of uv-active, nanohelix metamaterials. *Nano Lett.* 2019, 19, 8089–8096. [CrossRef] [PubMed]

- Gibbs, J.G.; Sarkar, S.; Holterhoff, A.L.; Li, M.; Castañeda, J.; Toller, J. Engineering the Dynamics of Active Colloids by Targeted Design of Metal–Semiconductor Heterojunctions. *Adv. Mater. Interfaces* 2019, *6*, 1801894. [CrossRef]

- 20. Wang, M.; Wang, W.; Leow, W.R.; Wan, C.; Chen, G.; Zeng, Y.; Yu, J.; Liu, Y.; Cai, P.; Wang, H.; et al. Enhancing the matrix addressing of flexible sensory arrays by a highly nonlinear threshold switch. *Adv. Mater.* **2018**, *30*, 1802516. [CrossRef] [PubMed]

- Jiang, H.; Belkin, D.; Savel'ev, S.E.; Lin, S.; Wang, Z.; Li, Y.; Joshi, S.; Midya, R.; Li, C.; Rao, M.; et al. A novel true random number generator based on a stochastic diffusive memristor. *Nat. Commun.* 2017, *8*, 882. [CrossRef] [PubMed]

- Chen, Y.C.; Chang, Y.F.; Lin, C.Y.; Wu, X.; Xu, G.; Fowler, B.; Chang, T.C.; Lee, J.C. Built-in nonlinear characteristics of low power operating one-resistor selector-less RRAM by stacking engineering. *ECS Trans.* 2017, *80*, 923. [CrossRef]

- Korolev, D.S.; Belov, A.I.; Okulich, E.V.; Okulich, V.I.; Guseinov, D.V.; Sidorenko, K.V.; Shuisky, R.A.; Antonov, I.N.; Gryaznov, E.G.; Gorshkov, O.N.; et al. Manipulation of resistive state of silicon oxide memristor by means of current limitation during electroforming. *Superlattices Microstruct.* 2018, 122, 371–376. [CrossRef]

- Vaziri, S.; Datye, I.M.; Ambrosi, E.; Khan, A.I.; Kwon, H.; Wu, C.H.; Hsu, C.F.; Guy, J.; Lee, T.Y.; Wong, H.S.; et al. First Fire-free, Low-voltage (~1.2 V), and Low Off-current (~3 nA) SiOxTey Selectors. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022; pp. 324–325.

- Jeon, D.S.; Dongale, T.D.; Kim, T.G. Low power Ti-doped NbO<sub>2</sub>-based selector device with high selectivity and low OFF current. J. Alloys Compd. 2021, 884, 161041. [CrossRef]