# Brief Report High-Temperature Annealing Effects on Atomically Thin Tungsten Diselenide Field-Effect Transistor

Muhammad Atif Khan, Muhammad Qasim Mehmood 🗈 and Yehia Massoud \*

Innovative Technologies Laboratories (ITL), King Abdullah University of Science and Technology (KAUST), Thuwal 23955, Saudi Arabia

\* Correspondence: yehia.massoud@kaust.edu.sa

**Abstract:** Two-dimensional (2D) material-based devices are expected to operate under high temperatures induced by Joule heating and environmental conditions when integrated into compact integrated circuits for practical applications. However, the behavior of these materials at high operating temperatures is obscure as most studies emphasize only room temperature or low-temperature operation. Here, the high-temperature electrical response of the tungsten diselenide (WSe<sub>2</sub>) fieldeffect transistor was studied. It is revealed that 350 K is the optimal annealing temperature for the WSe<sub>2</sub> transistor, and annealing at this temperature improves on-current, field-effect mobility and on/off ratio around three times. Annealing beyond this temperature (360 K to 670 K) adversely affects the device performance attributed to the partial oxidation of WSe<sub>2</sub> at higher temperatures. An increase in hysteresis also confirms the formation of new traps as the device is annealed beyond 350 K. These findings explicate the thermal stability of WSe<sub>2</sub> and can help design 2D materials-based durable devices for high-temperature practical applications.

check for updates

Citation: Khan, M.A.; Mehmood, M.Q.; Massoud, Y. High-Temperature Annealing Effects on Atomically Thin Tungsten Diselenide Field-Effect Transistor. *Appl. Sci.* 2022, *12*, 8119. https://doi.org/10.3390/ app12168119

Academic Editors: Filippo Giannazzo and Ivan Shtepliuk

Received: 22 July 2022 Accepted: 12 August 2022 Published: 13 August 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). Keywords: annealing; 2D materials; WSe<sub>2</sub>; mobility; field-effect transistor; thermal stability

## 1. Introduction

Since the invention of the transistor in 1947, silicon has become the material of choice for electronics [1–4] and photonics applications [5–8]. For the last few decades, enormous efforts have been made by the scientific community to find an alternative to silicon as a material of choice for future electronics [9–11]. It has been long appreciated that carbon nanotubes (CNTs) possess the required potential to be an ideal electronics material [12–16]. However, the challenges that arise from the non-uniform and imperfect growth of CNTs could not be resolved [12]. Since the discovery of graphene in 2004, 2D materials have emerged as a strong candidate for future high-speed and low-power electronics [17–20]. Two-dimensional materials possess several intrinsic properties like quantum confinement, a reasonable large bandgap, ease of fabrication, strong light-matter interaction, ability to form heterostructures and strong gate modulation, making them a suitable material for future electronics as well as photonics applications [21–24]. Among the 2D materials family, transition metal dichalcogenides (TMDs) are particularly of interest. WSe2 is a prominent member of TMDs because of its ambipolar behavior, large spin-orbit coupling and optical properties [25]. Studies showed the application of WSe<sub>2</sub> not only in electronic applications such as inverters and Schottky diodes [26] but also in photonic applications such as photodetectors, single-photon emitters and light-emitting diodes [27].

Until now, most of the studies have investigated the properties of WSe<sub>2</sub> at either room temperature or cryogenic temperatures [28]. While these studies were successful in understanding the intrinsic properties of the materials, there have been very few studies investigating the behavior of the material at high temperatures. For practical applications, 2D materials are expected to operate under high thermal stress caused by Joule heating in integrated circuits or local heating due to incident light in photonic applications [29–31].

Further, due to low thermal conductivity and heat capacity as well as high surface area, these materials are expected to endure temperatures higher than bulk materials such as Si and GaAs [32–36]. Therefore, it is essential to test the WSe<sub>2</sub> devices at high operating temperatures and monitor their performance under these conditions.

In this work, we designed an experimental setup to investigate the changes in the electrical behavior of the WSe<sub>2</sub> device after being exposed to high annealing temperatures. The investigation was carried out using a homemade probe station that can also anneal the devices in a nitrogen environment so that there is no need to take out the device after annealing. The device was annealed to temperatures ranging from 300 K to 670 K (step size: 10 K), and the electrical characterization of the device was performed at 300 K after each cycle of annealing. It was found that 350 K is the optimal annealing temperature for WSe<sub>2</sub>, which improves the device performance by eliminating the adsorbed species and chemical residue. Annealing at temperatures higher than 350 K adversely affects the device performance. The effects of annealing on the transfer characteristic curve, on/off ratio, field-effect mobility and hysteresis were investigated.

### 2. Materials and Methods

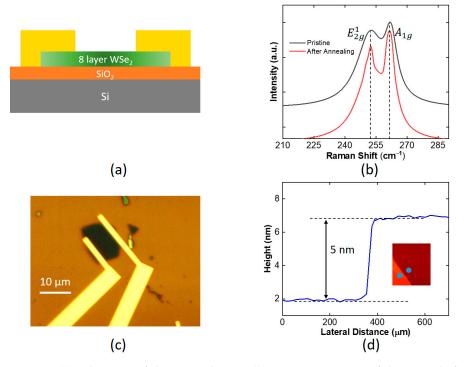

Figure 1a,c shows the schematic drawing and optical microscope image of the WSe<sub>2</sub> device. In order to fabricate this device, thin WSe<sub>2</sub> flakes were produced from the bulk WSe<sub>2</sub> crystal by the standard exfoliation method using scotch tape. The flakes were then transferred on a silicon substrate capped with 300 nm SiO<sub>2</sub>. An optical microscope was used to scan the substrate and identify suitable flakes, followed by Raman spectroscopy and atomic force microscopy (AFM). The back gated devices were prepared by electron beam lithography followed by metal deposition in an electron beam evaporation chamber. Electron beam lithography was used to make contact patterns on the selected WSe<sub>2</sub> flake. Titanium/gold (Ti/Au) with a thickness of 10/40 nm were chosen as contact materials as Ti forms Ohmic-like contacts with WSe<sub>2</sub>. The metal deposition was carried out in an electron beam evaporation chamber, followed by the lift-off in acetone.

**Figure 1.** (a) Schematic of the WSe<sub>2</sub> device. (b) Raman spectrum of the WSe<sub>2</sub> before and after annealing. (c) Optical microscope image of the device. (d) AFM image and height profile of the WSe<sub>2</sub> layer.

Figure 1b illustrates the Raman spectrum of the device taken by a 532 nm laser. The signature WSe<sub>2</sub> Raman peaks,  $E_{2g}^1$  and  $A_{1g}$ , can be seen at 252 cm<sup>-1</sup> and 261cm<sup>-1</sup>, respectively [37,38]. The presence of these two peaks not only confirms the material to be WSe<sub>2</sub> but also indicates that the flake thickness is more than four layers [22,23]. The Rama n spectroscopy was performed after annealing at 673 K as well. The comparison of the Raman spectrum before and after annealing is discussed in the later part. In order to accurately determine the WSe<sub>2</sub> thickness, atomic force microscopy (AFM) was carried out. Figure 1d presents the AFM image of the WSe<sub>2</sub> flake as well as the line profile between the two points shown in Figure 1d. It can be seen that the flake thickness is 5 nm, which corresponds to eight layers of WSe<sub>2</sub>.

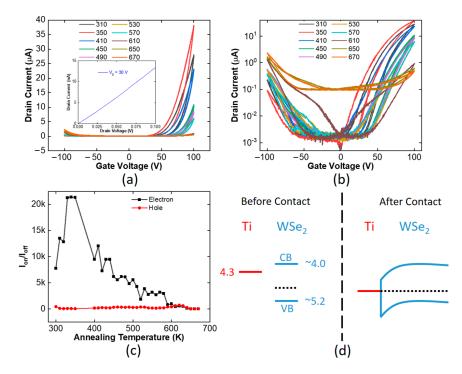

The transfer characteristics curves of the device at a constant source-drain voltage of 1 V measured at 300 K after annealing at different temperatures is shown in Figure 2. The influence of annealing on the device properties was systematically investigated by annealing the device at a target temperature for 30 min in a Nitrogen environment and then measuring its transfer characteristics curve at 300 K. The process was repeated for temperatures ranging from 310 K to 670 K with a step size of 10 K. In Figure 2, however, for better visibility, transfer curves are shown for selected annealing temperatures only. It can be seen that the device exhibits ambipolar behavior with hole-dominated transport for negative gate voltages and electron-dominated transport for positive gate voltages. After annealing at 310 K, the electron current is almost an order of magnitude higher than the hole current. In most studies, WSe<sub>2</sub> exhibit p-dominant transport; however, in the present study, n-dominant transport can be attributed to the Ti contacts. As shown in the schematic band diagram in Figure 2d, Ti has a work function of 4.3 eV, which is closer to the conduction band of WSe<sub>2</sub> [39,40]. Therefore, Ti can facilitate the injection of electrons in the conduction band of WSe<sub>2</sub> by forming good Ohmic-like contacts. At the same time, Ti forms a large Schottky barrier with the valence band of WSe<sub>2</sub>. This Schottky barrier results in electron transport being more prominent than the hole current. The inset of Figure 2a represents the output curve  $(I_d - V_d)$  of the WSe<sub>2</sub> device, and Ohmic-like linear characteristics can be seen there.

For the positive gate region (electron transport), as the annealing temperature is increased up to 350 K, an increase in the drain current as well as on/off ratio (ratio of on current to the off current of the device) is observed. As annealing temperature increases from 300 K to 350 K, the on/off ratio increases from 8000 to 22,000, whereas maximum on current increases from 14  $\mu$ A to 37  $\mu$ A. This observation of enhanced device performance after annealing is consistent with the previous studies in the literature [41]. The annealing improves the device's performance by removing the contaminants, adsorbed moisture and chemical residues from the surface of WSe<sub>2</sub> [41]. Two-dimensional materials possess a high surface-to-volume ratio and are extremely sensitive to the changes at the interface; therefore, annealing can drastically improve the device's performance. However, as the annealing temperature is increased beyond 350 K, the device performance gradually deteriorates. Overall, a decrease in device current as well as on/off ratio can be seen when the annealing temperature exceeds 350 K. The maximum current reduces from 37  $\mu$ A to 1.5  $\mu$ A, and the on/off ratio reduces from 22,000 to 1000 as the annealing temperature is gradually increased from 350 K to 590 K. Previous studies reported that  $WSe_2$  oxidizes to  $WO_x$  at high temperatures [42,43]. The oxidation of 2D materials differs from bulk materials as these materials show higher reactivity at the edges and defect sites only. The effects of oxidation on the electrical characteristics of the WSe<sub>2</sub> device can be seen in this temperature range (350 K to 590 K), where not only the on/off ratio and total current reduced but a decrease in the subthreshold swing can also be observed. It is safe to say that higher thermal and electrical stress has induced structural and chemical changes in the WSe<sub>2</sub>, which is further explained in the latter part. From 590 K to 670 K, the device behavior changes from semiconducting to fully conducting with very little gate control. The on/off ratio in the region is less than 10, and the off current has increased several orders of magnitude. In

order to obtain further insight into the device behavior, we extracted field-effect mobility and hysteresis of the device.

**Figure 2.** (a) Transfer characteristics curve of the WSe<sub>2</sub> device measured at 300 K after annealing at different temperatures on a linear scale (legend shows the annealing temperature in Kelvin, and inset represents the  $I_d$ - $V_d$  curve of the device). (b) Transfer characteristics curve of the WSe<sub>2</sub> device measured at 300 K after annealing at different temperatures on a semi-logarithmic scale (legend shows the annealing temperature in Kelvin). (c) The ratio of on current to the off current of the device as a function of annealing temperatures. (d) Schematic band diagram showing Ti and WSe<sub>2</sub> before and after contact.

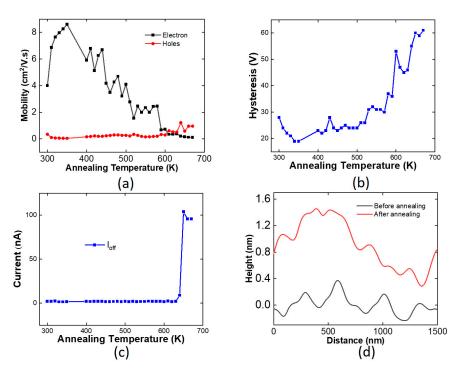

Figure 3 illustrates the field effect mobility as well as hysteresis as a function of annealing temperature. The field-effect mobility was extracted for electrons as well as holes using the following equation:

$$\mu = \frac{L}{W} \frac{g_m}{C_{ox} V_d}$$

In this equation, L and W are the total channel length and width, respectively, and  $C_{ox}$  is the back gate silicon dioxide capacitance per unit area, calculated by  $C_{ox} = \varepsilon_0 \cdot \varepsilon_r / d$ . Here,  $\varepsilon_0 = 8.85 \times 10^{-12}$  Fm<sup>-1</sup> is the permittivity of free space, and  $\varepsilon_r = 3.9$  is the relative permittivity of SiO<sub>2</sub> and d is SiO<sub>2</sub> thickness (300 nm).  $g_m$  is the trans-conductance obtained from the slope of each transfer curve,  $V_d$  is the applied drain voltage and  $\mu$  is the field effect mobility. A similar trend for electron mobility can also be seen in Figure 3, where initially, electron mobility increases from  $4 \text{ cm}^2/\text{V}$ s to  $9 \text{ cm}^2/\text{V}$ s as the annealing temperature is increased from 300 to 350 K. The mobility in 2D materials is limited by the scattering, and an improvement in mobility indicates a reduction in scattering. All the measurements were performed at 300 K, so it was safe to rule out any change in phonon scattering. Therefore, the increase in electron mobility can be attributed to a cleaner WSe<sub>2</sub> surface enabled by thermal annealing. As observed previously, in the temperature range of 360 K to 590 K, a consistent drop in electron mobility can be seen. One can also observe three distinct regions in the mobility curve: the mobility increases from 300 K to 350 K and from 350 K to 590 K, mobility gradually reduces from 9 cm<sup>2</sup>/V.s to 2.5 cm<sup>2</sup>/V.s and it reaches  $0.1 \text{ cm}^2/\text{V}$  s at 670 K. This trend of mobility and device current reflects that 350 K is the optimal annealing temperature for WSe<sub>2</sub>. Until this temperature, annealing improves the

device's performance by removing the contaminants, adsorbed moisture and chemical residues from the surface of WSe<sub>2</sub> [41]. Beyond 350 K, the high temperature starts to oxidize  $WSe_2$  and alter its chemical composition. As  $WSe_2$  becomes oxidized to  $WO_x$ , new traps are created at the WSe<sub>2</sub>-WO<sub>x</sub> interface, which results in a reduction in electron mobility [42,43]. The presence of hysteresis in the transfer curve is an indicator of charge traps in a device, so we investigated the hysteresis behavior of our device, as shown in Figure 3b. It is defined as the threshold voltage difference between the forward and reverse gate voltage sweep. Three distinct regions are also visible here; from 300 K to 350 K, hysteresis reduces, indicating the removal of traps and surface contaminants from WSe<sub>2</sub>. It gradually increases from 350 K to 590 K and increases exponentially from there onwards. Since hysteresis is an indicator of traps, it can be said that as WSe<sub>2</sub> becomes oxidized beyond 350 K, new traps are created, which degrade device performance by causing a reduction in electron mobility and on/off ratio. Figure 3c presents the off current as a function of annealing, which remains almost constant except at temperatures beyond 630 K, where chemical changes in  $WSe_2$  result in complete loss of gate control. The comparison of Raman (Figure 1d) and AFM measurements (Figure 3d) before and after the annealing give insight into the chemical changes induced by the thermal stress. In the Raman spectrum, the quenching of Raman peaks after annealing points to partial oxidation of WSe2 and the formation of new traps [44]. The average surface roughness before annealing was 320 pm, which was increased to 450 pm after annealing. The increased surface roughness in AFM measurement also corresponds to the formation of new traps. The observations such as quenching in the Raman spectrum, increased overall conductivity of WSe2, an increase in p-type behavior and an increase in surface roughness can be attributed to partial oxidation of  $WSe_2$  to  $WO_x$ as reported in previous studies [43-48]. Based on these observations, it can be assumed that in our WSe<sub>2</sub> device, the WSe<sub>2</sub> became oxidized during high-temperature annealing. However, this could be one of the reasons, and the exact nature of chemical changes still needs to be established.

**Figure 3.** (a) The field-effect mobility of the  $WSe_2$  device as a function of annealing temperature. (b) The hysteresis of the device as a function of annealing temperature. (c) The off current of the device as a function of annealing temperature. (d) Surface roughness of  $WSe_2$  as measured by AFM before and after annealing.

Thus far, we have discussed the positive gate region of Figures 2 and 3 mostly. For the negative region, the mobility and on/off ratio do not vary substantially with the annealing indicating that the hole transport is not limited by the channel imperfections. As shown in Figure 2, the bottleneck in hole transport is the Schottky contacts. Ti is used as a contact metal that can form a relatively large Schottky barrier with the valence band of WSe<sub>2</sub>, thus limiting the hole transport. This Schottky barrier results in low mobility and low current in the negative gate region and cannot be improved with annealing. Therefore, annealing does not affect the hole transport other than at temperatures beyond 590 K, where chemical changes in WSe<sub>2</sub> result in the channel becoming accumulated with the carriers completely and also results in a reduction in the effective Schottky barrier. This reduction results in enhanced hole current and hole mobility, as seen in Figure 3.

#### 4. Conclusions

In conclusion, we systematically investigated the thermal stability of the WSe<sub>2</sub> transistor by annealing it in a nitrogen environment at different temperatures. The effects of annealing on transfer curve, field-effect mobility and hysteresis were investigated. It was found that 350 K is the optimal annealing temperature that significantly improves the electrical characteristics of the WSe<sub>2</sub> transistor. Annealing beyond this temperature adversely affects the device's performance by oxidizing WSe<sub>2</sub> and permanently changing its electrical properties. Our findings elucidate the thermal stability of WSe<sub>2</sub> and can be useful to design 2D materials-based practical and durable devices to be operated at moderate or high temperatures.

Author Contributions: Conceptualization, M.A.K., M.Q.M. and Y.M.; methodology, M.A.K.; software, M.A.K.; validation, M.A.K., M.Q.M. and Y.M.; formal analysis, M.A.K. and M.Q.M.; investigation, M.A.K. and M.Q.M.; resources, Y.M.; data curation, M.A.K. and M.Q.M.; writing—original draft preparation, M.A.K.; writing—review and editing, M.A.K., M.Q.M. and Y.M.; visualization, M.A.K. and M.Q.M.; supervision, Y.M.; project administration, Y.M.; funding acquisition, Y.M. All authors have read and agreed to the published version of the manuscript.

**Funding:** The authors would like to acknowledge the research funding to the KAUST Innovative Technologies Laboratories (ITL) from King Abdullah University of Science and Technology (KAUST).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

**Data Availability Statement:** Data underlying the results presented in this paper are not publicly available at this time but may be obtained from the authors upon reasonable request.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- Massoud, Y.; White, J. Managing On-Chip Inductive Effects. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 2002, 10, 789–798. [CrossRef]

- Hosseini, A.; Ragheb, T.; Massoud, Y. A Fault-Aware Dynamic Routing Algorithm for On-Chip Networks. In Proceedings of the 2008 International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 May 2008; pp. 2653–2656.

- Massoud, Y.; White, J. Simulation and Modeling of the Effect Substrate Conductivity on Coupling Inductance and Circuit Crosstalk. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 2002, 10, 286–291. [CrossRef]

- Massoud, Y.; Ismail, Y. Grasping the Impact of On-Chip Inductance in High Speed ICs. IEEE Circuits Devices Mag. 2001, 17, 14–21. [CrossRef]

- Hosseini, A.; Nejati, H.; Massoud, Y. Triangular lattice plasmonic photonic band gaps in subwavelength metal-insulator-metal waveguide structures. *Appl. Phys. Lett.* 2008, 92, 013116. [CrossRef]

- Ijaz, S.; Rana, A.S.; Ahmad, Z.; Zubair, M.; Massoud, Y.; Mehmood, M.Q. The Dawn of Meta-devices: From Contemporary Designs to Exotic Applications. *Adv. Devices Instrum.* 2022, 2022, 9861078. [CrossRef]

- Naveed, M.A.; Kim, J.; Javed, I.; Ansari, M.A.; Seong, J.; Massoud, Y.M.; Badloe, T.; Kim, I.; Riaz, K.; Zubair, M.; et al. Novel Spin-Decoupling Strategy in Liquid Crystal-Integrated Metasurfaces for Interactive Meta-Displays. *Adv. Opt. Mater.* 2022, 10, 2200196. [CrossRef]

- Hosseini, A.; Massoud, Y. Nanoscale surface plasmon based resonator using rectangular geometry. *Appl. Phys. Lett.* 2007, 90, 181102. [CrossRef]

- 9. Macilwain, C. Silicon down to the win. *Nature* 2005, 436, 22.

- Alam, A.; Massoud, Y. RLC ladder model for scattering in single metallic nanoparticles. *IEEE Trans. Nanotechnol.* 2006, 5, 491–498. [CrossRef]

- Massoud, Y.; White, J. Improving the Generality of the Fictitious Magnetic Charge Approach to Computing Inductances in the Presence of Permeable Materials. In Proceedings of the IEEE/ACM Design Automation Conference, New Orleads, LA, USA, 10–14 June 2002; pp. 552–555.

- 12. Peng, L.; Zhang, Z.; Whang, S. Carbon nanotube electronics: Recent advances. Mater. Today 2014, 17, 433–442. [CrossRef]

- 13. Nieuwoudt, A.; Massoud, Y. Understanding the Impact of Inductance in Carbon Nanotube Bundles for VLSI Interconnect using Scalable Modeling Techniques. *IEEE Trans. Nanotechnol.* **2006**, *5*, 758–765. [CrossRef]

- 14. Massoud, Y.; Nieuwoudt, A. Modeling and Design Challenges and Solutions for Carbon Nanotube-Based Interconnect in Future High-Performanc Integrated Circuits. *ACM J. Emerg. Technol. Comput. Syst.* **2006**, *2*, 155–196. [CrossRef]

- Nieuwoudt, A.; Massoud, Y. On the Optimal Design, Performance, and Reliability of Future Carbon Nanotube-Based Interconnect Solutions. *IEEE Trans. Electron Devices* 2008, 55, 2097–2110. [CrossRef]

- Nieuwoudt, A.; Massoud, Y. On the Impact of Process Variations for Carbon Nanotube Bundles for VLSI Interconnect. *IEEE Trans. Electron. Devices* 2007, 54, 446–455. [CrossRef]

- Singh, V.; Joung, D.; Zhai, L.; Das, S.; Khondaker, S.I.; Seal, S. Graphene-based materials: Past, present and future. *Prog. Mater. Sci.* 2011, 56, 1178–1271. [CrossRef]

- 18. Li, X.; Zhu, H. Two-dimensional MoS<sub>2</sub>: Properties, preparation, and applications. J. Materiomics 2015, 1, 33–44. [CrossRef]

- 19. Hosseini, A.; Nieuwoudt, A.; Massoud, Y. Optimizing Dielectric Strips Over a Metallic Substrate for Subwavelength Light Confinement. *IEEE Photonics Lett.* 2007, 19, 522–524. [CrossRef]

- Massoud, Y.; Majors, S.; Bustami, T.; White, J. Layout Techniques for Minimizing On-Chip Interconnect Self Inductance. In Proceedings of the IEEE/ACM Design Automation Conference, San Francisco, CA, USA, 15–19 June 1998; pp. 566–571.

- 21. Geim, K.; Grigorieva, I.V. Van der Waals heterostructures. Nature 2013, 499, 419–425. [CrossRef]

- 22. Novoselov, K.S.; Mishchenkoa, A.; Carvalhoand, A.; Neto, A.H.C. 2D materials and van der Waals heterostructures. *Science* 2016, 353, 6298. [CrossRef]

- 23. Alam, M.; Massoud, Y. A closed-form analytical model for single nanoshells. IEEE Trans. Nanotechnol. 2006, 5, 265–272. [CrossRef]

- 24. Hosseini, A.; Massoud, Y. A low-loss metal-insulator-metal plasmonic bragg reflector. *Opt. Express* **2006**, *14*, 11318–11323. [CrossRef] [PubMed]

- 25. Tian, H.; Chin, M.L.; Najmaei, S.; Guo, Q.; Xia, F.; Wang, H.; Dubey, M. Optoelectronic devices based on two-dimensional transition metal dichalcogenides. *Nano Res.* **2016**, *9*, 1543–1560. [CrossRef]

- Wu, H.; Yan, Z.; Xie, Z.; Zhu, S. WSe<sub>2</sub>/Pd Schottky diode combining van der Waals integrated and evaporated metal contacts. *Appl. Phys. Lett.* 2021, 119, 213102. [CrossRef]

- Ross, J.S.; Klement, P.; Jones, A.M.; Ghimire, N.J.; Yan, J.; Mandrus, D.G.; Taniguchi, T.; Watanabe, K.; Kitamura, K.; Yao, W.; et al. Electrically tunable excitonic light-emitting diodes based on monolayer WSe<sub>2</sub> p–n junctions. *Nat. Nanotechnol.* 2014, 9, 268–272. [CrossRef]

- 28. Schultz, J.F.; Jiang, N. Characterizations of two-dimensional materials with cryogenic ultrahigh vacuum near-field optical microscopy in the visible range. *J. Vac. Sci. Technol.* **2022**, *40*, 040801. [CrossRef]

- Abbas, M.A.; Kim, J.; Rana, A.S.; Kim, I.; Rehman, B.; Ahmad, Z.; Massoud, Y.; Seong, J.; Badloe, T.; Park, K.; et al. Nanostructured Chromium-based Broadband Absorber and Emitter to Realize Thermally Stable Solar Thermophotovoltaic Systems. *Nanoscale* 2022, 14, 6425–6436. [CrossRef]

- 30. Hosseini, A.; Nieuwoudt, A.; Massoud, Y. Efficient simulation of subwavelength plasmonic waveguides using implicitly restarted Arnoldi. *Opt. Express* **2006**, *14*, 7291–7298. [CrossRef]

- Hosseini, A.; Nejati, H.; Massoud, Y. Design of a maximally flat optical low pass filter using plasmonic nanostrip waveguides. Opt. Express 2007, 15, 15280–15286. [CrossRef]

- 32. Gu, X.; Yang, R. Phonon transport and thermal conductivity in two-dimensional materials. *Annu. Rev. Heat Transf.* **2016**, *19*, 1. [CrossRef]

- Massoud, Y.; White, J. FastMag: A 3-D Fast Inductance Extraction Program for Structures with Permeable materials. In Proceedings of the IEEE/ACM International Conference on Computer Aided Design, San Jose, CA, USA, 10–14 November 2002; pp. 478–484.

- 34. Amir, H.; Massoud, Y. Optical range microcavities and filters using multiple dielectric layers in metal-insulator-metal structures. *J. Opt. Soc. Am. A* 2007, *24*, 221–224.

- 35. Massoud, Y.; Kawa, J.; MacMillen, D.; White, J. Modeling and Analysis of Differential Signaling for Minimizing Inductive Cross-Talk. In Proceedings of the IEEE/ACM Design Automation Conference, Las Vegas, NV, USA, 22 June 2001; pp. 804–809.

- 36. Hosseini, A.; Nejati, H.; Massoud, Y. Modeling and design methodology for metal-insulator-metal plasmonic Bragg reflectors. *Opt. Express* **2008**, *16*, 1475–1480. [CrossRef] [PubMed]

- Corro, E.; Terrones, H.; Elias, A.; Fantini, C.; Feng, S.; Nguyen, M.A.; Mallouk, T.E.; Terrones, M.; Pimenta, M.A. Excited excitonic states in 1L, 2L, 3L, and bulk WSe<sub>2</sub> observed by resonant Raman spectroscopy. ACS Nano 2014, 8, 9629–9635. [CrossRef] [PubMed]

- Sahin, H.; Tongay, S.; Horzum, S.; Fan, W.; Zhou, J.; Li, J.; Wu, J.; Peeters, F.M. Anomalous Raman spectra and thickness-dependent electronic properties of WSe. *Mater. Today* 2013, 87, 165409.

- Kim, K.; Larentis, S.; Fallahazad, B.; Lee, K.; Xue, J.; Dillen, D.C.; Corbet, C.M.; Tutuc, E. Band alignment in WSe<sub>2</sub>–graphene heterostructures. ACS Nano 2015, 9, 4527–4532. [CrossRef]

- Zhou, H.; Wang, C.; Shaw, J.C.; Cheng, R.; Chen, Y.; Huang, X.; Liu, Y.; Weiss, N.O.; Lin, Z.; Huang, Y.; et al. Large Area Growth and Electrical Properties of p-Type WSe<sub>2</sub> Atomic Layers. *Nano Lett.* **2015**, *15*, 709–713. [CrossRef]

- Namgung, S.D.; Yang, S.; Park, K.; Cho, A.-J.; Kim, H.; Kwon, J.-Y. Influence of post-annealing on the off current of MoS<sub>2</sub> field-effect transistors. *Nanoscale Res. Lett.* 2015, 10, 62. [CrossRef] [PubMed]

- Liu, Y.; Tan, C.; Chou, H.; Nayak, A.; Wu, D.; Ghosh, R.; Chang, H.-Y.; Hao, Y.; Wang, X.; Kim, J.-S.; et al. Thermal oxidation of WSe<sub>2</sub> nanosheets adhered on SiO2/Si substrates. *Nano Lett.* 2015, *15*, 4979–4984. [CrossRef]

- Wang, B.; Eichfield, S.M.; Wang, D.; Haque, M.A. In situ degradation studies of two-dimensional WSe<sub>2</sub>–graphene heterostructures. Nanoscale 2015, 7, 14489–14495. [CrossRef]

- Kang, M.; Yang, H.I.; Choi, W. Oxidation of WS2 and WSe<sub>2</sub> monolayers by ultraviolet-ozone treatment. *J. Phys. D Appl. Phys.* 2019, 52, 505105. [CrossRef]

- Tan, C.; Liu, Y.; Chou, H.; Kim, J.-S.; Wu, D.; Akinwande, D.; Lai, K. Laser-assisted oxidation of multi-layer tungsten diselenide nanosheets. *Appl. Phys. Lett.* 2016, 108, 083112. [CrossRef]

- Li, Z.; Yang, S.; Dhall, R.; Kosmowska, E.; Shi, H.; Chatzakis, I.; Cronin, S.B. Layer control of WSe<sub>2</sub> via selective surface layer oxidation. ACS Nano 2016, 10, 6836–6842. [CrossRef] [PubMed]

- Gammelgaard, L.; Whelan, P.R.; Booth, T.J.; Bøggild, P. Long-term stability and tree-ring oxidation of WSe 2 using phase-contrast AFM. *Nanoscale* 2021, 13, 19238–19246. [CrossRef] [PubMed]

- 48. Yamamoto, M.; Dutta, S.; Aikawa, S.; Nakaharai, S.; Wakabayashi, K.; Fuhrer, M.S.; Ueno, K.; Tsukagoshi, K. Self-limiting layer-by-layer oxidation of atomically thin WSe<sub>2</sub>. *Nano Lett.* **2015**, *15*, 2067–2073. [CrossRef] [PubMed]