Article

# Reconfigurable Sensor Analog Front-End Using Low-Noise Chopper-Stabilized Delta-Sigma Capacitance-to-Digital Converter

Hyungseup Kim <sup>1</sup>, Byeoncheol Lee <sup>1</sup>, Yeongjin Mun <sup>1</sup>, Jaesung Kim <sup>1</sup>, Kwonsang Han <sup>1</sup>, Youngtaek Roh <sup>2</sup>, Dongkyu Song <sup>2</sup>, Seounghoon Huh <sup>2</sup> and Hyoungho Ko <sup>1</sup>,\*

- Department of Electronics Engineering, Chungnam National University, Daejeon 34134, Korea; hyungseup@cnu.ac.kr (H.K.); dada5891@cnu.ac.kr (B.L.); ansdud159@cnu.ac.kr (Y.M.); jskim1@cnu.ac.kr (J.K.); kshan1@cnu.ac.kr (K.H.)

- <sup>2</sup> LeoLSI Co., Ltd., Seoul 06728, Korea; ytroh@leolsi.com (Y.R.); dksong@leolsi.com (D.S.); iamtoto@leolsi.com (S.H.)

- \* Correspondence: hhko@cnu.ac.kr; Tel.: +82-42-821-5664

Received: 15 May 2018; Accepted: 9 July 2018; Published: 10 July 2018

Abstract: This paper proposes a reconfigurable sensor analog front-end using low-noise chopper-stabilized delta-sigma capacitance-to-digital converter (CDC) for capacitive microsensors. The proposed reconfigurable sensor analog front-end can drive both capacitive microsensors and voltage signals by direct conversion without a front-end amplifier. The reconfigurable scheme of the front-end can be implemented in various multi-mode applications, where it is equipped with a fully integrated temperature sensor. A chopper stabilization technique is implemented here to achieve a low-noise characteristic by reducing unexpected low-frequency noises such as offsets and flicker noise. The prototype chip of the proposed sensor analog front-end is fabricated by a standard 0.18-µm 1-poly-6-metal (1P6M) complementary metal-oxide-semiconductor (CMOS) process. It occupies a total active area of 5.37 mm<sup>2</sup> and achieves an effective resolution of 16.3-bit. The total power consumption is 0.843 mW with a 1.8 V power supply.

**Keywords:** capacitive microsensor; analog front-end (AFE); capacitive sensor interface circuit; reconfigurable sensor readout circuit; delta-sigma modulation; capacitance-to-digital converter (CDC); temperature sensor; low-noise technique; chopper stabilization

#### 1. Introduction

The emergence of the Internet of Things (IoT) in recent years has greatly influenced the field of electronics, and the demand for the development of IoT based applications has increased. In particular, as the demand for various IoT applications grows, the performances of the sensor and the sensor interface integrated circuits have become increasingly important. Low-noise characteristics and low power consumption of the sensor interface circuits have become essential requirements. Capacitive microsensors are widely adopted in various applications such as humidity sensors, accelerometers, gyroscopes, biological sensors, pressure sensors, touch screen sensors, and proximity sensors [1–9]. With the wide use of capacitive microsensors, many research works on capacitive microsensor interface circuit techniques have been reported [10–22]. A multi-stage amplification capacitive sensor readout circuit with parasitic capacitance cancellation technique has been presented [10,11]. However, the multi-stage amplification scheme requires high power consumption and a large active area, which are not suitable for IoT applications that demand low power consumption and small size. A successive approximation register (SAR) capacitance-to-digital converter (CDC) scheme for

Micromachines 2018, 9, 347 2 of 16

low-power applications has been presented [12–16]. The SAR CDC scheme can achieve low power consumption and small size; however, it severely suffers from the effect of parasitic capacitance due to the direct connection of the capacitive sensor to the input of the comparator without the pre-amplifier. The implementation of the pre-amplifier in the SAR CDC scheme can relieve the effect of the parasitic capacitance, but the circuit complexity and power consumption increase. A delta-sigma modulation is widely used for high resolution capacitance-to-digital conversion. A capacitive sensor readout circuit with charge sensing amplifier (CSA) for pre-amplification of the sensor signal and a delta-sigma modulator can achieve high resolution because of its low-noise characteristic [17], however, the chip size and power consumption increase due to the additional CSA. To reduce the area and power consumption, the direct conversion delta-sigma CDC can be a good solution. The direct conversion first-order delta-sigma CDC scheme can relieve the problems by directly converting the capacitance change of the capacitive sensor to digital codes [18–21]. However, the first-order delta-sigma modulation scheme suffers from the dead zone problem, which increases the nonlinearity error and leads to performance degradation [22–25].

This paper presents a reconfigurable sensor analog front-end using low-noise chopper-stabilized delta-sigma CDC. The main strength of the proposed sensor analog front-end is the reconfigurable scheme, which can drive capacitive sensors and voltage signals without a front-end amplifier by direct conversion in the second-order incremental delta-sigma converter scheme. It also employs a chopper stabilization technique to achieve a low-noise characteristic. The second-order delta-sigma scheme can relieve the dead zone problem of the first-order delta-sigma modulation scheme, which causes nonlinearity error and performance degradation. The proposed sensor analog front-end with fully integrated temperature sensor can be flexibly adopted in various IoT sensor system applications due to its reconfigurable scheme.

This paper is organized as follows: Section 2 discusses the circuit implementation of the proposed reconfigurable sensor analog front-end. Section 3 describes the measurement results of the proposed reconfigurable sensor analog front-end. Finally, Section 4 presents the discussion of the proposed reconfigurable sensor analog front-end by comparison of performance with previously reported works and presents the conclusions of this work.

## 2. Circuit Implementation

#### 2.1. Top Level Architecture

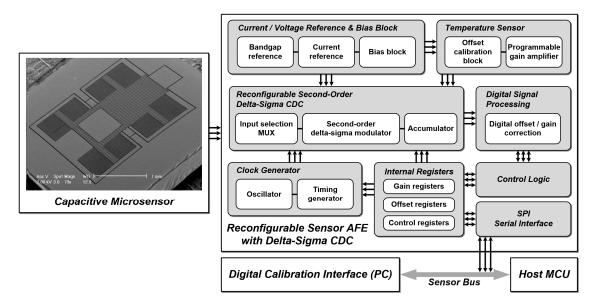

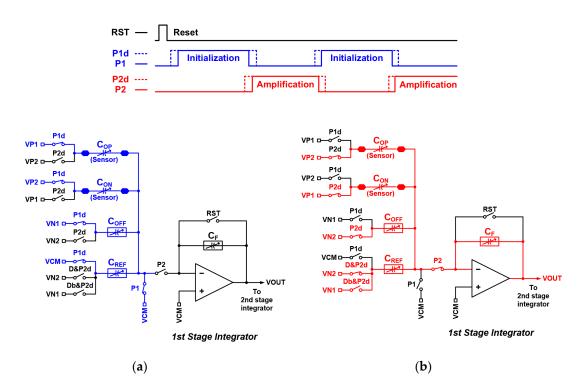

The block diagram of the proposed reconfigurable sensor analog front-end is shown in Figure 1. The analog front-end circuit includes: a second-order incremental delta-sigma CDC; a current/voltage reference block with the bandgap reference and bias block with a resister string; a clock generator with an on-chip oscillator and timing generator; a fully integrated temperature sensor; a digital offset/gain correction block; and a serial peripheral interface (SPI) for interface with the host microcontroller unit (MCU). The basic scheme of the reconfigurable sensor analog front-end comprises a second-order delta-sigma modulation scheme, which relieves the nonlinearity error and performance degradation caused by the dead zone that appears when the first-order delta-sigma modulation scheme is adopted. The reconfigurable sensor analog front-end can drive capacitive microsensors and voltage signals without a front-end amplifier by direct conversion. The proposed scheme can drive the capacitive microsensors in single drive mode or differential drive mode depending on the application. The bias generation block contains a bandgap reference, current reference and a bias block. The bandgap reference generates a reference voltage and the current reference generates the reference current with the bandgap voltage. The bias voltages generated in the bias block with the reference current supplies bias voltages for each sub-block. The bandgap reference also generates the complementary to the absolute temperature (CTAT) characteristic voltage for the operation of the fully integrated temperature sensor, which can be incorporated in specific applications to measure temperature when needed. The driving mode of the capacitive microsensors, the voltage signal driving mode, and the

Micromachines 2018, 9, 347 3 of 16

on-chip temperature sensor as the voltage signal driving mode, can be selected by register selection. The timing generator generates the clock signals needed by the on-chip oscillator, which can generate 1 MHz, 2 MHz, and 4 MHz master clocks by register selection or by the external input clock signal. The digital offset/gain correction block is integrated for offset/gain calibration. The SPI is used for register control and digital offset/gain correction block control with a laptop computer.

Figure 1. Block diagram of the proposed reconfigurable sensor analog front-end.

## 2.2. Reconfigurable Sensor Analog Front-End

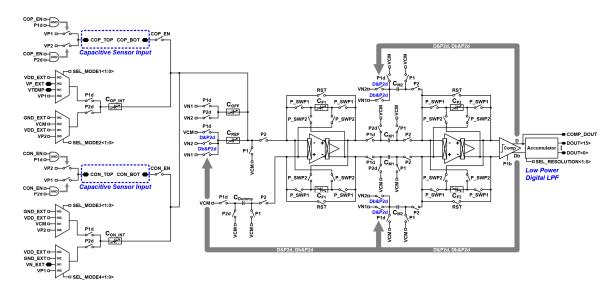

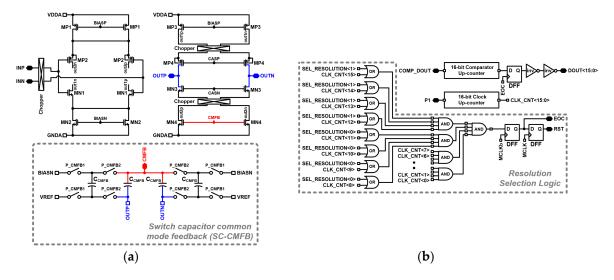

The schematic of the proposed reconfigurable second-order delta-sigma CDC is shown in Figure 2. The proposed reconfigurable sensor analog front-end is based on the second-order delta-sigma CDC scheme, which operates on the same concept as the conventional delta-sigma modulator based CDC. The switch-capacitor scheme serves to balance the signal charge of the input sensor capacitor ( $C_{OP}$  or  $C_{ON}$ ) with the programmable reference capacitor ( $C_{REF}$ ) using the feedback capacitor of the integrator  $(C_{F1})$  and  $C_{F2}$ , which balances the average charge to zero. The programmable offset capacitor  $(C_{OFF})$ is used for offset cancellation. The output signal through the two-stage integrator and comparator output is a digital signal, which is converted to 16-bit digital codes by the low-power digital low-pass filter (LPF) based on the accumulator. The digital data of the proposed scheme can also be acquired as bit-stream data (COMP\_DOUT) depending on the application preference. The programmable feedback capacitor of the first stage integrator ( $C_{F1}$ ) and second stage integrator ( $C_{F2}$ ) can be controlled from 0.177 pF to 22.671 pF by using a 7-bit control register, and from 0.177 pF to 11.336 pF by using a 6-bit control register. The timing diagram of the proposed reconfigurable sensor analog front-end is shown in Figure 3. The on-chip oscillator can generate 1 MHz, 2 MHz, or 4 MHz master clocks by register selection. Moreover, the external input clock can be operated manually. The default master clock (MCLK) operates at 1 MHz. P\_CMFB1 and P\_CMFB2 are non-overlapping clock signals used in the switch capacitor common mode feedback (SC-CMFB) for the fully differential amplifier, which operates at 500 kHz. P1, P1d, P2, and P2d are non-overlapping clocks operating at 250 kHz. The edges of P\_CMFB1, P\_CMFB2, P1, P1d, P2, and P2d do not overlap. The feedback capacitor swapping non-overlapping clocks of P\_SWP1 and P\_SWP2 operate at 125 kHz. The chopper non-overlapping clocks operate at 32 kHz. The reset clock (RST) operates at 1 kHz when implemented with the 1 MHz master clock. The proposed sensor analog front-end adopts a low-noise technique for ensuring a low-noise characteristic.

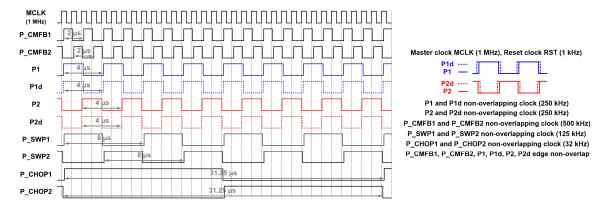

The detailed operation timing of the integrator in the delta-sigma CDC is shown in Figure 4 (i.e., the first stage integrator with differential capacitive sensor inputs  $C_{OP}$  and  $C_{ON}$ ). The operation is

Micromachines 2018, 9, 347 4 of 16

explained with a single-ended circuit scheme for simplicity. The RST is controlled by the accumulator in the back-end. The RST resets both of the first stage and second stage integrators after counting a number of 65,536 comparator output codes in the accumulator. The comparator output signal D and inverted signal Db are added to P2d with an AND gate controlling a VN1 switch and a VN2 switch connected to  $C_{REF}$ . After the reset phase, the CDC operates with two clock phases: An initialization phase and an amplification phase. The initialization phase is shown in Figure 4a. The non-overlapping clocks P1 and P1d enable the input sensors  $C_{OP}$ ,  $C_{ON}$  and  $C_{OFF}$  to be charged while  $C_{REF}$  is initialized to be reset by the reference voltage (VCM). The total charge can be expressed as Equation (1):

$$Q_{P1\&P1d} = C_{OP} \cdot (VCM - VP1) + C_{ON} \cdot (VCM - VP2) + C_{OFF} \cdot (VCM - VN1) \tag{1}$$

The amplification phase is shown in Figure 4b. The non-overlapping clocks P2 and P2d enable the charges stored in the input sensors  $C_{OP}$ ,  $C_{ON}$  and  $C_{OFF}$  to be transferred to the first stage integrator and to be amplified. The total charge in the amplification phase can be expressed as Equation (2):

$$Q_{P2\&P2d} = C_{OP} \cdot (VCM - VP2) + C_{ON} \cdot (VCM - VP1) + C_{OFF} \cdot (VCM - VN2) + D \cdot C_{REF} \cdot (VCM - VN2) + Db \cdot C_{REF} \cdot (VCM - VN1) + C_F \cdot (VCM - VOUT)$$

(2)

The total charge during the initialization phase and the amplification phase should be equal. The total charge transferred should satisfy Equation (3):

$$Q_{P1\&P1d} = Q_{P2\&P2d} \tag{3}$$

The voltages VP1, VP2, VN1 and VN2 are set according to Equation (4):

$$VP1 = VCM + 0.5 \cdot REFP$$

$$VP2 = VCM - 0.5 \cdot REFP$$

$$VN1 = VCM - 0.5 \cdot REFN$$

$$VN2 = VCM + 0.5 \cdot REFN$$

(4)

By Equations (3) and (4), the simplified output of the integrator can be expressed as Equation (5):

$$VOUT = (\frac{1}{C_F}) \cdot (C_{OP} \cdot REFP - C_{ON} \cdot REFP - C_{OFF} \cdot REFN - 0.5 \cdot D \cdot C_{REF} \cdot REFN + 0.5 \cdot Db \cdot C_{REF} \cdot REFN) + VCM$$

(5)

The output of the first stage integrator is then amplified by the second stage integrator by the same procedure. After the amplification of the second stage integrator, the comparator compares the second stage integrator and outputs bit-stream data.

The chopper stabilization technique is implemented to reduce low-frequency noises such as offsets and flicker noise [26]. The fully differential chopper amplifier is implemented as the amplifier of the integrator to obtain a low-noise characteristic. Similar fully differential chopper amplifiers are implemented for each stage. The schematic of the proposed fully differential chopper amplifier is shown in Figure 5a. The switched-capacitor common mode feedback (CMFB) circuit is implemented for low power consumption which generates the CMFB voltage for the fully differential chopper amplifier. The amplifier is designed with a DC gain of 78.68 dB and a 1.949 MHz unit gain bandwidth (UGBW). A feedback capacitor swapping scheme is adopted to enhance the common mode rejection ratio (CMRR) and thereby reduce the common mode noise of the sensor analog front-end. Figure 5b shows the resolution selectable accumulator. The accumulator consists of up-counters and resolution selection logic. The output digital code resolution can be selected by the accumulator by SEL\_RESOULTION<1:0> controlling the resolution selection logic. The resolution of the output digital code can be selected as 8-bit, 12-bit and 16-bit for specific application needs.

Micromachines 2018, 9, 347 5 of 16

The proposed sensor analog front-end can drive both capacitive microsensors and input voltage signals by register selection. The mode selection can be performed by controlling the registers SEL\_MODE1<1:0> to SEL\_MODE4<1:0> of the analog selection multiplexers, COP\_EN and CON\_EN. The driving mode of the single capacitive microsensors can be selected by enabling either COP\_EN or CON\_EN. The driving mode of the differential capacitive microsensors can be selected by enabling both COP\_EN and CON\_EN. When the driving mode of the capacitive microsensors is enabled, the internal programmable capacitors  $C_{OP\_INT}$  and  $C_{ON\_INT}$  should be switched off for correct conversion. The capacitive sensing mode operation can be expressed as Equation (6). The computations shown in Equation (6) can be denoted as REFP and REFN.

$$VP1 - VP2 = REFP$$

$$VN2 - VN1 = REFN$$

(6)

As shown in Equation (5), the differential output voltage of the second-order delta-sigma integrator of the proposed reconfigurable sensor analog front-end can be defined as Equation (7). The term  $C_F$  is the feedback capacitor of the second-order delta-sigma integrator.

$$\Delta V_O = (\frac{1}{C_F}) \cdot (C_{OP} \cdot REFP - C_{ON} \cdot REFP - C_{OFF} \cdot REFN - 0.5 \cdot D \cdot C_{REF} \cdot REFN + 0.5 \cdot Db \cdot C_{REF} \cdot REFN)$$

$$(7)$$

The input capacitance range can be defined by each conditions. When the differential output voltage of the second-order delta-sigma integrator is higher than 0 V and the bit-stream data D[n] is Low (0), it is saturated and the minimum input range can be expressed as Equation (8):

$$\Delta V_O > 0 \& D[n] = 0 \quad \text{(Minimum input capacitance range)}$$

$$(C_{OFF} - 0.5 \cdot C_{REF}) \cdot REFN < (C_{OP} - C_{ON}) \cdot REFP$$

(8)

When the differential output voltage of the second-order delta-sigma integrator is lower than 0 V and the bit-stream data D[n] is High (1), it is saturated and the maximum input range can be expressed as Equation (9):

$$\Delta V_O < 0 \& D[n] = 1 \quad \text{(Maximum input capacitance range)}$$

$$(C_{OP} - C_{ON}) \cdot REFP < (C_{OFF} + 0.5 \cdot C_{REF}) \cdot REFN$$

(9)

The capacitive input range of the driving mode of the capacitive microsensors can be defined as Equation (10):

$$(C_{OFF} - 0.5 \cdot C_{REF}) \cdot \frac{REFN}{REFP} < (C_{OP} - C_{ON}) < (C_{OFF} + 0.5 \cdot C_{REF}) \cdot \frac{REFN}{REFP}$$

(10)

The programmable capacitors  $C_{REF}$  and  $C_{OFF}$  can each be controlled from 0.177 pF to 11.158 pF by a 6-bit control register; their on and off states can also be controlled. The maximum capacitive input range of the proposed reconfigurable sensor analog front-end is 16.738 pF.

The voltage signal driving mode can be enabled by disabling COP\_EN and CON\_EN for the driving mode of the capacitive microsensors. When the voltage signal driving mode is enabled, the internal programmable capacitor  $C_{OP\_INT}$  or  $C_{ON\_INT}$  of the sampling capacitor should be switched on. A single-ended voltage mode can be selected by switching on one of the internal programmable capacitors  $C_{OP\_INT}$  and  $C_{ON\_INT}$ . When the internal programmable capacitor  $C_{OP\_INT}$  is selected as the single-input sampling capacitor, the input signal VP\_EXT should be selected by controlling SEL\_MODE1<1:0>. Further, when the internal programmable capacitor  $C_{ON\_INT}$  is selected as the single-input sampling capacitor, the input signal VN\_EXT should be selected by controlling SEL\_MODE4<1:0>. A differential voltage mode can be selected by switching on both the internal programmable capacitors  $C_{OP\_INT}$  and  $C_{ON\_INT}$ . When the differential input mode is selected,

Micromachines 2018, 9, 347 6 of 16

the internal programmable capacitors  $C_{OP\_INT}$  and  $C_{ON\_INT}$  should be switched on as differential sampling capacitors for both inputs. In addition, both the input signals VP\_EXT and VN\_EXT should be selected by controlling the SEL\_MODE1<1:0> and SEL\_MODE4<1:0> registers. The switching voltage can be controlled by SEL\_MODE2<1:0> and SEL\_MODE3<1:0>. The voltage signal driving mode with the single-ended voltage mode with VP\_EXT input can be expressed as Equation (11) when the condition is as specified in the equation:

$$VP1 - VP2 = REFP, VP1 = V_{IN}$$

$$\tag{11}$$

From Equations (10) and (11), the input range of the single-ended voltage mode can be deduced as Equation (12):

$$\left(\frac{C_{OFF} - 0.5 \cdot C_{REF}}{C_{OP\_INT}}\right) \cdot REFN + VP2 < V_{IN} < \left(\frac{C_{OFF} + 0.5 \cdot C_{REF}}{C_{OP\_INT}}\right) \cdot REFN + VP2$$

$$VP1 = VP\_EXT$$

(12)

The single-ended voltage mode with VN\_EXT input can be expressed as for Equation (12) by changing the parameters  $C_{OP\_INT}$  to  $C_{ON\_INT}$ , and VP\_EXT to VN\_EXT. Each of the programmable capacitors  $C_{REF}$ ,  $C_{OFF}$ ,  $C_{OP\_INT}$ , and  $C_{ON\_INT}$  can be controlled from 0.177 pF to 11.158 pF by a 6-bit control register, and their on and off states can also be controlled. The maximum voltage mode input range of the proposed reconfigurable sensor analog front-end is 0 V to 1.8 V.

Figure 2. Schematic of the second-order delta-sigma CDC.

Figure 3. Timing diagram of the second-order delta-sigma CDC.

*Micromachines* **2018**, 9, 347 7 of 16

**Figure 4.** Detailed operation timing of the integrator in the delta-sigma CDC. (a) Initialization phase; (b) Amplification phase.

**Figure 5.** Schematic of fully differential chopper amplifier and accumulator. (a) Fully differential chopper amplifier; (b) Resolution selectable accumulator.

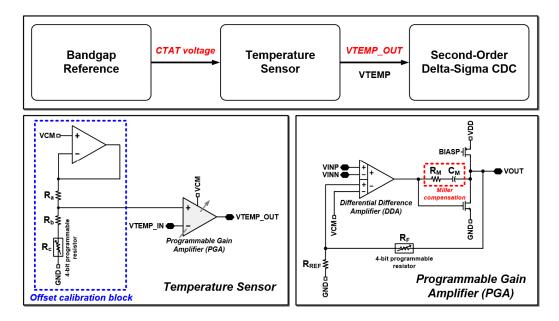

# 2.3. Fully Integrated Temperature Sensor

The schematic of the fully integrated temperature sensor of the proposed reconfigurable sensor analog front-end is shown in Figure 6. The temperature sensor operates and senses the temperature with the CTAT voltage generated by the bandgap reference. The output analog voltage of the temperature sensor is converted to digital codes by the voltage input mode of the proposed scheme. The scheme of the temperature sensor has been presented in [27]. The temperature sensor consists of an offset calibration block and the programmable gain amplifier (PGA). The programmable resistor ( $R_c$ ) of the offset calibration block can be controlled from 52.267 k $\Omega$  to 784.016 k $\Omega$ . The value of resistor

Micromachines 2018, 9, 347 8 of 16

$R_a$  is 250.885  $k\Omega$  and that of  $R_b$  is 385.875  $k\Omega$ . The offset voltage of the temperature sensor can be expressed as Equation (13):

$V_{OFFSET} = \left(\frac{R_b + R_c}{R_a + R_b + R_c}\right) \cdot VCM \tag{13}$

The PGA is implemented using a differential difference amplifier (DDA). The gain of the PGA is controlled by the 4-bit programmable resistor  $R_F$  from 522.678 k $\Omega$  to 7.840 M $\Omega$ . The gain of the PGA can be expressed as Equation (14):

$$VOUT = \left(1 + \frac{R_F}{R_{RFF}}\right) \cdot \left(VINP - VINN\right) + VCM \tag{14}$$

Therefore, the output voltage of the temperature sensor can be expressed as Equation (15).

$$VTEMP\_OUT = \left(1 + \frac{R_F}{R_{REF}}\right) \cdot \left(V_{OFFSET} - VTEMP\_IN\right) + VCM \tag{15}$$

The gain for temperature signal amplification and the offset level can be controlled by the proposed scheme depending on the application status in the temperature range of -10 °C to 120 °C.

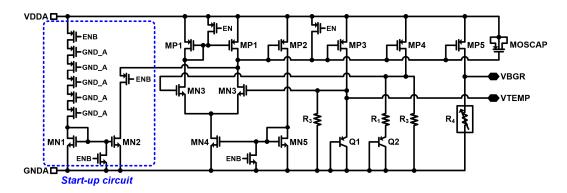

The schematic of the bandgap reference of the fully integrated temperature sensor is shown in Figure 7. The implemented low voltage bandgap reference in the temperature sensor is a modified version of the previous bandgap scheme [28]. The bandgap reference operates with the input enable signal (EN) to be High (1) (input disable signal (ENB) to be Low (0)) which operates the start-up circuit. The output bandgap reference voltage (VBGR) is generated by ratios of the resistors  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$ , following Equation (16) (when the ratio between the two bipolar junction transistors (BJT) is Q1:Q2 = 1:24):

$$VBGR = (\frac{R_4}{R_1}) \cdot V_T \cdot ln(n) + (\frac{R_4}{R_3}) \cdot VEB_{Q2}$$

$$ln(24) = 3.178$$

(16)

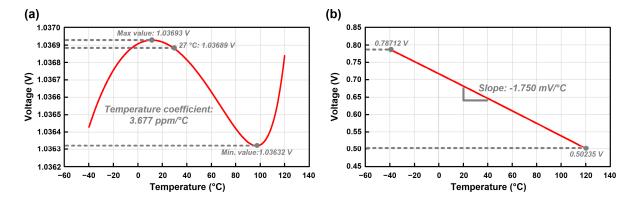

The bandgap resistor R4 is implemented with a 3-bit programmable resistor for voltage trimming with a range of 90.986 k $\Omega$  to 126.280 k $\Omega$ . Figure 8 shows the simulation results of the bandgap reference. The simulation result of the temperature sweep in the range of  $-40\,^{\circ}\text{C}$  to 120  $^{\circ}\text{C}$  is shown in Figure 8a. The simulated temperature coefficient is 3.677 ppm/ $^{\circ}\text{C}$ . The generated temperature sensor voltage (VTEMP) with CTAT voltage characteristic is shown in Figure 8b. The simulation result shows that the VTEMP has CTAT characteristic with  $-1.750\,\text{mV}/^{\circ}\text{C}$ , which is used in the proposed on-chip temperature sensor shown as in Equation (15).

Micromachines 2018, 9, 347 9 of 16

Figure 6. Schematic of fully integrated temperature sensor.

Figure 7. Schematic of bandgap reference of the fully integrated temperature sensor.

**Figure 8.** Simulation results of the bandgap reference. (a) Temperature sweep of output bandgap reference voltage (VBGR); (b) Generated temperature sensor voltage (VTEMP).

#### 3. Measurement Results

## 3.1. Prototype Chip Implementation

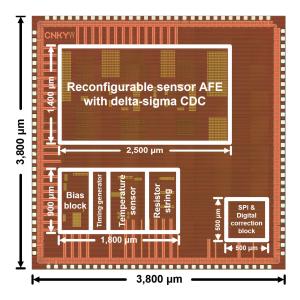

The reconfigurable sensor analog front-end integrated circuit (IC) was fabricated using a standard 0.18-μm complementary metal-oxide-semiconductor (CMOS) process with an active area of 5.37 mm<sup>2</sup>.

Micromachines 2018, 9, 347 10 of 16

The die photograph is shown in Figure 9. The chip is fully integrated without other external elements. The total power consumption is 0.843 mW with 1.8 V power supply.

Figure 9. Die photograph of the proposed reconfigurable sensor analog front-end IC.

#### 3.2. Measurement Environment

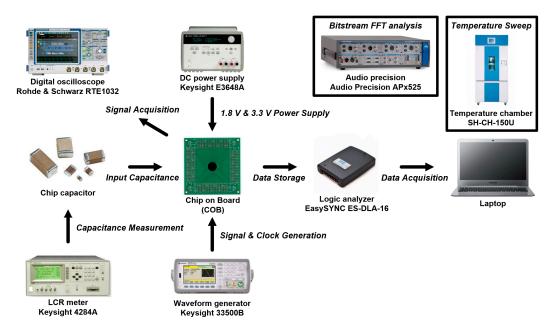

The measurement environment of the reconfigurable sensor analog front-end IC is shown in Figure 10. A digital oscilloscope was used for signal acquisition and data analysis. The output digital codes of the prototype IC are acquired by the logic analyzer through the laptop computer. The Fast Fourier Transform (FFT) measurement with output bit-stream data was performed by using the Audio Precision APx525. The inductance, capacitance and resistance (LCR) meter was used to measure the chip capacitor to compare with the measurement results by the proposed prototype IC for measurement evaluation. The temperature chamber was used to evaluate the performance of the on-chip temperature sensor.

Figure 10. Measurement environment of the proposed reconfigurable sensor analog front-end IC.

Micromachines 2018, 9, 347 11 of 16

#### 3.3. Measurement Results

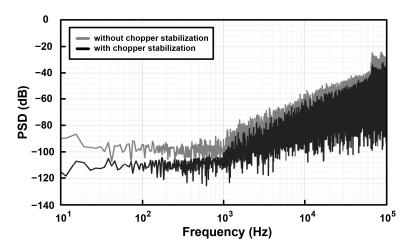

The FFT measurement results of the driving mode of the capacitive microsensors in the proposed reconfigurable sensor analog front-end IC are shown in Figure 11. The FFT was achieved by the bit-stream data FFT length of 65,536 points with a Blackman–Harris 3-term window. The gray line shows the measurement results without the application of the chopper stabilization technique and the black line shows the measurement results with the application of the chopper stabilization technique. The FFT result shows enhanced reduction of noise by the chopper stabilization technique implemented in the proposed scheme.

Figure 11. FFT measurement results of the proposed reconfigurable sensor analog front-end IC.

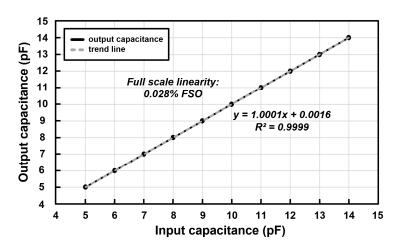

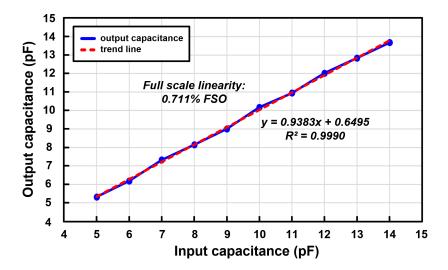

The simulation result of the capacitance linearity is shown in Figure 12. The output capacitance is indicated by the black line and the gray line indicates the trend line of the simulated output capacitance. The simulated nonlinearity is 0.028% FSO. The simulation was proceeded by Cadence Virtuoso for comparison with the measurement result. The capacitance linearity measurement result of the driving mode of the capacitive microsensors in the proposed scheme is shown in Figure 13. The capacitance linearity was measured by changing the input capacitance and acquiring the output digital codes. The output capacitance is indicated by the blue line and the red line indicates the trend line of the measured output capacitance. The measured nonlinearity is 0.711% FSO. The input capacitance was connected and measured using the LCR meter, and then connected to the analog front-end circuit; thus, the measurement results include the relatively large non-linearity because of the parasitic capacitance from the measurement environment.

Figure 12. Linearity simulation results of the proposed reconfigurable sensor analog front-end.

Micromachines 2018, 9, 347 12 of 16

Figure 13. Linearity measurement results of the proposed reconfigurable sensor analog front-end.

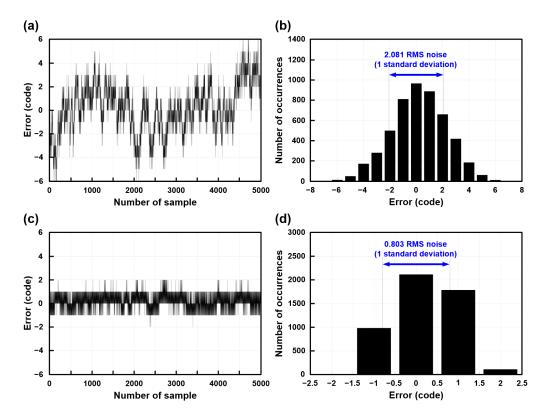

The measured output codes of the capacitive microsensors of the proposed scheme are shown in Figure 14a–d. The output code error without chopper stabilization is shown in Figure 14a and its histogram is shown in Figure 14b. The output code error with the application of the chopper stabilization is shown in Figure 14c and its histogram is shown in Figure 14d. Five thousand sets of data values with fixed input capacitance of 6 pF were acquired. Figure 14a shows the peak-to-peak (P-P) noise of  $\pm 6$  code variation without the application of the chopper stabilization. Figure 14c shows the measurement results of the code variation with the application of the chopper stabilization, which improved the code variation to  $\pm 2$ . The root mean square (RMS) noise is improved from 2.081 to 0.803, as shown in Figures 14b and 14d. The measured input referred capacitance RMS noise is 0.180 fF without the application of the chopper stabilization and 0.069 fF with the application of the chopper stabilization. The RMS noise and P-P noise can be acquired by the standard deviation and difference of the maximum and minimum results of the data. The effective resolution and P-P resolution can be acquired for performance evaluation. The effective resolution can be calculated as Equation (17) and the P-P resolution can be calculated as Equation (18) from the histogram results [29]:

$$Effective \ resolution = \log_2(\frac{P - P \ Range \ (LSBs)}{RMS \ Noise \ (LSBs)})$$

(17)

$$P - P \ resolution = \log_2(\frac{P - P \ Range \ (LSBs)}{P - P \ Noise \ (LSBs)})$$

(18)

The measured effective resolution and *P-P resolution* of the proposed scheme without the application of the chopper stabilization are 14.9-bit and 12.4-bit, respectively. The measured effective resolution and *P-P resolution* with the application of the chopper stabilization are 16.3-bit and 14-bit, respectively.

Micromachines 2018, 9, 347 13 of 16

**Figure 14.** Measured output codes of the proposed reconfigurable sensor analog front-end IC. (a) Output code error without chopper stabilization; (b) Histogram of output code error without chopper stabilization; (c) Output code error with chopper stabilization; (d) Histogram of output code error with chopper stabilization.

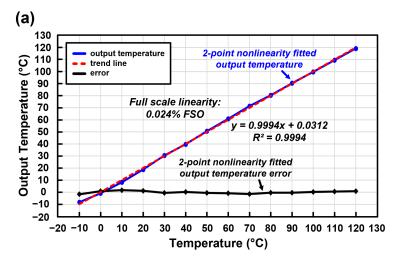

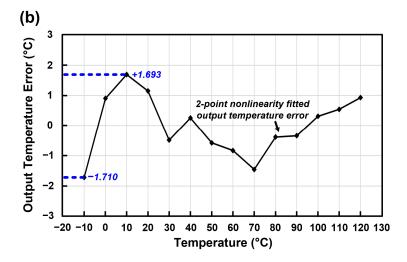

The measured output data of the temperature sensor with the proposed reconfigurable sensor analog front-end IC are shown in Figures 15a and 15b. The measured temperature range is  $-10\,^{\circ}\text{C}$  to 120  $^{\circ}\text{C}$ . Figure 15a shows the measured output temperature data. The blue line represents the output temperature with two-point nonlinearity fitting. The red line is the trend line of the measured output temperature and the black line represents the error of the two-point nonlinearity fitted output temperature, which is shown in detail in Figure 15b. The measured nonlinearity is 0.024% FSO and the output temperature error is  $-1.710/+1.693\,^{\circ}\text{C}$ .

Figure 15. Cont.

Micromachines 2018, 9, 347 14 of 16

**Figure 15.** Measured output data of the temperature sensor of the proposed sensor analog front-end. (a) Measured output temperature data; (b) Error of the two-point nonlinearity fitted output temperature.

#### 4. Discussion and Conclusions

The performance summary and comparison of previous works with the proposed reconfigurable sensor analog front-end scheme is shown in Table 1. The figure-of-merit (*FoM*) for the performance comparison can be calculated as given in Equation (19) [30]:

$$FoM = \frac{P_{total} \cdot T_{measurement}}{2^{resolution}} \tag{19}$$

The performance summary and comparisons show that the proposed work achieves high effective resolution, low power consumption, and low *FoM*. The power consumption of 0.843 mW and *FoM* of 13.06 pJ/step show improvements compared with previous works with similar architecture of discrete time delta-sigma CDC. The wide range of input capacitance with 16.7 pF of the proposed CDC is also an advantage compared to previous works, which makes it suitable for various capacitive microsensor applications.

This paper presented a reconfigurable sensor analog front-end using low-noise chopper-stabilized delta-sigma CDC. The proposed scheme can drive both capacitive microsensors and voltage signals by direct conversion. A fully integrated temperature sensor is implemented in the proposed reconfigurable sensor analog front-end for various applications. A low-noise technique with chopper stabilization was implemented to achieve a low-noise characteristic. The prototype IC was fabricated as per the standard 0.18-µm 1P6M CMOS process. The proposed scheme occupies a total active area of 5.37 mm² and the total power consumption is 0.843 mW with a 1.8 V power supply. It achieves an effective resolution of 16.3-bit and measured input referred capacitance RMS noise of 0.069 fF. The measured capacitance nonlinearity and the measured temperature nonlinearity are 0.711 % FSO and 0.024% FSO, respectively. The proposed sensor analog front-end can be flexibly adopted in various IoT sensor system applications with reasonable performance due to its reconfigurable scheme.

Micromachines 2018, 9, 347 15 of 16

| Specification                  | This Work                 | [20]   | [31]   | [32]   | [33]   | [34]   |

|--------------------------------|---------------------------|--------|--------|--------|--------|--------|

| Modulator order                | DT 2nd                    | DT 1st | DT 2nd | DT 2nd | DT 4th | DT 2nd |

| Process (μm)                   | 0.18                      | 0.35   | 0.35   | -      | 0.25   | 0.18   |

| Re-configurability             | Y                         | N      | N      | N      | N      | N      |

| Supply voltage (V)             | 1.8 (core)/<br>3.3 (pads) | 3.3    | 3.0    | 5.0    | 2.5    | 2.6    |

| Power consumption (mW)         | 0.843                     | 1.44   | 60     | 3.75   | 6      | 2.34   |

| Measurement time (ms)          | 1.25                      | 0.128  | 1000   | 20     | 500    | 3.07   |

| Effective Resolution (bit)     | 16.3                      | 11.0   | 20.0   | 19.4   | 20.3   | 17.4   |

| Capacitance range (pF)         | 16.7                      | 1      | 1      | 8      | 5.3    | 10     |

| FoM (pJ/step)                  | 13.06                     | 90     | 57220  | 108    | 2300   | 37     |

| Active area (mm <sup>2</sup> ) | 5.37                      | 0.05   | 0.65   | -      | 2      | 0.67   |

**Table 1.** Performance summary and comparisons.

**Author Contributions:** H.K. conceived the study; H.K., B.L., Y.R., D.S., and S.H. designed the experiment; all authors participated in the testing and evaluations; H.K. wrote the paper.

Funding: This research received no external funding.

Acknowledgments: This work was supported by LeoLSI Co., Ltd., and IC Design Education Center (IDEC).

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Rittersma, Z.M. Recent achievements in miniaturised humidity sensors—A review of transduction techniques. *Sens. Actuators A Phys.* **2002**, *96*, 196–210. [CrossRef]

- 2. Sun, H.; Fang, D.; Jia, K.; Maarouf, F.; Qu, H.; Xie, H. A low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. *IEEE Sens. J.* **2011**, *11*, 925–933. [CrossRef]

- 3. Tez, S.; Akin, T. Fabrication of a sandwich type three axis capacitive MEMS accelerometer. In Proceedings of the IEEE Sensors, Baltimore, MD, USA, 3–6 November 2013; pp. 1–4.

- 4. Cho, D.; Ko, H.; Kim, J.; Park, S.; Kwak, D.; Song, T.; Carr, W.; Buss, J. A novel z-axis accelerometer with perfectly-aligned, fully-offset vertical combs fabricated using the extended sacrificial bulk micromachining process. *Int. J. Comput. Eng. Sci.* **2003**, *4*, 493–496. [CrossRef]

- 5. Tsouti, V.; Boutopoulos, C.; Zergioti, I.; Chatzandroulis, S. Capacitive microsystems for biological sensing. *Biosens. Bioelectron.* **2011**, 27, 1–11. [CrossRef] [PubMed]

- 6. Yu, H.Y.; Qin, M.; Huang, J.Q.; Huang, Q.A. A MEMS capacitive pressure sensor compatible with CMOS process. In Proceedings of the IEEE Sensors, Taipei, Taiwan, 28–31 October 2012; pp. 1–4.

- 7. Pedersen, T.; Fragiacomo, G.; Hansen, O.; Thomsen, E.V. Highly sensitive micro-machined capacitive pressure sensor with reduced hysteresis and low parasitic capacitance. *Sens. Actuators A Phys.* **2009**, *154*, 35–41. [CrossRef]

- 8. Tan, Z.; Shalmany, S.H.; Meijer, G.C.; Pertijs, M.A. An energy-efficient 15-bit capacitive-sensor interface based on period modulation. *IEEE J. Solid State Circuits* **2012**, *47*, 1703–1711. [CrossRef]

- 9. Dobrzynska, J.A.; Gijs, M.A.M. Polymer-based flexible capacitive sensor for three-axial force measurements. *J. Micromech. Microeng.* **2013**, 23, 1–11. [CrossRef]

- 10. Song, H.; Park, Y.; Kim, H.; Cho, D.D.; Ko, H. Fully integrated low-noise readout circuit with automatic offset cancellation loop for capacitive microsensors. *Sensors* **2015**, *15*, 26009–26017. [CrossRef] [PubMed]

- 11. Mun, Y.; Kim, H.; Ko, Y.; Park, Y.; Koo, K.; Cho, D.D.; Ko, H. Capacitive analog front-end circuit with dual-mode automatic parasitic cancellation loop. *Microsyst. Technol.* **2017**, *23*, 515–523. [CrossRef]

- 12. Tanaka, K.; Kuramochi, Y.; Kurashina, T.; Okada, K.; Matsuzawa, A. A 0.026 mm<sup>2</sup> capacitance-to-digital converter for biotelemetry applications using a charge redistribution technique. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Jeju, Korea, 12–14 November 2007; pp. 244–247.

- 13. Omran, H.; Arsalan, M.; Salama, K.N. An integrated energy-efficient capacitive sensor digital interface circuit. *Sens. Actuators A Phys.* **2014**, 216, 43–51. [CrossRef]

Micromachines 2018, 9, 347 16 of 16

14. Alhoshany, A.; Omran, H.; Salama, K.N. A 45.8 fJ/Step, energy-efficient, differential SAR capacitance-to-digital converter for capacitive pressure sensing. *Sens. Actuators A Phys.* **2016**, 245, 10–18. [CrossRef]

- 15. Omran, H.; Alhoshany, A.; Alahmadi, H.; Salama, K.N. A 33fJ/Step SAR capacitance-to-digital converter using a chain of inverter-based amplifiers. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2017**, *64*, 310–321. [CrossRef]

- Alhoshany, A.; Sivashankar, S.; Mashraei, Y.; Omran, H.; Salama, K.N. A biosensor-CMOS platform and integrated readout circuit in 0.18-μm CMOS technology for cancer biomarker detection. Sensors 2017, 17, 1942. [CrossRef] [PubMed]

- 17. Xu, H.; Liu, X.; Yin, L. A closed-loop  $\Sigma\Delta$  interface for a high-Q micromechanical capacitive accelerometer with 200 ng/ Hz input noise density. *IEEE J. Solid State Circuits* **2015**, *50*, 2101–2112. [CrossRef]

- 18. Liu, B.; Hoseini, Z.; Lee, K.S.; Lee, Y.M. On-chip touch sensor readout circuit using passive sigma-delta modulator capacitance-to-digital converter. *IEEE Sens. J.* **2015**, *15*, 3893–3902. [CrossRef]

- 19. Chiou, J.C.; Hsu, S.H.; Huang, Y.C.; Yeh, G.T.; Liou, W.T.; Kuei, C.K. A wirelessly powered smart contact lens with reconfigurable wide range and tunable sensitivity sensor readout circuitry. *Sensors* **2017**, *17*, 108. [CrossRef] [PubMed]

- 20. Shin, D.Y.; Lee, H.; Kim, S. A delta–sigma interface circuit for capacitive sensors with an automatically calibrated zero point. *IEEE Trans. Circuits Syst. II Exp. Briefs* **2011**, *58*, 90–94. [CrossRef]

- 21. Oh, S.; Jung, W.; Yang, K.; Blaauw, D.; Sylvester, D. 15.4b incremental sigma-delta capacitance-to-digital converter with zoom-in 9b asynchronous SAR. In Proceedings of the Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014; pp. 1–2.

- 22. Robert, J.; Deval, P. A second-order high-resolution incremental A/D converter with offset and charge injection compensation. *IEEE J. Solid State Circuits* **1988**, 23, 736–741. [CrossRef]

- 23. Boser, B.E.; Howe, R.T. Surface micromachined accelerometers. *IEEE J. Solid State Circuits* **1996**, *31*, 366–375. [CrossRef]

- 24. Markus, J.; Silva, J.; Temes, G.C. Theory and applications of incremental ΔΣ converters. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2004**, *51*, 678–690. [CrossRef]

- 25. Dong, Y.; Kraft, M.; Gollasch, C.; Redman-White, W. A high-performance accelerometer with a fifth-order sigma–delta modulator. *J. Micromech. Microeng.* **2005**, *15*, S22–S29. [CrossRef]

- 26. Enz, C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. *Proc. IEEE* **1996**, *84*, 1584–1614. [CrossRef]

- 27. Park, Y.; Kim, H.; Ko, Y.; Mun, Y.; Lee, S.; Kim, J.H.; Ko, H. Low noise CMOS temperature sensor with on-chip digital calibration. *Sensor Mater.* **2017**, 29, 1025–1030.

- 28. Banba, H.; Shiga, H.; Umezawa, A.; Miyaba, T.; Tanzawa, T.; Atsumi, S.; Sakui, K. A CMOS bandgap reference circuit with sub-1-V operation. *IEEE J. Solid State Circuits* **1999**, *34*, *670*–*674*. [CrossRef]

- Understanding Noise, ENOB, and Effective Resolution in Analog-to-Digital Converters, Maxim Integrated, Appl. Note. AN5384. Available online: <a href="http://www.maximintegrated.com">http://www.maximintegrated.com</a> (accessed on 10 July 2018).

- 30. Li, B.; Sun, L.; Ko, C.T.; Wong, A.K.Y.; Pun, K.P. A high-linearity capacitance-to-digital converter suppressing charge errors from bottom-plate switches. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2014**, *61*, 1928–1941. [CrossRef]

- 31. Gozzini, F.; Ferrari, G.; Sampietro, M. An instrument-on-chip for impedance measurements on nanobiosensors with attoFarad resoution. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 346–348.

- 32. 24-Bit Capacitance-to-Digital Converter with Temperature Sensor, Analog Devices, Data Sheet AD7745/AD7746. Available online: http://www.analog.com (accessed on 10 July 2018).

- 33. Amini, B.V.; Ayazi, F. A 2.5-V 14-bit ΣΔ CMOS SOI capacitive accelerometer. *IEEE J. Solid State Circuits* **2004**, 39, 2467–2476. [CrossRef]

- 34. Jung, Y.; Duan, Q.; Roh, J. A 17.4-b delta-sigma capacitance-to-digital converter for one-terminal capacitive sensors. *IEEE Trans. Circuits Syst. II Exp. Briefs* **2017**, *64*, 1122–1126. [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).