Review

# 3D Integrated Circuit Cooling with Microfluidics

Shaoxi Wang <sup>1,2,3,\*</sup> , Yue Yin <sup>1</sup>, Chenxia Hu <sup>4</sup> and Pouya Rezai <sup>2</sup>

- School of software and microelectronics, Northwestern Polytechnical University, Xi'an 710072, China; yinyue@nwpu.edu.cn

- Lassonde School of Engineering, York University, Toronto, ON M3J 1P3, Canada; pouya.rezai@lassonde.yorku.ca

- Research & Development Institute of Northwestern Polytechnical University, Shenzhen 518057, China

- School of Pharmaceutical Science, Guangzhou University of Chinese Medicine, Guangzhou 510006, China; 20010614@gzucm.edu.cn

- \* Correspondence: shxwang@nwpu.edu.cn

Received: 27 April 2018; Accepted: 1 June 2018; Published: 7 June 2018

Abstract: Using microfluidic cooling to achieve thermal management of three-dimensional integrated circuits (ICs) is recognized as a promising method of extending Moore law progression in electronic components and systems. Since the U.S. Defense Advanced Research Projects Agency launched Intra/Inter Chip Enhanced Cooling thermal packaging program, the method of using microfluidic cooling in 3D ICs has been under continuous development. This paper presents an analysis of all publications available about the microfluidic cooling technologies used in 3D IC thermal management, and summarized these research works into six categories: cooling structure design, co-design issues, through silicon via (TSV) influence, specific chip applications, thermal models, and non-uniform heating and hotspots. The details of these research works are given, future works are suggested.

**Keywords:** microfluidics; 3D; integrated circuits; cooling

#### 1. Introduction

With the feature size of integrated circuits (ICs) scaling down towards the extreme of traditional micro/nano fabrication, the 3D IC technique is a promising method of extending the Moore law [1]. Three-dimensional ICs can alleviate the interconnection bottleneck that currently exists at the nanometer scale and continue the law's progression. This next-generation technology is promising for multiple cores, memory, and logic units that are stacked vertically and interconnected in a single unit to increase clocking speed, reducing transmission losses, power consumption, and footprint area [2].

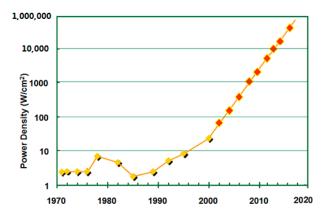

However, 3D ICs also present many serious challenges that need to be overcome to make the technology useful. The greatest challenge is overheating because of an increasing power flux and a higher thermal resistance. This 3D IC technology may lead to the alienation of stacked-structure hotspots and the increase of local heat fluxes, and global chip temperature, hence degrading chip performance and reliability. The reliability, performance, and power dissipation of interconnects and transistors are heavily dependent on the operating temperature. Therefore, chip-level cooling with large power dissipation in high performance chips has become imperative. International Technology Roadmap for Semiconductors (ITRS) projects that the power density of a single package will increase to  $10^6 \text{ W/cm}^2$  for performance applications in 2018 [3]. Such a trend is shown in Figure 1. Power density is increased greatly as more chips are integrated into a package.

Consequently, effective cooling structures used in 3D IC technologies need to be developed in order to benefit beyond the Moore law [4]. A number of chip cooling methods, which include passive and active cooling methods, have been proposed. Passive methods include thermal conduction (pastes, metal lines, and vias), natural convection (finned heat sinks and ventilation slots), radiation (coatings

Micromachines 2018, 9, 287 2 of 14

and paints), heat pipes, and thermosyphons [5]. These passive devices are easily designed and generally inexpensive to implement, but typically perform worse than active-cooling devices. Active cooling requires input power, which requires external components such as forced convection devices (fans and nozzles), pumped loops (heat exchangers and cold plates), and refrigerators (Peltier thermoelectric and vapor-compression-based) [5]. However, these cooling methods cannot be embedded in 3D IC structures with a small enough size or effective cooling, and are still unable to address the varying thermal profiles of an IC.

**Figure 1.** The power density trend for a single package.

Microfluidics, also called lab-on-a-chip, is the science and technology of systems that process or manipulate small amounts of fluids, using channels or flat platforms with dimensions of tens to hundreds of micrometers [6]. In 2004, American Business 2.0 magazine named microfluidics as one of the seven new technologies that change everything, stating that such innovations were already here and were about to hatch some of tomorrow's greatest business opportunities [7]. In July 2006, Nature magazine published a special issue for microfluidics, presenting the origins, the future, and the basic principle and applications of microfluidics, and recognized it as "the technologies of the century" [8]. Moreover, most research works focus on applications in biology, chemistry, materials science, and medical science.

More recently, microfluidics cooling has been demonstrated as promising for 3D ICs with high power density. Since 2012, the U.S. Defense Advanced Research Projects Agency (DARPA) has worked on an Intra/Inter Chip Enhanced Cooling (ICECool) thermal packaging program to solve cooling limitations and remove significant barriers so as to continue Moore law progression in electronic components and systems. The program adopts microfluidic cooling as aggressive thermal management techniques that directly cool the heat generation sites in the chip, substrate, and/or package [9]. With the promotion of the ICECool program, microfluidic technologies have been developed to cool 3D ICs in the last few years. There are 85 publications available concerning 3D ICs with microfluidics. Five dissertations and 80 journal or conference publications have been presented on basic principles and methods. These research works can be summarized into six categories: cooling structure design, co-design issues, through silicon via (TSV) influence, specific chip application, thermal models, and non-uniform heating and hotspots. Section 2 focuses on cooling structure design. Section 3 describes co-design issues in microfluidic cooling for 3D ICs. Section 4 shows how the design of TSVs in microfludic cooling can be optimized. Section 5 focuses on microfludic cooling for specific chip applications. Section 6 presents thermal models, characteristics, and transmissions. Section 7 focuses on non-uniform heating and hotspots. The last section summarizes the review and concludes.

### 2. Microfluidic Cooling Structure and Manufacture

ICECool programs are working to create many micro/nano microfluidic channels and structures embedded in 3D ICs with high thermal conductivity, as well as thermoelectric materials to link

Micromachines 2018, 9, 287 3 of 14

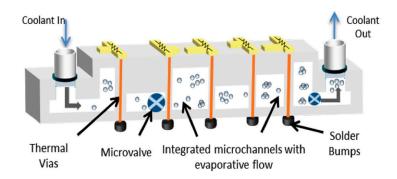

on-chip hotspots to microfluidically cooled microchannels. The proposed intra/inter chip-enhanced cooling methods are required to be compatible with materials, fabrication procedures, and thermal management needs of homogeneous and heterogeneous integration in 3D chip stacks. A conceptual ICECool structure is given in Figure 2 [10,11].

Figure 2. A cross-Sectional conceptual schematic of an ICECool device.

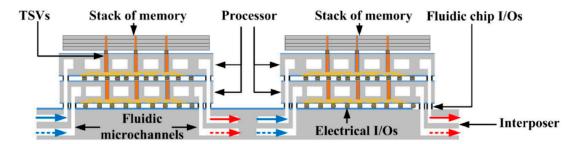

Micropores and microchannels are directly fabricated into intra-chips [12]. The interchip approach uses the microgap as a cooling channel between chips in three-dimensional stacks [13,14]. Based on the conceptual model of the ICECool program, several different structures of microfluidic cooling embedded into 3D ICs have been presented. Yue Zhang et al. proposed tier-specific microfluidic cooling technology, which was experimentally demonstrated in a 3D stack, shown in Figure 3 [15]. The tier-specific cooling approach, compared with conventional microfluidic cooling, can reduce the pumping power by 37.5%, preventing overcooling, when an operating temperature is specified.

**Figure 3.** The tier-specific microfluidic cooling technology in 3D stacks. Reproduced with permission from [15].

In Figure 3, the blue arrows indicate cold coolants and red arrows indicate hot coolants. To develop the structure in Figure 3, Minhaj Hassan et al. attempted to study the influence of temperature on circuit performance and the advantages of using microfluidics technology for continued performance scaling. Experimental results certified that conventional air cooling solutions limit 3D stacks [16]. To solve stack bonding, Yassir Madhour et al. presented a patterned die-to-die thin film bonding method for 3D chip stacks with integrated microfluidic cooling. The method was developed and successfully tested [17]. Paragkumar et al. then demonstrated the manufacture and characterization of a thick silicon interposer, which had low-loss polymer-embedded vias and two dices. The integrated microfluidic heat sink and fluidic and electrical I/Os were embedded into a silicon interposer for high-performance 3D system integration [18].

Modified microfluidic cooling structures, shown in Figure 4, have also been studied. Each chip had its own fluidic inlet and outlet. Flow direction and flow rate were modified independently for each die based on individual demands [19–21]. This approach achieved independent cooling for each tier and can be used for different temperature distributions and velocities.

Micromachines 2018, 9, 287 4 of 14

Figure 4. A 3D system with independent microfluidic cooling. Reproduced with permission from [21].

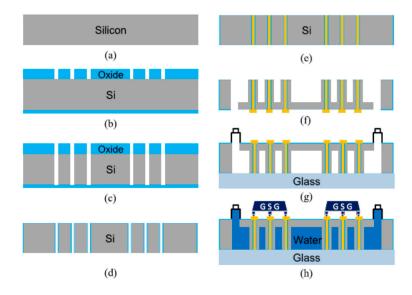

Through silicon vias (TSVs) embedded in the 3D ICs require more complicated processes for microfabrication. Typical processes are shown in Figure 5. The processes started with the deposition of silicon dioxide followed by metal depositing. A thin chrome layer was chosen as an etch mask, as shown in Figure 5b. Using the chrome mask, the silicon dioxide layer was etched, and using a CR-7S chrome etchant, the remaining chrome was removed. Figure 5c shows the resulting silicon dioxide as an etch mask. The high-aspect-ratio Bosch process etched via holes through the silicon wafer. Figure 5d shows that the wet oxidation isolates the vias from the silicon substrate. Titanium and copper seed layers were deposited using an e-beam evaporator at the backside of the wafer. Moreover, chemical mechanical polishing will need to be removed the overburden (Figure 5e). A micropin-fin heat sink structure, shown in Figure 5f, will then be achieved. Finally, a glass slide is assembled into the testbed with fluidic inlet/outlets for fluid delivery, shown in Figure 5g [21].

Figure 5. Schematic of the overall fabrication process.

#### 3. Co-Design of Microfluidic Cooling in 3D Integrated Circuits (ICs)

A new strategy integrates the computational, electrical, physical, thermal, and reliability aspects of a system. The unification of these diverse aspects of ICs is called co-design. The independent optimization and design of each aspect leads to sub-optimal designs considering the lack of understanding of cross-domain interactions and their impacts on the feasibility region of the architectural design space. Thus co-design enables optimization with efficient design and high-performance configurations.

Although the co-design strategy is becoming increasingly imperative in IC design, 3D ICs with efficient microfluidic cooling has become even more critical. The interlayer coupling with cooling structures, and a higher degree of connectivity between components, exacerbates the interdependence between physical design parameters, architectural parameters, and a multitude of metrics of interest

Micromachines 2018, 9, 287 5 of 14

such as performance, hotspot distribution, power, and reliability. The embedded microfluidic cooling greatly influences the former parameters. Co-design becomes critical in 3D ICs with microfluidic cooling.

Jianyong Xie et al. proposed the electrical-thermal co-simulation of 3D systems with fluidic cooling, joule heating, and air convection effects. The finite-volume formulations of heat equations and the voltage distribution equation for both solid medium and fluid flow are carefully explained. Based on the proposed iterative co-simulation method, package voltage dropped and temperature distribution with fluidic cooling effects can be estimated [22]. Zhimin Wan et al. investigated the co-design of multicore architecture and microfluidic cooling for 3D-stacked ICs, in which a 16-core, ×86 multicore die stacked with a second die hosting an L2 SRAM cache was included. In their works, a multicore ×86 compatible cycle-level microarchitecture simulator was reached and integrated with physical power models. The simulator executed benchmark programs to create power traces that drive thermal analysis. After using a compact thermal model, thermal characteristics under liquid cooling were investigated, and four alternative packaging organizations were compared. With a given pumping power, the greatest overall temperature reduction was reached, with two pin-fin-enhanced microgaps and two tiers, where the high power dissipation tier is on the top. At last, the pin-fin parameters were optimized such that significant improvements in energy instruction were made, and leakage power, as well as the height, the diameter, and the longitudinal and transversal spacing, significantly decreased [23]. Bing Shi et al. studied a hybrid 3D-IC cooling method that combined thermal TSVs with micro-channel liquid cooling structures. The thermal TSVs acted as heat removal agents and as beneficial heat conduction paths to the micro-channel structures. The experimental results demonstrated that the proposed hybrid cooling method provided more cooling capability than thermal TSVs alone but, compared with pure microchannel cooling, required 56% less cooling power [24]. Caleb Serafy presented a scheme for multi-domain co-optimization and co-simulation of 3D central processing unit (CPU) architectures with both microfluidic and air cooling solutions, and demonstrated a paradigm for design space modeling and exploration in the co-design scheme, and discussed possible avenues for improvement of this work in the future [25]. Yue Zhang et al. investigated the electrical and thermal co-design of an interlayer microfluidic heat sink and its experimental test-bed, and analyzed design tradeoffs between heat removal capability and the associated TSV parasitics [26].

## 4. Influence of Microfluidic Cooling on Through Silicon Vias

The thickness of chips or of gaps between chips has been modified to embed microfluidic cooling structures into 3D stacks. The coolant and structure will result in a change in electrical characterization including high frequency. The impact of microfluidic cooling on the electrical performance of TSVs needs to be investigated for 3D ICs. The impact of microfluidic cooling on the electrical characteristics of ICs has been studied. Experimental results have demonstrated a 66.2% leakage current decrease in a complementary metal-oxide-semiconductor (CMOS) chip with microfluidic cooling because of the high cooling capability [27]. Results have also shown the frequency-dependent electrical characteristics of liquid coolants when microfluidic cooling is integrated with an L-band filter to demonstrate a tunable corner frequency of the filter considering the dielectric constant of the coolant [28]. To achieve broadband frequency tunability using distilled water and using methanol–water as a coolant, a tunable RF sensor with a conductor-backed coplanar waveguide was integrated [29]. The coolant between ground and signal interconnects bring about signal propagation, signal integrity, loss, and crosstalk [30].

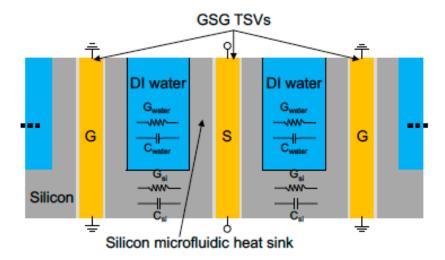

Hanju Oh et al. sought to determine what is missing for microfluidic cooling to influence TSVs. Their works investigated impacts on insertion loss, TSV capacitance, and conductance of microfluidic cooling, considered the design of a microfluidic cooling testbed containing TSVs using two kinds of heat sinks, and reported a high frequency of microfluidic heat-sink-embedded TSVs in deionized water [31]. The signal propagation in TSVs with integrated microfluidic cooling can be seen in Figure 6, which illustrates the ground–signal–ground TSVs with integrated microfluidic

Micromachines 2018, 9, 287 6 of 14

cooling. In such a cooling system, a signal propagating through TSVs will partially encounter capacitance and conductance through silicon and de-ionized (DI) water. Unlike the permittivity of silicon, the permittivity of DI water varied significantly with frequency [32].

**Figure 6.** Ground–signal–ground through silicon vias (TSVs) in a microfluidic heat sink. Reproduced with permission from [32].

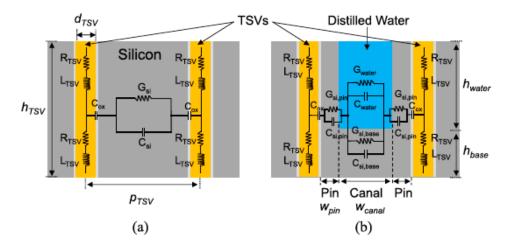

Additionally, Hanju Oh et al. focused on the fabrication of fully isolated TSVs with an aspect ratio of 23:1, investigated the integration of high-aspect-ratio TSVs within a microfluidic heat sink using various fabrication processes, proposed a 3D system with TSVs embedded within interlayer-microfluidic cooling, and described the fabrication and the electrical characterization of high-aspect-ratio TSVs within a micropin-fin heat sink in detail [33]. The distilled water, common acting as a coolant, brought about an impact on the electrical performance of TSVs. Equivalent circuit models of TSVs in a silicon substrate and TSVs in a micropin-fin heat sink filled with distilled water are shown in Figure 7 [34]. This model can be used to analyze the influence of liquid cooling on the electrical performance of TSVs using a microfluidic cooling testbed containing TSVs.

**Figure 7.** Equivalent circuit models for (a) conventional TSVs and (b) TSVs with distilled water. Reproduced with permission from [34].

Hanhua Qian et al. presented an accurate steady-state thermal simulator for both sink-cooled and microfluidic cooled 3D ICs. The thermal effect of TSVs at fine granularity was determined by calculating the anisotropic equivalent thermal conductance of a solid grid cell when TSVs are

Micromachines 2018, 9, 287 7 of 14

inserted. This model can estimate the thermal effect of TSVs on computationally efficiency and fine granularity. It also considers the entrance influence of microchannels based on the most appropriate thermodynamics for microfluidic cooling [35].

## 5. Microfluidic Cooling Application in Specific Application

Microfluidic cooling was demonstrated to achieve excellent thermal management in 3D-stack-integrated structures. Some projects have focused on 3D stack applications with microfluidic cooling. Caleb Serafy et al. used microfluidic cooling architectures in 3D processor stacks, and explored the new design scheme that was available to computer architects when microfluidic cooling was applied to the 3D chips. With microfluidic cooling, these performance improvements became realizable, and new high performance architectures were achieved when cooling was designed considering the architecture. Results showed a 2.4× increase in average performance when comparing a 3D-stacked memory processor with and without micro-fluidic cooling [36]. The relationship between the performance of a 3D field programmable gate array (FPGA) and micro-channel heat sink design is very complicated and requires a comprehensive method that identifies the optimal design of 3D FPGAs subject to thermo-electrical constraints. Zhiyuan Yang et al. proposed an analysis scheme for 3D FPGAs in which microchannels based on fluidic cooling were embedded to study the influence of channel density on performance and cooling. They provided guidelines for designing 3D FPGAs with micro-channel cooling and identified the optimal design for each benchmark. Optimal design using the scheme can increase the energy efficiency and operating frequency by up to 80.3% and 124.0%, when compared to original 3D FPGA designs with fixed thermal heat sinks [37]. To overcome the limit of microfluidic cooling experiments to silicon with effective heaters representing the heat generating circuitry, a micropin-fin heat sink was etched into the backside of an Altera FPGA with a 28 nm CMOS process. The FPGA was cooled with inlet water temperatures as high as 50 °C, enabling high efficiency through heat exchange directly to ambient air, or waste heat reuse [38].

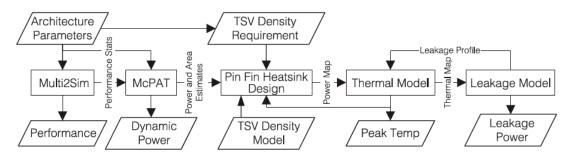

Three-dimensional CPUs have also been used to study microfluidic cooling. Caleb Serafy et al. performed a design of microfluidic cooling on a 3D CPU, in which microfluidic cooling was shown as a necessary aggressive cooling solution to unlock the true potential of 3D ICs. After simulating a spectrum of 3D CPU architectures, a 2.3× improvement in performance was reached when microfluidic cooling and floor plan co-optimization was applied [39]. A simulation flowchart for the thermoelectric co-design of 3D CPUs with embedded microfluidic cooling pin-fin heat sinks, which identifies optimal architectural and heat sink design points, is shown in Figure 8, showing the design methodology of a 3D CPU architecture with the microfluidic heat sink that is required to find optimal design choices subject to both physical constraints [40]. Yue Zhang et al., with respect to tier microfluidic cooling, reported on a processor stack in which TSVs with a 23:1 aspect ratio were integrated into a microfluidic heat sink and a vacuum cavity was integrated in the low power tier. Therefore the tier was protected from temperature variation and non-uniformity [41].

Figure 8. Flowchart of the analysis approach.

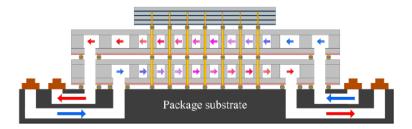

High-performance computing is another application with respect to microfluidic cooling. Li Zheng et al. proposed a silicon interposer platform using microfluidic cooling for high-performance

Micromachines 2018, 9, 287 8 of 14

3D computing systems, in which a logic stack was embedded into the microfluidic heat sink in each tier and a memory stack was assembled side by side on a silicon interposer. High-bandwidth signaling between the two stacks was achieved in the system [42]. The thermal experimental results based on the measured thermal resistance showed a 40.1% reduction in the silicon interposer temperature with microfluidic cooling compared to air cooling [43]. Mark D. Schultz et al. published works on the integration of microfluidic cooling with a functional high-performance server. Two-phase flow boiling was proposed as a potential method for cooling high-performance computer systems, and detailed descriptions on the design, fabrication, testing, and characterization of the microfluidic two-phase cooling of a high power microprocessor were given [44,45].

Besides these applications, systems on chips (SoCs) or compound semiconductor devices have been applied. Mohamed M. Sabry et al. demonstrated the potential of power delivery and cooling issues, caused by limitations in Dennard scaling, using a disruptive approach for integrated power generation and cooling based on multiprocessor SoCs. Indeed, this new approach used the coolant fluid as a means of delivering energy to the chips [46]. Wen Yueh et al. presented the design, experimental characterization, and feasibility analysis of integrated in-package fluidic cooling for mobile SoCs. A pin-fin interposer for fluidic cooling was designed and integrated with a commercial SoC. The demonstrated system was integrated with an active low-power piezoelectric pump controlled by the SoC itself and a metal/acrylic-based board-scale heat spreader and exchanger. Different software-based policies in the SoC for controlling the fluid flow based on the SoC's temperature and performance were implemented and compared. The measurement results demonstrated that in-package fluidic cooling, compared to external passive cooling, improves the SoC's energy efficiency and reduces the design footprint [47]. To reduce the temperature of high-power X band gallium nitride devices and amplifiers, an integrated microfluidic cooling scheme on multilayer organic liquid crystal polymer substrate has been set up. Experimental results demonstrated the need for dynamic microfluidics in packages to mitigate thermal effects [48,49], and the microfluidic cooling technique improved a GaN monolithic microwave IC amplifier's gain by over 4 dB, its maximum output power by over 8 dB, and its power efficiency by 3% to 5% [50].

## 6. Thermal Models, Characteristics, and Transmissions in Microfluidic Cooling

One of the important issues to achieve accuracy and efficiency in the thermal management of 3D ICs is to construct thermal models including all relevant parameters. Outmane Lemtiri Chlieh et al. set up a thermal model to predict the overall thermal resistance of the organic heat sink in the case of a moving coolant inside a microfluidic channel based on existing thermal models in the literature, and then fabricated and tested four sets of microfluidic channels with different thicknesses. The temperature measurements of the resistors with different power ratings and sizes agreed with the model predictions [51]. Model simulators will thus be necessary. Wan Z. et al. studied a coupled power-thermal simulator that was used to analyze the influence of on-chip micropin-fin cooling design on both the electrical and thermal performance of 3D ICs when working with real applications and producing hotspot maps. The leakage power accounted for 55.8% of the dynamic power consumption of the chip. An ambient heat transfer coefficient had very little influence on the electrical and thermal performance, while the increasing ambient temperature strongly influences the fluid temperature [52].

For thermal management in GaN-based microelectronic devices with microfluidic cooling, Gunjan Agarwal et al. used finite element analysis to achieve numerical thermal models compatible with heterogeneous integration with conventional silicon-based CMOS devices [53]. Considering the influence of structures, Guilian Wang et al. experimentally and numerically investigated the heat transfer and friction characteristics of microfluidic heat sinks with various structures such as rectangular, triangular, and semicircular ribs. The structures were fabricated on the sidewalls of microfluidic channels by a surface micromachining process and used as turbulators to improve the heat transfer rate of the microfluidic heat sink. The results indicated that the utilizing of micro-ribs provided a better heat transfer rate but also increased the pressure drop penalty for microchannels [54].

Micromachines 2018, 9, 287 9 of 14

However, Xuchen Zhang et al. worked on thermal testbeds with embedded micropin-fin heat sinks. They designed and microfabricated two micropin-fin arrays for experiments. The results obtained from the two testbeds were compared and analyzed, and showed that the density of micropin-fins has a significant impact on thermal performance [55].

## 7. Non-Uniform Heating and Hotspots

Hotspots in 3D ICs arise due to the non-uniform utilization of underlying ICs during chip operation. The hotspot areas and the background area of the chip result in excessive temperature gradients across the chip, which adversely affects chip performance and reliability, as large temperature gradients increase thermal stresses. To tackle hotspot cooling, a number of novel techniques have been proposed, and can be summarized into five classes shown in Table 1.

**Table 1.** Summary of the literature review for non-uniform heating and hotspots.

| Categories                                               | The Methods Used in the Literatures                                                                                                                                                                                                                                                                                            | References                                                   |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| The analysis of non-uniform<br>heating and hotspots      | A novel, low profile jet impingement was given within an individual channel suitable for targeting hotspots in a densely packed circuit, at the low Reynolds numbers prevalent in micro-fluidic applications (Re < 500).                                                                                                       | A.M. Waddell et al. (2016) [56]                              |

|                                                          | A micro-fluidic cooling chip with different-sized hotspots was fabricated to investigate the influence of hotspot characteristics on the cooling ability of the embedded micro-channel.                                                                                                                                        | Y.D. Pi et al. (2016) [57]                                   |

|                                                          | A one-dimensional, semi-empirical approach was presented for quick design of a microchannel heat sink for targeted, energy-efficient liquid cooling of hotspots in microprocessors.                                                                                                                                            | C.S. Sharma (2016) [58]                                      |

| Using digital microfluidics to solve non-uniform heating | A digital microfluidic cooling platform enabled adaptive cooling in IC design.                                                                                                                                                                                                                                                 | P.Y. Paik et al. (2008) [5]                                  |

|                                                          | A cooling method based on high-speed electrowetting manipulation of discrete sub-microliter droplets was achieved under voltage control with volume flow rates in excess of 10 mL/min.                                                                                                                                         | V.K. Pamula et al. (2003) [59]                               |

|                                                          | An alternative cooling technique based on a recently invented "digital microfluidic" platform was reached.  An innovative approach to regulate hotspot temperature was demonstrated by creating a hydrophilic spot (H-spot) on the heater that retains a small droplet while the main coolant droplet passes over the hotspot. | P.Y. Paik et al. (2008) [60]  G.S. Bindiganavale (2015) [61] |

|                                                          | A novel digital microfluidic liquid cooling system using electrowetting on dielectric developed for demonstrating and studying hotspot cooling towards electronics thermal management was shown.                                                                                                                               | G.S. Bindiganavale et al. (2014<br>[62]                      |

|                                                          | The high accuracy and consistency in volume of coolant nanodrops dispensed from the reservoir, the fast motion of coolant nanodrops to the hotspot to avoid dry-out, and the simultaneous achievement of both small volume and high frequency of nanodrop that arrives to the hotspot were analyzed.                           | J.B. Yaddessalage (2013) [63]                                |

|                                                          | A single-sided digital microfluidic device that enables not only effective liquid handling on a single-sided surface but also two-phase heat transfer to enhance thermal rejection performance was created.                                                                                                                    | S.Y. Park et al. (2017) [64]                                 |

Micromachines 2018, 9, 287 10 of 14

Table 1. Cont.

| Categories                                                     | The Methods Used in the Literatures                                                                                                                                                                                                               | References                        |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Changing channel clustering for non-uniform heating            | An efficient clustering algorithm was used to guide the division of microchannels into clusters and the allocation of cooling resources to each cluster in order to achieve an effective microfluidic cooling with a minimal total flow rate.     | H.H. Qian et al. (2011) [65]      |

|                                                                | A novel liquid-cooling concept was studied, for targeted, energy-efficient cooling of hotspots through passively optimized microchannel structures etched into the backside of a chip.                                                            | C.S. Sharma (2014) [66]           |

|                                                                | The model was presented for independent interlayer microfluidic cooling for heterogeneous 3D IC applications.                                                                                                                                     | Y. Zhang (2013) [20]              |

| Using novel structures for non-uniform heating                 | A single microfluidic loop was demonstrated for the combined and efficient cooling of hotspot and moderate power areas.                                                                                                                           | D. Lorenzini et al. (2016) [67]   |

|                                                                | Non-uniform micropin-fin heat sinks for the cooling of ICs with non-uniform maps were studied.                                                                                                                                                    | T.E. Sarvey et al. (2017) [68]    |

|                                                                | Fine pitch electrical microbumps and annular shaped fluidic microbumps were achieved to enable high bandwidth die-to-die signaling, embedded microfluidic cooling and power delivery for silicon interposer and 3D integrated electronics systems | L. Zheng et al. (2014) [69]       |

|                                                                | Temperature-regulated microvalves were designed for energy-efficient fluidic cooling of microelectronic systems.                                                                                                                                  | H. Azarkish et al. (2017) [70]    |

|                                                                | A liquid cooling device was achieved based on a matrix of microfluidic cells with individually flow rate controlling microvalves for temperature uniformities.                                                                                    | G. Laguna et al. (2017) [71]      |

| The test and protocols for non-uniform heating solving methods | Novel thermal testbeds with embedded micropin-fin heat sinks for 3D ICs were created.                                                                                                                                                             | X.C. Zhang et al. (2016) [72]     |

|                                                                | Microfluidic system protocols for integrated on-chip communication and cooling were demonstrated.                                                                                                                                                 | S.A. Wirdatmadja et al. (2017) [7 |

### 8. Conclusions

The discussion above addresses all available publications using microfluidic cooling in 3D ICs. Most research works were published in the last five years and focused on fundamental principles, models, and application examples in microfluidic cooling. Based on all analyses, several future works are suggested:

- Determining how non-uniform heating can be achieved is important for applying microfluidic cooling to 3D ICs, but no exact methods and models are yet available for evaluating hotspots.

- Digital microfluidics is an effective approach used in the cooling processes, but how drive voltage needs to be reduced when the cooling structures are embedded into 3D stacked ICs.

- More systematic achievements are required in manufacturing, testing, and designing methods when using microfluidic cooling in 3D ICs.

**Author Contributions:** Y.Y. and C.H. analyzed the data; P.R. contributed the methods; S.W. summarized and wrote the paper.

**Acknowledgments:** The work was supported by the Science and Technology Development Program of Shaanxi (No. 2016GY-091) and the Natural Science Foundation of Shenzhen (No. JCYJ2016042915311 908).

Micromachines 2018, 9, 287 11 of 14

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

1. Beyne, E. The rise of the 3rd dimension for system integration. In Proceedings of the International Interconnect Technology Conference, Burlingame, CA, USA, 5–7 June 2006.

- 2. Cheramy, S.; Charbonnier, J.; Henry, D.; Astier, A.; Chausse, P.; Neyret, M.; Brunet-Manquat, C.; Verrun, S.; Sillon, N.; Bonnot, L.; et al. 3D integration process flow for set-top box application: Description of technology and electrical results. In Proceedings of the 2009 EMPC 2009 European Microelectronics and Packaging Conference, Rimini, Italy, 15–18 June 2009.

- 3. 2015 International Technology Roadmap for Semiconductors (ITRS). Available online: https://www.semiconductors.org/main/2015\_international\_technology\_roadmap\_for\_semiconductors\_itrs/ (accessed on 7 June 2018).

- 4. Bar-Cohen, A. Thermal management of on-chip hot spots and 3D chip stacks. In Proceedings of the IEEE International Conference on Microwaves, Communications, Antennas and Electronics Systems, Tel Aviv, Israel, 9–11 November 2009.

- 5. Paik, P.Y.; Pamula, V.K.; Chakrabarty, K. A digital-microfluidic approach to chip cooling. *IEEE Des. Test Comput.* **2008**, 25, 372–381. [CrossRef]

- 6. Demello, A.J. Control and detection of Chemical reactions in microfluidic systems. *Nature* **2006**, *442*, 394–402. [CrossRef] [PubMed]

- 7. Available online: http://money.cnn.com/magazines/business2/business2\_archive/2004/09/01/toc.html (accessed on 7 June 2018).

- 8. Whitesides, G.M. The origins and the future of microfluidics. *Nature* **2006**, 442, 368–373. [CrossRef] [PubMed]

- Keller, J. DARPA moves forward with ICECool thermal-management program for embedded computing. Mil. Aerosp. Electron. 2013, 6, 15–23.

- Altman, D.H.; Gupta, A.; Tyhach, M. Development of a diamond microfluidics-based intra-chip cooling technology for GaN. In ASME 2015 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems Collocated with the ASME 2015 13th International Conference on Nanochannels, Microchannels, and Minichannels (pp. V003T04A006-V003T04A006); American Society of Mechanical Engineers: New York, NY, USA, 2015.

- 11. Bar-Cohen, A.; Maurer, J.J.; Felbinger, J.G. DARPA's intra/inter chip enhanced cooling (ICECool) program. In Proceedings of the CS MANTECH Conference, New Orleans, LA, USA, 13–16 May 2013.

- 12. Yarin, L.P.; Mosyak, A.; Hetsroni, G. Fluid Flow, Heat Transfer and Boiling in Micro-Channels; Springer: Berlin/Heidelberg, Germany, 2009.

- 13. Bar-Cohen, A.; Geisler, K.J.L. Cooling the electronic brain. Mech. Eng. 2011, 133, 38–41.

- 14. Bar-Cohen, A.; Sheehan, J.R.; Rahim, E. Two-phase thermal transport in microgap channels—Theory, experimental results, and predictive relations. *Microgravity Sci. Technol.* **2012**, 24, 1–15. [CrossRef]

- 15. Zhang, Y.; Zheng, L.; Bakir, M.S. 3-D stacked tier-specific microfluidic cooling for heterogeneous 3-D ICs. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2013**, *3*, 1811–1819. [CrossRef]

- 16. Hassan, S.M.; Yalamanchili, S. Understanding the impact of air and microfluidics cooling on performance of 3D stacked memory systems. In Proceedings of the 2nd International Symposium on Memory Systems, Alexandria, VA, USA, 3–6 October 2016.

- 17. Madhour, Y.; Brunschwiler, T.; Kazzi, M.E.; Thome, J.R. Patterned die-to-die thin film bonding for 3D chip stacks with integrated microfluidic cooling. In Proceedings of the International Conference on Electronic Packaging Technology and High Density Packaging, Guilin, China, 13–16 August 2012.

- 18. Thadesar, P.A.; Li, Z.; Bakir, M.S. Low-loss silicon interposer for three-dimensional system integration with embedded microfluidic cooling. In Proceedings of the Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014.

- 19. Zhang, Y.; Dembla, A.; Joshi, Y.; Bakir, M.S. 3D stacked microfluidic cooling for high-performance 3D ICs. In Proceedings of the 62nd Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012.

- 20. Zhang, Y.; Bakir, M.S. Independent interlayer microfluidic cooling for heterogeneous 3D IC applications. *Electron. Lett.* **2013**, 49, 404–406. [CrossRef]

Micromachines 2018, 9, 287 12 of 14

21. Zheng, L.; Zhang, Y.; Bakir, M.S. Design, fabrication and assembly of a novel electrical and microfluidic I/Os for 3-D chip stack and silicon interposer. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 28–31 May 2013.

- 22. Xie, J.; Swaminathan, M. Electrical-thermal co-simulation of 3D integrated systems with micro-fluidic cooling and joule heating effects. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2011**, *1*, 234–246. [CrossRef]

- 23. Wan, Z.; Xiao, H.; Joshi, Y.; Yalamanchili, S. Co-design of multicore architectures and microfluidic cooling for 3D stacked ICs. In Proceedings of the International Workshop on Thermal Investigations of ICS and Systems, Berlin, Germany, 25–27 September 2013.

- 24. Shi, B.; Srivastava, A.; Bar-Cohen, A. Co-design of micro-fluidic heat sink and thermal through-silicon-vias for cooling of three-dimensional integrated circuit. *IET Circu its Dev. Syst.* **2013**, 7, 223–231. [CrossRef]

- 25. Caleb, S. *Architectural-Physical Co-Design of 3D CPUs with Microfluidic Cooling*; University of Maryland: College Park, MD, USA, 2016.

- Zhang, Y.; Dembla, A.; Bakir, M.S. Silicon micropin-fin heat sink with integrated TSVs for 3-D ICs: Tradeoff analysis and experimental testing. *IEEE Trans. Compon. Packag. Manuf. Technol.* 2013, 3, 1842–1850. [CrossRef]

- 27. Wan, Z.; Wen, Y.; Joshi, Y.; Mukhopadhyay, S. Enhancement in CMOS chip performance through microfluidic cooling. In Proceedings of the International Workshop on Thermal Investigations of ICS and Systems, London, UK, 24–26 September 2014.

- 28. Chlieh, O.L.; Khan, W.T.; Papapolymerou, J. L-band tunable microstrip bandpass filter on multilayer organic substrate with integrated microfluidic channel. In Proceedings of the Microwave Symposium, Tampa, FL, USA, 1–6 June 2014.

- 29. Cui, Y.; Sun, J.; He, Y.; Wang, Z.; Wang, P. A simple, tunable, and highly sensitive radio-frequency sensor. *Appl. Phys. Lett.* **2013**, *103*. [CrossRef] [PubMed]

- 30. Curran, B.; Ndip, I.; Guttovski, S.; Reichl, H. The impacts of dimensions and return current path geometry on coupling in single ended Through Silicon Vias. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009.

- 31. Oh, H.; Zhang, X.; May, G.S.; Bakir, M.S. High-frequency analysis of embedded microfluidic cooling within 3-D ICs using a TSV testbed. In Proceedings of the 66th Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016; pp. 68–73.

- 32. Oh, H.; Zhang, Y.; May, G.S.; Bakir, M.S. TSVs embedded in a microfluidic heat sink: High-frequency characterization and thermal modeling. In Proceedings of the 20th Workshop on Signal and Power Integrity (SPI), Turin, Italy, 8–11 May 2016; pp. 1–4.

- 33. Oh, H.; Gu, J.M.; Hong, S.J.; May, G.S.; Bakir, M.S. High-aspect ratio through-silicon vias for the integration of microfluidic cooling with 3D microsystems. *Microelectron. Eng.* **2015**, *142*, 30–35. [CrossRef]

- 34. Oh, H.; May, G.S.; Bakir, M.S. Analysis of signal propagation through TSVs within distilled water for liquid-cooled microsystems. *IEEE Trans. Electron Dev.* **2016**, *63*, 1176–1181. [CrossRef]

- 35. Qian, H.; Liang, H.; Chang, C.H.; Zhang, W. Thermal simulator of 3D-IC with modeling of anisotropic TSV conductance and microchannel entrance effects. In Proceedings of the 18th Asia and South Pacific Design Automation Conference (ASP-DAC), Yokohama, Japan, 22–25 January 2013.

- 36. Serafy, C.; Shi, B.; Srivastava, A.; Yeung, D. High performance 3D stacked DRAM processor architectures with micro-fluidic cooling. In Proceedings of the IEEE International 3D Systems Integration Conference, San Francisco, CA, USA, 2–4 October 2013.

- Yang, Z.; Srivastava, A. Physical design of 3D FPGAs embedded with micro-channel-based fluidic cooling. In Proceedings of the Acm/sigda International Symposium on Field-Programmable Gate Arrays, Monterey, CA, USA, 21–23 February 2016.

- 38. Sarvey, T.E.; Zhang, Y.; Cheung, C.; Gulata, R.; Rahman, A.; Dasu, A. Monolithic integration of a micropin-fin heat sink in a 28-nm FPGA. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2017**, 7, 1617–1624. [CrossRef]

- 39. Serafy, C.; Bar-Cohen, A.; Srivastava, A.; et al. Unlocking the true potential of 3-D CPUs with microfluidic cooling. *IEEE Trans. Larg. Scale Integr. Syst.* **2016**, *24*, 1515–1523. [CrossRef]

- 40. Serafy, C.; Yang, Z.; Hu, Y.; Srivastava, A.; Joshi, Y. Thermo-electric co-design of 3D CPUs and embedded micro-fluidic pin-fin heatsinks. *IEEE Des. Test* **2016**, *33*, 40–48. [CrossRef]

- 41. Zhang, Y.; Oh, H.; Bakir, M.S. Within-tier cooling and thermal isolation technologies for heterogeneous 3D ICs. In Proceedings of the 3D Systems Integration Conference, San Francisco, CA, USA, 2–4 October 2013.

Micromachines 2018, 9, 287 13 of 14

Zheng, L.; Zhang, Y.; Zhang, X.; Bakir, M.S. Silicon interposer with embedded microfluidic cooling for high-performance computing systems. In Proceedings of the Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015.

- 43. Li, Z.; Yang, Z.; Bakir, M.S. A Silicon interposer platform utilizing microfluidic cooling for high-performance computing systems. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2017**, *5*, 1379–1386.

- 44. Schultz, M.D.; Parida, P.R.; Gaynes, M.; Ozsun, O.; McVicker, G.; Drechsler, U.; Chainer, T. Microfluidic two-phase cooling of a high power microprocessor part A: Design and fabrication. In Proceedings of the IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA, 30 May–2 June 2017.

- 45. Schultz, M.D.; Parida, P.R.; Gaynes, M.; Ozsun, O.; McVicker, G.; Drechsler, U.; Chainer, T. Microfluidic two-phase cooling of a high power microprocessor part B: Test and characterization. In Proceedings of the IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA, 30 May–2 June 2017.

- 46. Sabry, M.M.; Sridhar, A.; Atienza, D.; Ruch, P. Integrated microfluidic power generation and cooling for bright silicon MPSoCs. In Proceedings of the Design, Automation and Test in Europe Conference and Exhibition, Dresden, Germany, 24–28 March 2014.

- 47. Wen, Y.; Wan, Z.; He, X.; Yalamanchili, S.; Joshi, Y. Active fluidic cooling on energy constrained system-on-chip systems. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2017**, *7*, 1813–1822.

- 48. Chlieh, O.L.; Morcillo, C.A.D.; Pavlidis, S.; Khan, W.; Papapolymerou, J. Integrated microfluidic cooling for GaNdevices on multilayer organic LCP substrate. In Proceedings of the Microwave Symposium Digest, Seattle, WA, USA, 2–7 June 2013.

- 49. Chlieh, O.L.; Papapolymerou, J. Hybrid integrated microfluidic channels on multilayer organic substrate and on copper for tuning and cooling an RF reconfigurable S-/C-band GaN-based power amplifier. *IEEE Trans. Microw. Theory Tech.* **2017**, *65*, 156–164. [CrossRef]

- 50. Ditri, J.; Pearson, R.R.; Cadotte, R.; Hahn, J.W.; Fetterolf, D.; McNulty, M.; Luppa, D. GaN unleashed: The benefits of microfluidic cooling. *IEEE Trans. Semicond. Manuf.* **2016**, *29*, 376–383. [CrossRef]

- 51. Chlieh, O.L.; Khan, W.T.; Papapolymerou, J. Thermal modelling of microfluidic channels for cooling high power resistors on multilayer organic liquid crystal polymer substrate. *J. Electron. Packag.* **2015**, 137. [CrossRef]

- 52. Wan, Z.; Xiao, H.; Joshi, Y.; Yalamanchili, S. S3-P9: Thermal and electrical performance of microfluidically cooled 3D ICs with non-uniform power dissipation. In Proceedings of the Lester Eastman Conference on High PERFORMANCE Devices, Ithaca, NY, USA, 5–7 August 2014.

- 53. Agarwal, G.; Kazior, T.; Kenny, T.; Weinstein, D. Modeling and analysis for thermal management in GaN HEMTs using microfluidic cooling. *J. Electron. Packag.* **2017**, 139. [CrossRef]

- 54. Wang, G.L.; Yang, D.W.; Wang, Y.; Niu, D.; Zhao, X.L.; Ding, G.F. Heat transfer and friction characteristics of the microfluidic heat sink with variously-shaped ribs for chip cooling. *Sensors* **2015**, *15*, 9547–9562. [CrossRef] [PubMed]

- 55. Zhang, X.; Han, X.; Sarvey, T.T.; Green, C.E.; Kottke, P.A. Three-dimensional integrated circuit with embedded microfluidic cooling: Technology, thermal performance, and electrical implications. *J. Electron. Packag.* **2016**, 138. [CrossRef]

- 56. Waddell, A.M.; Punch, J.; Stafford, J.; Jeffers, N. The characterization of a low-profile channel–confined jet for targeted hot-spot cooling in microfluidic applications. *Int. J. Heat Mass Transf.* **2016**, *101*, 620–628. [CrossRef]

- 57. Pi, Y.; Wang, W.; Chen, J.; Jin, Y. Microfluidic cooling for distributed hot-spots. In Proceedings of the Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016.

- 58. Sharma, C.S.; Tiwari, M.K.; Poulikakos, D. A simplified approach to hotspot alleviation in microprocessors. *Appl. Ther. Eng.* **2016**, *93*, 1314–1323. [CrossRef]

- 59. Pamula, V.K.; Chakrabarty, K. Cooling of integrated circuits using droplet-based microfluidics. In Proceedings of the 13th ACM Great Lakes Symposium on Vlsi, Washington, DC, USA, 28–29 April 2003.

- 60. Paik, P.Y.; Pamula, V.K.; Chakrabarty, K. Adaptive cooling of integrated circuits using digital microfluidics. *IEEE Trans. Larg. Scale Integr. Syst.* **2008**, *16*, 432–443. [CrossRef]

- 61. Bindiganavale, G.S. Study of Hotspot Cooling for Integrated Circuits Using Electrowetting on Dielectric Digital Microfluidic System; The University of Texas: Arlington, TX, USA, 2015.

Micromachines 2018, 9, 287 14 of 14

62. Bindiganavale, G.; You, S.M.; Moon, H. Study of hotspot cooling using electrowetting on dielectric digital microfluidic system. In Proceedings of the International Conference on MICRO Electro Mechanical Systems, San Francisco, CA, USA, 26–30 January 2014.

- 63. Jagath, B. Yaddessalage, Study of the Capabilities of Electrowetting on Dielectric Digital Microfluidics towards the High efficient thin film Evaporative Cooling Platform; The University of Texas: Arlington, TX, USA, 2013.

- 64. Park, S.Y.; Nam, Y. Single-Sided Digital Microfluidic (SDMF) Devices for Effective Coolant Delivery and Enhanced Two-Phase Cooling. *Micromachines* **2017**, *8*, 3. [CrossRef]

- 65. Qian, H.; Chang, C.-H.; Yu, H. An efficient channel clustering and flow rate allocation algorithm for: Non-uniform microfluidic cooling of 3D integrated circuits. *Integr. VLSI J.* **2013**, *46*, 57–68. [CrossRef]

- 66. Sharma, C.S.; Tiwari, M.K.; Zimmermann, S.; Brunschwiler, T.; Schlottig, G.; Michel, B.; Poulikakos, D. Energy efficient hotspot-targeted embedded liquid cooling of electronics. *Appl. Energy* **2015**, *138*, 414–422. [CrossRef]

- 67. Lorenzini, D.; Green, C.; Sarvey, T.E.; Zhang, X.; Hu, Y.; Fedorov, A.G.; Bakir, M.S.; Joshi, Y. Embedded single phase microfluidic thermal management for non-uniform heating and hotspots using microgaps with variable pin fin clustering. *Int. J. Heat Mass Transf.* **2016**, *103*, 1359–1370. [CrossRef]

- 68. Sarvey, T.E.; Hu, Y.; Green, C.E.; Kottke, P.A.; Woodrum, D.C.; Joshi, Y.K.; Fedorov, A.G.; Sitaraman, S.K.; Bakir, M.S. Integrated circuit cooling using heterogeneous micropin-fin arrays for nonuniform power maps. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2017**, 7, 1465–1475. [CrossRef]

- 69. Zheng, L.; Zhang, Y.; Huang, G.; Bakir, M.S. Novel electrical and fluidic microbumps for silicon interposer and 3-D ICs. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2014**, *4*, 777–785. [CrossRef]

- Azarkish, H.; Barrau, J.; Coudrain, P.; Savelli, G.; Collin, L.; Frechette, L.G. Self-adaptive microvalve array

for energy efficient fluidic cooling in microelectronic systems. In Proceedings of the 16th Intersociety

Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA,

30 May–2 June 2017; pp. 522–529.

- 71. Laguna, G.; Azarkish, H.; Vilarrubi, M.; Ibariez, M.; Roseli, J.; Betancourt, Y. Microfluidic cell cooling system for electronics. In Proceedings of the International Workshop on Thermal Investigations of ICS and Systems, Orlando, FL, USA, 30 May–2 June 2017.

- 72. Sahu, V.; Fedorov, A.G.; Joshi, Y.K. Transient characterization of hybrid microfluidic-thermoelectric cooling scheme for dynamic thermal management of microprocessor. *J. Electron. Packag.* **2014**, *136*. [CrossRef]

- 73. Wirdatmadja, S.A.; Moltchanov, D.; Balasubramaniam, S.; Koucheryavy, Y. Microfluidic system protocols for integrated on-chip communications and cooling. *IEEE Access* **2017**, *5*, 2417–2429. [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).