# **A Brief Overview of the Rapid Progress and Proposed Improvements in Gallium Nitride Epitaxy and Process for Third-Generation Semiconductors with Wide Bandgap**

An-Chen Liu<sup>1</sup>, Yung-Yu Lai<sup>2</sup>, Hsin-Chu Chen<sup>3,\*</sup>, An-Ping Chiu<sup>4</sup> and Hao-Chung Kuo<sup>1,4,\*</sup>

- <sup>1</sup> Department of Photonics, Institute of Electro-Optical Engineering, College of Electrical and Computer Engineering, National Yang Ming Chiao Tung University, Hsinchu 30010, Taiwan

- <sup>2</sup> Research Center for Applied Sciences, Academia Sinica, Taipei 114699, Taiwan

- <sup>3</sup> Institute of Advanced Semiconductor Packaging and Testing, College of Semiconductor and Advanced Technology Research, National Sun Yat-sen University, Kaohsiung 804201, Taiwan

- <sup>4</sup> Semiconductor Research Center, Hon Hai Research Institute, Taipei 114699, Taiwan

- \* Correspondence: chenhc@mail.nsysu.edu.tw (H.-C.C.); hckuo@faculty.nctu.edu.tw (H.-C.K.); Tel.: +886-7-525-2000 (ext. 6612) (H.-C.C.); +886-3-571-2121 (ext. 31986) (H.-C.K.)

**Abstract:** In this paper, we will discuss the rapid progress of third-generation semiconductors with wide bandgap, with a special focus on the gallium nitride (GaN) on silicon (Si). This architecture has high mass-production potential due to its low cost, larger size, and compatibility with CMOS-fab processes. As a result, several improvements have been proposed in terms of epitaxy structure and high electron mobility transistor (HEMT) process, particularly in the enhancement mode (E-mode). IMEC has made significant strides using a 200 mm 8-inch Qromis Substrate Technology (QST<sup>®</sup>) substrate for breakdown voltage to achieve 650 V in 2020, which was further improved to 1200 V by superlattice and carbon-doped in 2022. In 2016, IMEC adopted VEECO metal-organic chemical vapor deposition (MOCVD) for GaN on Si HEMT epitaxy structure and the process by implementing a three-layer field plate to improve dynamic on-resistance (R<sub>ON</sub>). In 2019, Panasonic HD-GITs plus field version was utilized to effectively improve dynamic R<sub>ON</sub>. Both reliability and dynamic RON have been enhanced by these improvements.

Keywords: gallium nitride; high electron mobility transistor; GaN on Si/SiC/QST

# 1. Introduction

GaN was a wide-bandgap semiconductor material with excellent electrical and optical properties [1–3], making it a promising candidate for various electronic and optoelectronic devices. In particular, the unique properties of GaN make it a popular choice for high-power and high-frequency applications [4–7], such as power electronics [8,9], RF amplifiers [6,7], and light-emitting diodes (LEDs) [10–13]. One of the key challenges in realizing the full potential of GaN devices was the quality of the epitaxial layer. The epitaxial layer was a thin layer of GaN that was grown on a substrate, and it plays a critical role in determining the performance and reliability of GaN devices [14–19]. Therefore, it was essential to have a thorough understanding of the epitaxial growth process and the structural properties of the epitaxial layer [20–25].

In recent years, significant progress has been made in improving the quality of GaN epitaxial layers through the development of advanced growth techniques and optimization of process parameters. The problem in GaN epitaxial layers was attributed to several factors, including defects [26,27], traps [28], and dislocations [29] in the material. These defects acted as sites for electron trapping and recombination, leading to localized heating and thermal runaway [30–32]. In addition, the high electric fields in GaN devices led to impact ionization and the creation of electron-hole pairs, which further deteriorate the breakdown problem [33]. To address the breakdown problem in GaN devices, scientists

Citation: Liu, A.-C.; Lai, Y.-Y.; Chen, H.-C.; Chiu, A.-P.; Kuo, H.-C. A Brief Overview of the Rapid Progress and Proposed Improvements in Gallium Nitride Epitaxy and Process for Third-Generation Semiconductors with Wide Bandgap. *Micromachines* 2023, *14*, 764. https://doi.org/ 10.3390/mi14040764

Academic Editor: Neha Aggarwal

Received: 7 March 2023 Revised: 24 March 2023 Accepted: 27 March 2023 Published: 29 March 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). developed various solutions. One approach was to optimize the growth conditions of GaN epitaxial layers to reduce the density of defects and dislocations. This was achieved by using advanced growth techniques, such as MOCVD and molecular beam epitaxy (MBE), and by incorporating buffer layers and strain engineering [34–36]. Another approach was to develop new device structures and architectures that could mitigate the breakdown problem. For example, the use of field plates [37,38], edge termination structures [39,40], and deep trench isolation [41] helped to reduce the electric field concentration and improve the breakdown voltage of GaN devices. In addition, the use of advanced gate dielectrics, such as Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, helped to reduce the gate leakage and improve the device's reliability [42–44].

Overall, the breakdown problem in GaN epitaxial layers was a complex issue that required a multidisciplinary approach involving materials science, device physics, and electrical characterization. By developing advanced growth techniques and device structures, and by improving the understanding of the underlying physics, scientists were able to overcome the challenges and unlock the full potential of GaN devices for high-power and high-frequency applications. To improve these challenges, various characterization techniques have been developed to evaluate the structural properties of GaN epitaxial layers. These techniques include optical microscopy (OM) [45], atomic force microscopy (AFM) [46], photoluminescence (PL) [47,48], X-ray diffraction (XRD) [49,50], and transmission electron microscopy (TEM) [51,52], among others. These techniques enable researchers to evaluate the structural properties of GaN epitaxial layers at different scales and provide valuable insights into the growth process and the quality of the epitaxial layer.

In this paper, we review the recent advances in GaN epitaxial growth and the characterization techniques used to evaluate the structural properties of the epitaxial layer. We also discuss the challenges that need to be improved and the future directions for the development of GaN devices. The goal of the study is to provide a comprehensive overview of the current state of the art in GaN epitaxy and research in the enhancement of GaN devices. With the increasing issue of global warming, the demand for energy-efficient devices with a reduction in carbon increases. The development of third-generation semiconductors, including GaN on Si [53–58] or silicon carbide (SiC) [28,59–63], has been a focus of research for more than 20 years. Among these materials, GaN on Si has emerged as a promising alternative to SiC due to its lower cost and CMOS process compatibility [64–69]. Despite this advantage, the epitaxy of GaN on Si remains challenging due to the lattice mismatch and thermal expansion coefficient differences between the two materials.

Nonetheless, a few companies, such as TSMC [70,71] and Panasonic [72–75], have successfully produced GaN on Si, while other companies, such as IMEC, have made significant progress in device performance by focusing on the device designs, such as integrating the optimized material for epi-stack [76]. Recently, IMEC reported achieving a device of GaN on Si that reached 1200 V [77–79], with performance comparable to that of SiC. The fabrication process involved the use of a CMOS-fab process-friendly method in 2022 [80,81]. However, it is worth noting that the production of SiC substrates remains a high-energy-consuming industry. The crystal growth furnace requires temperatures exceeding 2500 °C [76,82–86], and the epitaxy process demands temperatures exceeding 1500 °C [87–93].

Given these challenges, the development of more sustainable and efficient production processes for GaN on Si and other third-generation semiconductors becomes the most preferred task for the industry. This would help to further reduce the environmental impact of the semiconductor industry while also enhancing the economic viability of these materials. Ultimately, GaN on Si and SiC represent important developments in the field of semiconductors, offering a pathway to more energy-efficient and environmentally friendly electronic devices [94–98].

# 2. GaN Epitaxy

GaN epitaxy on Si (111) faces a problem related to the lattice mismatch between the substrate and the epitaxial layers [99–109]. This mismatch can result in a high density of threading dislocations and other defects, which can affect the performance of the final device. To mitigate this issue, various techniques, such as strain engineering, defect reduction, and the use of graded buffer layers, have been developed to reduce the number of dislocations and improve the quality of the epitaxial layers. Moreover, the thermal management of the GaN on the Si substrate was another critical factor that needs to be considered during epitaxial growth. The high thermal conductivity of Si can cause significant thermal stress on the GaN epitaxial layer, which can result in cracking and other defects. Therefore, appropriate thermal management techniques such as the use of thermal interface materials, optimized structure design, and the integration of heat sinks need to be implemented to ensure the reliability and long-term performance of the device.

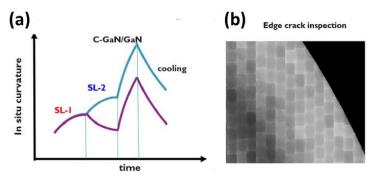

The Qromis Substrate Technology (QST) substrate structure was designed specifically for epitaxial growth and was characterized by a coefficient of thermal expansion (CTE) that was closely matched to the epitaxial layers grown on it. The substrate was composed of several layers, including a polycrystalline ceramic core that provided structural support, a first adhesion layer coupled to the core, a conductive layer coupled to the first adhesion layer, a second adhesion layer coupled to the conductive layer, and a barrier layer coupled to the second adhesion layer. In addition to these layers, the substrate also included a silicon oxide layer coupled to the support structure, which was then followed by a substantially single crystalline silicon layer. Finally, an epitaxial III–V layer was coupled to the single crystalline silicon layer. Overall, the QST substrate structure was designed to provide a stable and reliable foundation for epitaxial growth while also allowing for the use of a variety of semiconductor processing techniques [110]. An example of this would be the growth of thicker buffer layers on QST substrates [100,111,112], which requires the introduction of tensile stress to limit the increase in in-situ curvature. Figure 1 illustrates the improvement in curvature by introducing the alternate compressive and tensile stresses. QST substrates could be used for growing epitaxial thin films of various materials, such as nitrides, phosphides, arsenides, and other semiconductor materials. The characteristic of QST substrates was that their surfaces were very smooth with low defect density, which could provide high-quality surfaces that facilitated the growth and manufacturing of epitaxial thin films. In addition, the lattice matching of QST substrates could improve the crystal quality and lattice defect density of epitaxial thin films. QST substrates also had high transparency and optical performance, making them an ideal substrate for manufacturing high-quality optoelectronic devices.

**Figure 1.** (a). Conceptual representation of stepped superlattice and reversed stepped superlattice. (b) CAMTEK edge inspection (the square pattern on the wafer is due to stitching of measurement shots) [81]. Figure reproduced with permission from AIP Publishing Applied Physics Letters.

To overcome the challenges posed by the mismatch in CTE between Si and (Al)GaN, which affected the mechanical strength of wafers during the epitaxial growth of buffers, additional measures were taken. High-quality (Al)GaN buffers could be grown on Si substrates, but the CTE mismatch put a limit on the buffer quality, thickness, and substrate

size. One approach that was tried was to use substrates with nonstandard thickness, such as 1150 µm in our GaN-on-Si technology, for GaN growth on 200 mm Si substrates. However, this was not a scalable solution. A more practical solution was to use commercially available SEMI standard thickness engineered substrates, such as QST<sup>®</sup>, which had a CTE-matched poly-AIN core to the (Al)GaN buffer and good thermal conductivity. These substrates demonstrated extraordinary properties, including high crystal quality, abundant buffer thickness (>15  $\mu$ m), high thermal conductivity, and scalability potential to large diameter (12 inches). By using such substrates, the limitations posed by the CTE mismatch and the mechanical strength issues during epitaxial growth of buffers were overcome, enabling highquality (Al)GaN growth on Si substrates with improved mechanical and thermal properties. In summary, QST substrates are high-quality, high-performance substrates used for growing epitaxial thin films of various materials, including nitrides, phosphides, arsenides, and other semiconductor materials. Figure 1 illustrates that this can be accomplished by introducing alternate compressive and tensile stresses. However, this alone was not enough, as the strain partition effect will continue to be the primary impediment to the growth of thicker buffers for high-voltage applications. Traditional buffer technology that uses stepped superlattices [113–116] (SLs)—specifically, SL-1 > SL-2 (as indicated by the blue line in Figure 1)—relies on the gradual accumulation of compressive stress, which causes significant curvature in the QST substrates during growth. As a result, to achieve the growth of thicker buffers on QST substrates, the introduction of tensile stress was necessary to restrict in situ curvature buildup. This can be accomplished by alternating compressive and tensile stress in SL-1 < SL-2 (as shown by the purple line in Figure 1). Additionally, a reverse SL can be stacked to optimize the ex-situ wafer bow.

Furthermore, the interface between the GaN epitaxial layer and the Si substrate can also affect the performance of the device. The interfacial properties, such as the interface roughness, oxide layer thickness, and defect density, can have a significant impact on the electrical and optical properties of the device. Thus, the optimization of the interfacial properties is critical for achieving high-performance GaN on Si devices. In summary, the epitaxial growth of GaN on Si faces various challenges related to buffer layer design, defects, thermal management, and interfacial properties. Solving these challenges requires careful consideration of multiple factors and the implementation of appropriate techniques to ensure high-quality devices with reliable performance.

After the epitaxy process, the quality of the epitaxial layer was evaluated through the measurements of PL, XRD, AFM, and surface scans (surfscan). The information obtained from these measurements was used to optimize the epitaxial structure and refine the MOCVD recipe for subsequent epitaxy runs [117–120]. If any surface defect cracks were found on the wafer, further investigations were carried out to identify the cause and improve the quality of the epitaxial layer.

To improve the issue of gallium on Si substrate in contact resulting in melt-back etching, a nucleation layer of GaN or AlN can be adopted as an interface layer. However, due to limitations in the growth process, only an AlN nucleation layer (NL) can be selected in practice. The surface morphology and presence of unintentional oxygen impurities govern the vertical leakage of AlN NL/Si [121–126]. Interestingly, the AlN NL influences the growth of subsequent epitaxial layers as well as their vertical breakdown voltage. Further, it was found that the AlGaN intermediate layer and multi-pairs of AlGaN/AlN strained layer superlattice grown over AlN NL with better surface properties enhance the vertical breakdown voltage. Before applying the AlN nucleation layer, surface treatments such as spraying some aluminum or NH<sub>3</sub> can be employed to create a rough SiN<sub>x</sub> surface. This helps to militate the lattice mismatch-induced stress between the Si substrate and GaN lattice, which could otherwise lead to cracks and curvature in the epitaxial layer.

To further mitigate this issue, graduated buffer layers with a decreasing aluminum concentration were used, and a stepped gradient layer of  $Al_xGa_{1-x}N$  is typically used instead of a linear gradient layer. Additionally, superlattice or interrupted layers of AlN can be inserted to enhance the crystal quality of the epitaxial layer. The carbon-GaN layer

was also critical for the performance of the device due to its high insulator characteristic, as it determines the breakdown voltage and leakage [127]. Therefore, achieving uniformity in carbon doping was essential. Several options for carbon doping were available, including  $CH_4$ ,  $C_2H_4$ ,  $C_3H_8$ , and  $CBr_4$ . Some of the literature also suggests the use of Fe doping, which can improve the electrical conductivity of the epitaxial layer.

In 2020, IMEC planned to utilize 200 mm 8-inch QST substrate technology to grow GaN on silicon [128,129], which is a promising development for the electronics industry. This technology offers several benefits over traditional substrates, including reduced parasitic effects, a thermal expansion coefficient of AlN that matches the substrate, high thermal conductivity, high mechanical yield, and the capability to grow thick GaN buffer layers. These advantages enable the achievement of a high breakdown voltage of 650 V, which is essential for high-power devices.

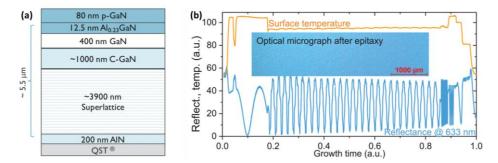

To achieve this breakdown voltage, a layer of 200 nm AlN is grown at high temperatures on QST, followed by the growth of a 3900 nm superlattice structure, as shown in Figure 2, at a lower temperature. This structure functions as a template for the subsequent growth of GaN layers. Next, 1000 nm carbon-doped GaN is grown at the same temperature, followed by 400 nm of GaN. Finally, 12.5 nm of aluminum nitride was grown at high temperatures, and 80 nm of Mg-doped GaN was grown by cooling. In the context of growing Mg-doped GaN by cooling typically meant that the growth process involved a technique known as epitaxial lateral overgrowth (ELO) or lateral epitaxial overgrowth (LEO). During this process, a thin layer of GaN was first deposited on a substrate. Then, a mask was applied to the surface of the GaN layer, leaving only small openings for the growth of GaN crystals. When additional GaN material was deposited over the mask, the crystals that grew through the openings started to merge and form a continuous layer. The key aspect of ELO/LEO was that during the growth process, the temperature was lowered to a point where GaN crystals could only grow laterally over the substrate rather than growing vertically. This allowed for a more controlled and precise growth of the Mg-doped GaN layer, as it prevented the formation of defects and impurities that could arise during the traditional vertical growth process. Therefore, by cooling in this context referred to the use of ELO/LEO to grow a high-quality and uniform layer of Mg-doped GaN by controlling the temperature during the growth process. This sequential layer growth process enables the creation of a high-quality and high-performance GaN on Si HEMT.

**Figure 2.** (a) Schematic cross-section of the epitaxial layer stack and (b) in-situ data of the surface temperature and the reflectance. The inset shows an optical micrograph of the surface after the epitaxial growth [128]. Figure reproduced with permission from IEEE Transactions on Semiconductor Manufacturing.

The high voltage power HEMT market demand electrical characteristic of the resulting device was impressive, with a breakdown voltage greater than 650 V and a low leakage current of 10  $\mu$ A/mm<sup>2</sup> for GaN HEMT with 36 mm of gate width (W<sub>G</sub>) and 16  $\mu$ m of gate-to-drain distance [128]. Figure 2 device has a high threshold voltage of about 3.1 V and a low off-state drain leakage of less than 1  $\mu$ A/mm. The horizontal trench isolation breakdown voltage exceeds 650 V, which indicates the high reliability and robustness of the device. Additionally, the device dispersion was well controlled to within 20% over high

and low temperature and bias voltage ranges, which ensures consistent performance over a wide range of operating conditions. Overall, the use of QST technology to grow GaN on Si holds great promise for the development of more efficient and high-performance electronic devices. The combination of high breakdown voltage, low leakage current, and well-controlled dispersion makes this technology an attractive option for power electronics, high-speed communications, and other demanding applications [130].

In recent years, the development of high-breakdown voltage epitaxial structures has been a major focus in the field of GaN power electronics. In 2020, IMEC achieved a significant milestone by developing an epitaxial structure with a breakdown voltage of 650 V. Building on this success, in 2022, they were able to increase the breakdown voltage to 1200 V by using the 200 mm QST substrate, showcasing the potential of complex epitaxial material stacks and QST substrates for high-voltage power applications such as electric vehicles. To achieve high breakdown voltage, the coefficient of thermal expansion (CTE) of the poly-AlN substrate is a crucial factor [81,131]. IMEC has carefully designed the poly-AlN substrate to closely match the CTE of the GaN/AlGaN epitaxial layer, enabling thicker epitaxial structures to be grown on large diameter substrates while maintaining the mechanical strength of the substrate and achieving higher voltage operation.

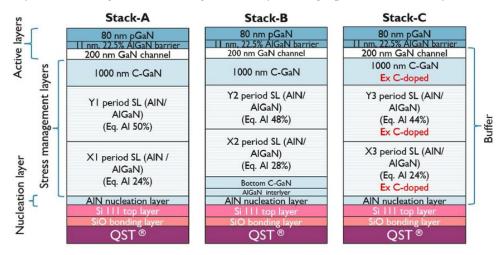

Besides the structural improvements, IMEC has also made significant advancements in its MOCVD technology. They have replaced the vertical Veeco MOCVD with the AIX-TRON horizontal MOCVD [132,133], leading to improved epitaxial structures, as shown in Figure 3. IMEC has also experimented with different epitaxial structures using reversed stepped superlattice (RSSL) inverted stepped superlattice structures, achieving higher vertical breakdown voltage >1200, as shown in Figure 4a–c. IMECs research and development efforts have made significant contributions to the field of GaN power electronics. Furthermore, they have collaborated with leading semiconductor companies to develop commercial-grade GaN-based power electronics for various applications, which has further accelerated the adoption of GaN-based power electronics in the market. The success of IMECs research and development in GaN-based power electronics is expected to pave the way for the next generation of high-efficiency and high-power electronic systems.

**Figure 3.** HEMT stacks based on intrinsic (stack A and stack B) and extrinsic (stack C) C-doping developed in this study. Buffer thicknesses of stack A and stack B vary from 5.3–7.4 to 4.8–6.1  $\mu$ m, respectively. Stack C has a thickness of ~6.8  $\mu$ m [81]. Figure reproduced with permission from AIP Publishing Applied Physics Letters.

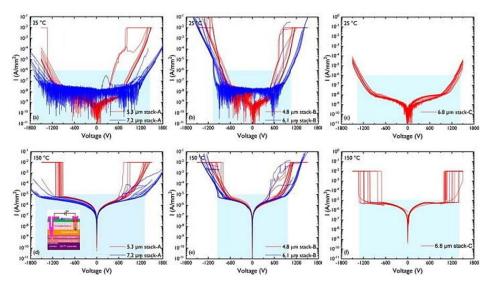

**Figure 4.** Vertical buffer leakage measurements for intrinsic C-doped (**a**,**d**) stack A (5.3  $\mu$ m vs. 7.2  $\mu$ m), (**b**,**e**) stack B (4.8 vs. 6.1  $\mu$ m), and (**c**,**f**) stack C (6.8  $\mu$ m) at 25 and 150 °C [81]. Figure reproduced with permission from AIP Publishing Applied Physics Letters.

The breakdown voltage of GaN HEMT was an important parameter that determined their reliability and performance. The critical electric field of AlN was higher than that of GaN, making it necessary to increase the Al percentage in the superlattice region to achieve high breakdown voltage. Additionally, the optimization of carbon concentration was crucial in achieving high breakdown voltage. Carbon doping can be performed through external sources such as ethylene or by tuning epitaxy parameters that affect crystal quality [134–136].

In this chapter, we also explore another way to increase breakdown voltage, which was to reduce the critical electric field at the AlN/Si interface by increasing the thickness of the buffer layer. There were different structural concepts and optimized Figure 4a–c to achieve a target vertical breakdown voltage of at least 1200 V. Design grow stress relief layers with varying thicknesses for structures A, B, and C and evaluate their breakdown voltage under high and low-temperature conditions [81].

Results demonstrate that the epitaxial structure plays a significant role in determining the collapse voltage of GaN HEMT. The doping of carbon was the main factor that affected breakdown voltage. It found that the breakdown voltage of structures A and C exceeds 1200 V, while structure B did not reach 1200 V for both thicknesses tested. Moreover, the thickness of structure C was less than that of structure A, but its breakdown voltage at high and low temperatures exceeds 1300 V. These results emphasize the importance of optimizing the epitaxy structure and carbon doping concentration for achieving high breakdown voltage in the GaN HEMT.

In the field of epitaxial growth of GaN, it is essential to ensure the quality of the surface since it affects the subsequent processes and the final characteristics of the components. Therefore, the surface inspection was critical in ensuring the quality of the epitaxial layer. OM was commonly used to check the surface of the substrate and epitaxial layer for visible cracks and roughness. AFM was a high-resolution technique used to detect surface roughness and morphology at the nanoscale level. PL was a non-destructive technique used to evaluate the quality of the epitaxial layer by measuring its optical properties. XRD is a powerful technique that can provide information about the crystal quality, thickness, and strain of the epitaxial layer.

In addition to these techniques, TEM can also be used to investigate the structural defects in the epitaxial layer at the atomic level. It can provide detailed information about the crystal structure, defects, and dislocations, which are critical for determining the quality of the epitaxial layer. Apart from the above-mentioned techniques, KLA Corporation's

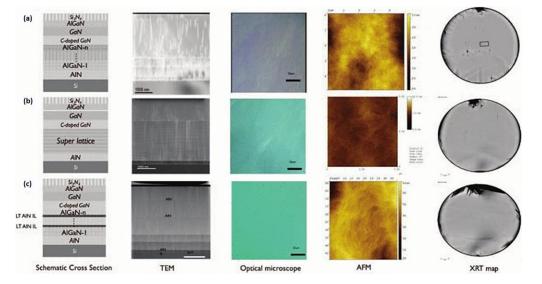

product of surface scan is another widely used method to detect surface defects and particles [137]. It was a non-contact, high-resolution technique that can detect surface defects such as scratches, pits, and particles that are smaller than the wavelength of light. In conclusion, the inspection of the surface quality of the epitaxial layer is crucial for ensuring the quality of the final components. The use of various surface inspection techniques such as OM, AFM, PL, XRD, TEM, and KLA Corporation's surface scan provides critical information about the quality of the epitaxial layer and helps in improving the process and component performance. Three typical substrate architectures in Figure 5a have been individually optimized for epi-quality and electrical performance. A step-graded buffer uses, on top of an AlN nucleation layer, several AlGaN layers with decreasing Al content in steps. A superlattice buffer Figure 5b consists of N pairs of strained AlN/(Al)GaN layers. This allows for the growth of thicker buffers while keeping the overall wafer bow below 50 µm. Increasing the (Al)GaN buffer thickness increases the achievable breakdown voltage. Increasing the thickness of the GaN buffer using a step-graded approach, however, increases the in-film stress resulting in a high density of slip lines, high wafer bow, and possibly film and wafer cracking. Therefore, thin low-temperature AlN interlayers Figure 5c can be inserted in a step-graded type of buffer to minimize the internal stress during growth and post-growth cool down, thus achieving thicker layers [138].

**Figure 5.** Schematic cross-section (not to scale), TEM, optical microscope, AFM, and X-ray topography map (XRT) of (**a**) stepped buffer, (**b**) superlattice, and (**c**) low-temperature AIN interlayer. Both the superlattice and interlayer approaches reduce the density of slip lines and cracks significantly with respect to the step-graded buffer approach [138]. Figure reproduced with permission from IEEE Proceedings.

### 3. GaN Process

On the other hand, depletion-mode (D-mode) devices have been developed as an alternative solution to overcome the limitations of power switching capability in Si-related devices. D-mode devices can be fabricated using a self-aligned process and offer several advantages, including a simple fabrication process, low off-state leakage current, and high stability. These advantages made D-mode devices suitable for power-switching applications, particularly for fast switching speed and high-current operations. In recent years, significant progress has been made in the development of GaN-based enhancement-mode (E-mode) and D-mode devices, particularly in terms of their performance, reliability, and scalability. However, several challenges still need to be improved, including the optimization of the key material selection, device structure design, and process precise control. This article aims to provide an overview of the GaN process' current state, including the remaining challenges and opportunities for GaN development and the future prospects

for GaN-based E-mode and D-mode devices, focusing on their performance, reliability, and scalability [139–141].

One of the key features of GaN-based devices was their ability to operate in the Dmode, which was attributed to the unique material properties of the two-dimensional electron gas (2DEG) in AlGaN/GaN. Furthermore, E-mode devices have been extensively studied and developed for their ability to offer high performance, low R<sub>ON</sub>, and low dynamic power consumption. However, the fabrication of E-mode devices requires precise control of the doping process in the gate structure, which has several challenges, such as the high gate leakage current and poor stability under high temperature and high voltage conditions.

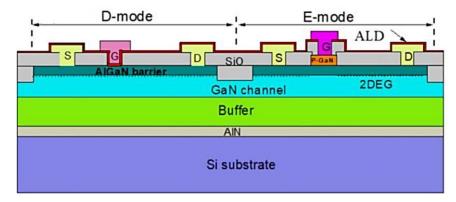

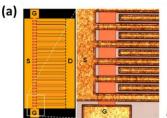

An AlGaN/GaN of E-mode and D-mode HEMT combined inverter, as shown in Figure 6, utilizing p-GaN gate technology on a 150 mm silicon wafer. The key difference between an E/D mode GaN inverter and other conventional inverters lies in the use of a p-GaN epitaxial layer on a 150 mm silicon substrate, which was fabricated on a p-GaN gate/AlGaN/GaN. The epitaxial layer is grown using the MOCVD technique. It includes a 200 nm AlN nucleation layer, a high-resistance buffer layer of about 3.5  $\mu$ m, an undoped GaN channel layer of about 300 nm, and an Al<sub>0.13</sub>Ga<sub>0.87</sub>N barrier layer of about 18 nm. These layers were sequentially grown on the silicon substrate to form the epitaxial structure. To complete the fabrication process, a p-type GaN layer of about 90 nm was grown with an Mg concentration of about  $10^{19}$  cm<sup>-3</sup>. The entire structure was then annealed at 650 °C for 15 min in the MOCVD. This process helps to activate the Mg dopants and enhance the electrical properties of the device [142].

**Figure 6.** Schematic cross-section of E/D-mode GaN monolithic integration technology Adapted with permission from [142].

After the epitaxial growth and annealing, the process continues with device fabrication steps. First, mesa isolation was performed using standard photolithography and dry etching techniques [143,144]. After performing mesa isolation using standard photolithography and dry etching techniques, surface leakage problems may have occurred. Surface leakage refers to the phenomenon where current flowed along the surface of the mesa, rather than through the desired pathway. This could have led to reduced device performance or failure. One possible cause of surface leakage was the presence of residual etching material on the mesa surface which could have created a conductive path. This could have been mitigated by thoroughly cleaning the mesa surface after etching, using techniques such as plasma cleaning or wet chemical cleaning. Another possible cause of surface leakage was the formation of surface defects during the etching process. These defects could have acted as trap sites for charge carriers, allowing them to bypass the intended pathway. To minimize surface defects, it was important to optimize the etching conditions, such as gas composition, pressure, and power. In addition, proper mesa passivation could have also helped to reduce surface leakage. Passivation referred to the process of coating the mesa surface with a thin layer of insulating material, such as silicon dioxide or silicon nitride. This layer could have helped to block surface currents and reduce the likelihood of surface

defects. Overall, careful attention to cleaning, etching conditions, and passivation could have helped to minimize surface leakage problems after dry etching mesa isolation. Then, the ohmic contacts were formed by depositing a Ti/Al/Ni/Au metal stack [145–147] and annealing at 850 °C for 30 s [148–150]. Next, the p-GaN gate was formed by depositing the Ni/Au metal stack and annealing at 500–800 °C [151–153]. Finally, the passivation layer was deposited to protect the device from environmental affecting. In the summary, the AlGaN/GaN E/D mode HEMT combined inverter using p-GaN gate technology on a 150 mm silicon wafer was successfully fabricated. The process involves the growth of the p-GaN epitaxial layer on a 150 mm silicon substrate, followed by device fabrication steps, including mesa isolation, ohmic contact formation, p-GaN gate formation, and passivation. The resulting device exhibits excellent electrical properties and can be utilized in various applications, such as power electronics and high-frequency circuit-based devices [154].

#### 4. Gold-Free COMS-Compatible GaN Technology

The compatibility of GaN technology with complementary metal-oxide-semiconductor (CMOS) processes has been a long-standing challenge in the semiconductor industry. The demand for high-speed, high-power, and high-temperature electronic devices has driven the development of GaN-based technology. However, the integration of GaN devices with conventional CMOS processes has been limited due to the incompatibility of the materials and fabrication processes. To improve this issue, researchers have developed various CMOS-compatible GaN fabrication methods, including the use of Si substrates and Si-based materials. The use of Si substrates has several advantages, including low cost, large area, and well-established CMOS processing techniques. However, the lattice mismatch between Si and GaN results in high defect density and poor crystalline quality, which leads to low device performance [64–69].

To overcome these challenges, researchers have developed new techniques, such as the epitaxial lateral overgrowth (ELOG) of GaN on Si substrate. ELOG is a promising technique that allows the growth of high-quality GaN thin film on Si substrate by reducing the defect density and enhancing the crystalline quality of the GaN thin film. Another promising approach was the use of a strained Si substrate, which can reduce the lattice mismatch and improve the GaN crystal quality. Moreover, the development of CMOS-compatible GaN-based technology also involves the optimization of the process steps, such as the growth of high-quality GaN thin film, the formation of ohmic contact, and the integration of GaN devices with CMOS circuits. These steps require careful control of the growth conditions, surface treatment, and device processing, as well as the development of new materials and fabrication techniques.

In recent years, significant progress has been made in CMOS-compatible GaN technology, with several successful demonstrations of GaN-based power devices integrated with CMOS circuits. These devices have shown promising performance, including high breakdown voltage, low R<sub>ON</sub>, and fast switching speed. The development of CMOS-compatible GaN technology was expected to enable the integration of high-performance GaN devices with CMOS circuits for a wide range of applications, such as power electronics, RF communications, and optoelectronics.

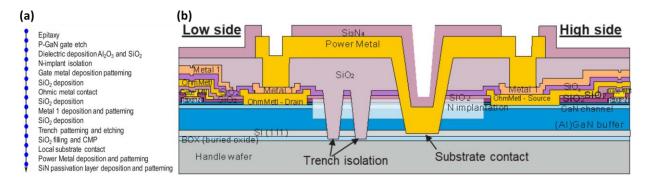

This section focuses on the fabrication of a nitride-based semiconductor device using a CMOS-compatible process. The process was performed using a 200 mm CMOS-compatible process from IMEC, as shown in Figure 7a. The process involves depositing the TiN layer on the p-GaN layer and then etching it using a dry etch. This was followed by a selective dry etch from the p-GaN layer to the AlGaN layer using  $BCl_3/SF_6$ . The gate was then defined by laterally etching the TiN metal layer. This technique significantly suppresses leakage through the gate sidewall and improves the gate reliability. Afterward, dielectric layers using  $Al_2O_3$  and  $SiO_2$  were deposited in defined areas, and nitrogen ion implantation was performed for lateral isolation. The dielectric layer was then etched away in the gate area, and then the gate metal layer was deposited and patterned.

**Figure 7.** (a) Schematic cross-section of the epitaxial layer stack and process integration flow. (b) Schematic cross-section of the integrated half-bridge, trench isolation, and local substrate contact [128]. Figure reproduced with permission from IEEE Transactions on Semiconductor Manufacturing.

Following the gate treatment, the ohmic contact metal layer of the source and drain was plated using a metal stack composed of Ti, Al, Ti, and TiN. The metal stack was then annealed at a low temperature. Trench isolation was formed by etching the dielectric AlGaN buffer layer down to the Si (111) layer [121,155], stopping at the SiO<sub>2</sub> buried oxide layer. Chemical mechanical polishing (CMP) with SiO<sub>2</sub> filling was then performed [156–158]. Through etch to the substrate, rear metallization and SiN passivation protection layer are added to the device. Finally, the entire component manufacturing process is completed, as shown in Figure 7b. The CMOS-compatible process used in this paper provides a promising pathway for the integration of nitride-based devices with mainstream CMOS technology, enabling the development of new and advanced electronic devices.

# 5. The Defect of GaN HEMT Device

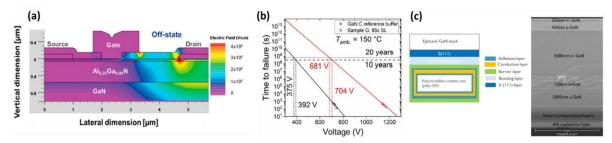

In this part, the focus is on the reliability and defects of GaN devices. As shown in the Figure 8a, the electric field formula of the E-mode element under high bias can lead to rapid shortening of the device life due to defects [159]. Therefore, in addition to improving the epitaxial design structure, there were several ways to enhance device reliability. Firstly, fluorine ion implantation can be used under the gate. Secondly, the metal-insulator-semiconductor (MIS) type gate design can be employed. Thirdly, the high voltage GaN HEMT can be connected to the low voltage silicon MOSFET. Fourthly, a p-GaN or p-AlGaN layer can be added to the AlGaN/GaN HEMT structure.

**Figure 8.** (a) A simulated electric field in a GaN high electron mobility transistor (HEMT) in off-state, with a drain bias of 300 V. (b) TTF (Weibull scale factor, 63.2% failure) dependence on the drain voltage along with lifetime extrapolations comparing the reference GaN:C and AlGaN/AlN superlattice buffer. (c) Schematic image of QST<sup>®</sup> engineered substrates with poly-AlN core (with epitaxial GaN stack on top), and cross-sectional SEM image of a vertical device stack with a total GaN thickness of 5.4 µm on 200 mm engineered substrates [159–161]. Figure reproduced with permission from IEEE Transactions on Electron Devices and Elsevier Microelectronics Reliability.

Figure 8b shows the time to failure (TTF) study by IMEC using QST substrates with a breakdown voltage of about 200 V [160]. However, no carbon doping was added to the

buffer layer, leading to reduced reliability. In contrast, the 2020 Aixtron paper sponsored by Bayerische Motoren Werke (BMW) changed from the general carbon-doped stepped buffer layer to 85 pairs of the carbon-doped superlattice, as can be seen in Figure 8b. This change has effectively doubled the device's lifetime. Therefore, the design of the epitaxial structure changes is critical not only for improving component characteristics but also for enhancing device reliability [161].

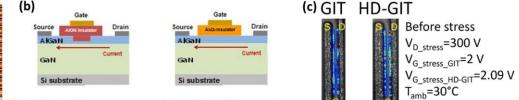

On reliability and defects of GaN technology presents various approaches to improve the performance and reliability of the components. One of the strategies discussed the use of is the Panasonic HD-GITs Plus field version [162], which has been shown to effectively improve dynamic  $R_{ON}$ . In 2012, IMEC designed an 8-inch Si substrate with a gold-free CMOS component design, which had a breakdown voltage of about 300 V. This design used the three-layer field plate to improve dynamic  $R_{ON}$ . Compared with components using a one-layer field plate and a three-layer field plate, the normalized on-resistance dropped from 3.7 to 1.7 on average. Not only can a well-designed source and gate fieldplate configuration reduce the magnitude of the electric field between the drain and source, but it can also constrain the trapping region by regulating the location of the electric field maxima [163]. In 2018, Panasonic introduced the Hybrid-Drain-embedded GITs (HD-GITs), which used the previously mentioned MIS structure and had a breakdown voltage of up to 730 V and a drain current of up to 20 A [66].

Figure 9 illustrates the distribution of the electric field in the HD-GITs. The electroluminescence signal peak was divided into the following two regions: the drain-side edge of the gate and the drain. These were the channels where the electric field was the strongest. The HD-GITs have demonstrated no-current collapse up to 1 kV. The trapping mechanism responsible for the current collapse was investigated in GITs and HD-GITs, combining pulse measurements, transient investigations, and electroluminescence characteristics under off-state and half-on conditions. To improve current collapse, the p-type drain was introduced in HD-GITs to help inject holes in closed and half-open states. The results showed that the traps filled in the closed state and the half-open condition were the same, with an activation energy (Ea = 0.8 eV) consistent with the displacement of carbon defects.

AION MIS GaN (New technology) AI2O3 MIS GaN (Conventional)

**Figure 9.** (a) Layout (left) and microscope picture detail (right) of a 60 mm gate width power device. (b) AlON MIS GaN (new tech.), and Al<sub>2</sub>O = MIS GaN (conventional). (c) A false color profile is taken after the application of  $V_D$  = 300 V,  $V_G\_GIT$  = 2 V, and  $V_G\_HD\_GIT$  = 2.09 V. Under semi-ON conditions, the luminescence is localized at the drain side of the gate and at the drain contact both in the GIT and in the HD\\_GIT [66,162,164]. Figure reproduced with permission from IEEE Proceedings.

The dynamic R<sub>ON</sub> variation under half-on conditions, such as pulsed and transient measurements, was found to be different between GITs and HD-GITs. The faster demolding speeds in HD-GITs led to improved pulse measurements during the current collapse and reduced drain edge (semiconducting luminescence under constant voltage stress) conditions. Overall, the Panasonic HD-GITs Plus field version has shown great promise in improving dynamic R<sub>ON</sub> and reducing current collapse, thereby enhancing the reliability of gallium nitride technology [164].

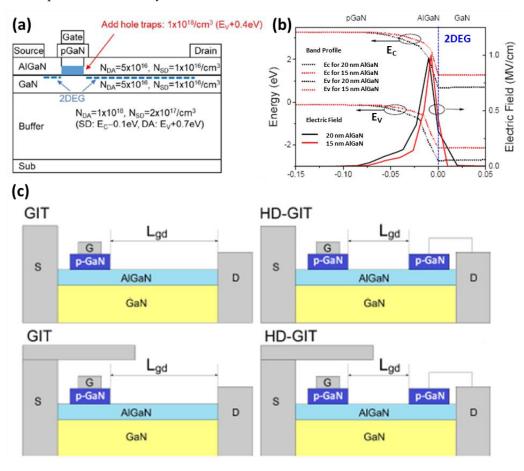

In 2019, Panasonic conducted research on the electric field of different thicknesses of AlGaN in the E-mode. Figure 10a,b the results of this study [165]. The electric field distribution in the AlGaN layer can be improved by reducing the thickness of the AlGaN layer. This helps to reduce the electric field peak, which can improve the reliability and

lifetime of the device. In addition, Panasonic also conducted research on the HD-GITs (Hybrid-Drain-embedded GITs) plus field version in 2019. Figure 10c The HD-GITs plus field version can effectively improve the dynamic R<sub>ON</sub> of the device [164]. This is achieved by introducing a drain layer in the HD-GITs, which helps to inject holes in closed and half-open states, and thus improves current collapse. The trapping mechanism responsible for the current collapse was also investigated in GITs and HD-GITs, which helps to understand and improve the reliability and lifetime of the device.

**Figure 10.** (a) Schematic cross-section of gate injection transistor (GIT). The densities and levels of traps employed in simulation in this study are also presented. (b) Energy band profiles underneath the pGaN gate simulated for the GIT with a thinner (15-nm-thick) AlGaN (larger  $V_{TH}$ ) and a thicker (20-nm-thick) AlGaN barrier (smaller  $V_{TH}$ ). (c) Schematic cross sections of a gate injection transistor (GIT) and a hybrid-drain-embedded GIT (HD-GIT) without and with the field plate [164,165]. Figure reproduced with permission from IEEE Proceedings.

The research also found that the variation between GITs and HD-GITs is the dynamic R<sub>ON</sub> variation under half-on conditions, such as pulsed and transient measurements. The faster demolding speeds in HD-GITs lead to improved pulse measurements during the current collapse and reduced drain edge conditions. Furthermore, the study found that the traps filled in the closed state and the half-open condition are the same, with activation energy consistent with the displacement of carbon defects. These findings provide valuable insights into the design and optimization of the epitaxial structure for improving the reliability and lifetime of GaN-based devices.

In 2015, Infineon conducted a study on the effect of measurement setup on pulsed I–V measurements, focusing on  $I_{DS}(t)$  waveform to ensure the accuracy of the measurement. The study found that  $R_{ON}$  was insensitive to short transients, below 10 µs, in both the fresh and accelerated bias aging test (HTRB) aged devices. However, the  $R_{ON}$  doubled in shutdown when increasing  $V_{DS0}$  from 0 V to 50 V. Moreover, the threshold voltage

$V_{TH}$  of the aged device in the HTRB aging test, which was conducted for 2200 h, showed comparable trapping effects that led to an increase in  $R_{ON}$ , particularly under the gate-source and drain-source access areas.

In 2015, On-semi and IMEC studied the use of ion implantation as an effective and controllable way to reduce the dynamic Ron. The effects were evaluated by combining pulse characterization, transient measurements, and electroluminescence analysis on untreated and irradiated devices. The study found that ion implantation led to an increase in electroluminescence signal and a decrease in dynamic R<sub>ON</sub> post-implantation, which was attributed to the reduction of leakage in the u-GaN layer and the facilitation of charge release from the buffer layer. Notably, no trap level state  $(1.5 \times 10^{14} \text{ ions/cm}^2)$  was detected after ion implantation. When a semiconductor material is implanted with ions, it can lead to the creation of defects in the lattice structure of the material, which can act as trapping centers for charge carriers. These trapping centers can affect the electrical properties of the material, such as its carrier mobility, lifetime, and resistance. In this case, the ion implantation was performed in such a way that the defects created in the lattice structure of the material did not act as trapping centers for charge carriers. This was likely achieved by optimizing the implantation conditions, such as the energy and dose of the implanted ions, to ensure that the created defects were either electrically neutral or did not significantly affect the electrical properties of the material. Furthermore, the study mentions that the ion implantation led to an increase in electroluminescence signal and a decrease in dynamic R<sub>ON</sub>, which suggests that the created defects did not have a significant impact on the material's electrical properties. Therefore, it is reasonable to conclude that no trap level state was detected after ion implantation because the created defects did not act as trapping centers for charge carriers.

The characterization of low-frequency noise (LFN) in electronic devices at cryogenic temperatures became an active research area. For instance, researchers examined shot noise in short-channel MOSFETs, white noise in NMOS technology, and the microwave noise figure of InP HEMT under cryogenic conditions. The LFN level of devices was considered a crucial parameter in cryogenic electronic systems as it contributed significantly to the transistor's comprehensive noise, especially given that both thermal and shot noise decreased at cryogenic temperatures. Additionally, LFN measurements could assess the defect states in devices and their reliability. Although various studies investigated the behavior and origins of LFN in Si-based and GaAs/InP-based cryogenic systems, few studies examined the LFN characteristics of GaN HEMTs in the cryogenic environment, particularly at extremely low temperatures down to 4.2 K.

To address this gap, we conducted a comprehensive study of the DC and LFN behavior of GaN-based HEMTs across a temperature range from 300 K to 4.2 K. As the temperature decreased, we observed an overall improvement in the devices' electrical performance, with a 75% increase in maximum IDS ( $I_{DS,max}$ ), steeper SS, suppressed leakage current by an order of magnitude, and decreased R<sub>ON</sub>. These improvements were attributed to the suppressed lattice scattering and enhanced carrier mobility under cryogenic conditions. Additionally, the studies analyzed the LFN of the devices as a function of temperature, revealing a clear 1/f noise behavior. More importantly, we used the carrier number fluctuations with correlated mobility fluctuations (CNF/CMF) model to describe the origin and underlying physics of LFN down to 4.2 K. Research extracted and discussed the correlated parameters, i.e., flat-band voltage spectral density (Svfb) and trap density (Nt), which revealed the defect evolution in the GaN-based HEMTs under cryogenic temperatures. Overall, our work provided a thorough analysis of the DC and LFN characterizations of GaN HEMTs down to 4.2 K, offering insights for the design of future GaN-based cryodevices and systems [166].

#### 6. Conclusions

In conclusion, this review paper has highlighted the rapid progress and proposed improvements in GaN on Si epitaxy structure to achieve the high breakdown voltage and three-layer field plate to improve dynamic  $R_{ON}$ . IMECs use of the 200 mm, 8-inch QST substrate with GaN epitaxy architecture for high breakdown voltage has achieved significant breakthroughs, with the breakdown voltage reaching 650 V in 2020 and 1200 V in 2022 through the use of superlattice and carbon-doping techniques. The adoption of VEECO MOCVD and the three-layer field plate has also improved the process in GaN HEMT, resulting in the low dynamic  $R_{ON}$ . Furthermore, highlights a CMOS-fab compatible process, which provides a promising pathway for the integration of GaN devices with mainstream CMOS technology, thereby enabling the development of new and advanced electronic devices. Panasonic HD-GITs plus field version was also utilized to effectively improve dynamic  $R_{ON}$  in 2019. These improvements have led to enhanced reliability and  $R_{ON}$ , marking a significant milestone in the development of third-generation semiconductors with wide bandgap, particularly GaN on Si.

Author Contributions: Data curation, Y.-Y.L.; project administration, A.-P.C.; supervision, H.-C.C. and H.-C.K.; writing—original draft, A.-C.L.; writing—review and editing, all authors. All authors have read and agreed to the published version of the manuscript.

Funding: Ministry of Science and Technology, Taiwan (111-2218-E-008-005-).

Acknowledgments: The authors would like to thank the Semiconductor Research Center, Hon Hai Research Institute, for the helpful discussion.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

- 1. Pearton, S.J.; Abernathy, C.R.; Thaler, G.T.; Frazier, R.M.; Norton, D.P.; Ren, F. Wide bandgap GaN-based semiconductors for spintronics. *J. Phys. Condens. Matter* **2004**, *16*, R209–R245. [CrossRef]

- 2. Kaminski, N.; Hilt, O. SiC and GaN devices—Wide bandgap is not all the same. *IET Circuits Devices Syst.* **2014**, *8*, 227–236. [CrossRef]

- 3. Fujita, S. Wide-bandgap semiconductor materials: For their full bloom. Jpn. J. Appl. Phys. 2015, 54, 030101. [CrossRef]

- 4. Augustine Fletcher, A.S.; Nirmal, D.; Ajayan, J.; Arivazhagan, L. Analysis of AlGaN/GaN HEMT using discrete field plate technique for high power and high frequency applications. *AEU Int. J. Electron. Commun.* **2019**, *99*, 325–330. [CrossRef]

- Ueda, T.; Ishida, M.; Tanaka, T.; Ueda, D. GaN transistors on Si for switching and high-frequency applications. *Jpn. J. Appl. Phys.* 2014, 53, 100214. [CrossRef]

- Xu, J.; Gu, L.; Ye, Z.; Kargarrazi, S.; Rivas-Davila, J.M. Cascode GaN/SiC: A Wide-Bandgap Heterogenous Power Device for High-Frequency Applications. *IEEE Trans. Power Electron.* 2020, 35, 6340–6349. [CrossRef]

- Saadat, O.I.; Chung, J.W.; Piner, E.L.; Palacios, T. Gate-First AlGaN/GaN HEMT Technology for High-Frequency Applications. IEEE Electron Device Lett. 2009, 30, 1254–1256. [CrossRef]

- 8. Shur, M.S. GaN based transistors for high power applications1This paper was first published in the Material Research Society Symposium Proceedings, Symposium E, Fall, 1997.1. *Solid-State Electron.* **1998**, *42*, 2131–2138. [CrossRef]

- Trew, R.J.; Shin, M.W.; Gatto, V. High power applications for GaN-based devices. *Solid-State Electron.* 1997, 41, 1561–1567. [CrossRef]

- 10. Wasisto, H.S.; Prades, J.D.; Gülink, J.; Waag, A. Beyond solid-state lighting: Miniaturization, hybrid integration, and applications of GaN nano- and micro-LEDs. *Appl. Phys. Rev.* 2019, *6*, 041315. [CrossRef]

- 11. Koike, M.; Shibata, N.; Kato, H.; Takahashi, Y. Development of high efficiency GaN-based multiquantum-well light-emitting diodes and their applications. *IEEE J. Sel. Top. Quantum Electron.* **2002**, *8*, 271–277. [CrossRef]

- 12. Liu, Z.; Chong, W.C.; Wong, K.M.; Lau, K.M. GaN-based LED micro-displays for wearable applications. *Microelectron. Eng.* 2015, 148, 98–103. [CrossRef]

- Lee, S.Y.; Park, K.-I.; Huh, C.; Koo, M.; Yoo, H.G.; Kim, S.; Ah, C.S.; Sung, G.Y.; Lee, K.J. Water-resistant flexible GaN LED on a liquid crystal polymer substrate for implantable biomedical applications. *Nano Energy* 2012, 1, 145–151. [CrossRef]

- Disney, D.; Nie, H.; Edwards, A.; Bour, D.; Shah, H.; Kizilyalli, I.C. Vertical power diodes in bulk GaN. In Proceedings of the 2013 25th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Kanazawa, Japan, 26–30 May 2013; pp. 59–62.

- 15. Waltereit, P.; Bronner, W.; Quay, R.; Dammann, M.; Kiefer, R.; Pletschen, W.; Müller, S.; Aidam, R.; Menner, H.; Kirste, L.; et al. AlGaN/GaN epitaxy and technology. *Int. J. Microw. Wirel. Technol.* **2010**, *2*, 3–11. [CrossRef]

- Green, D.S.; Gibb, S.R.; Hosse, B.; Vetury, R.; Grider, D.E.; Smart, J.A. Control of epitaxial defects for optimal AlGaN/GaN HEMT performance and reliability. J. Cryst. Growth 2004, 272, 285–292. [CrossRef]

- 17. Kizilyalli, I.C.; Bui-Quang, P.; Disney, D.; Bhatia, H.; Aktas, O. Reliability studies of vertical GaN devices based on bulk GaN substrates. *Microelectron. Reliab.* **2015**, *55*, 1654–1661. [CrossRef]

- Zhang, D.; Cheng, X.; Ng, W.T.; Shen, L.; Zheng, L.; Wang, Q.; Qian, R.; Gu, Z.; Wu, D.; Zhou, W.; et al. Reliability Improvement of GaN Devices on Free-Standing GaN Substrates. *IEEE Trans. Electron Devices* 2018, 65, 3379–3387. [CrossRef]

- 19. Wuerfl, J.; Bahat-Treidel, E.; Brunner, F.; Cho, E.; Hilt, O.; Ivo, P.; Knauer, A.; Kurpas, P.; Lossy, R.; Schulz, M.; et al. Reliability issues of GaN based high voltage power devices. *Microelectron. Reliab.* **2011**, *51*, 1710–1716. [CrossRef]

- 20. Duffy, M.T.; Wang, C.C.; O'clock, G.D.; McFarlane, S.H.; Zanzucchi, P.J. Epitaxial growth and piezoelectric properties of A1N, GaN, and GaAs on sapphire or spinel. *J. Electron. Mater.* **1973**, *2*, 359–372. [CrossRef]

- 21. Yamaguchi, S.; Kariya, M.; Nitta, S.; Takeuchi, T.; Wetzel, C.; Amano, H.; Akasaki, I. Structural properties of InN on GaN grown by metalorganic vapor-phase epitaxy. *J. Appl. Phys.* **1999**, *85*, 7682–7688. [CrossRef]

- 22. Ohta, J.; Fujioka, H.; Oshima, M. Room-temperature epitaxial growth of GaN on conductive substrates. *Appl. Phys. Lett.* 2003, *83*, 3060–3062. [CrossRef]

- 23. Hughes, W.C. Molecular beam epitaxy growth and properties of GaN films on GaN/SiC substrates. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. 1995, 13, 1571. [CrossRef]

- Kosicki, B.B.; Kahng, D. Preparation and Structural Properties of GaN Thin Films. *J. Vac. Sci. Technol.* 1969, *6*, 593–596. [CrossRef]

Nahhas, A.; Kim, H.K.; Blachere, J. Epitaxial growth of ZnO films on Si substrates using an epitaxial GaN buffer. *Appl. Phys. Lett.*

- 2001, 78, 1511–1513. [CrossRef]

26. Paskova, T.; Evans, K.R. GaN Substrates—Progress, Status, and Prospects. *IEEE J. Sel. Top. Quantum Electron.* 2009, 15, 1041–1052. [CrossRef]

- 27. Ponce, F.A. Defects and Interfaces in GaN Epitaxy. MRS Bull. 1997, 22, 51–57. [CrossRef]

- Binari, S.C.; Klein, P.B.; Kazior, T.E. Trapping effects in GaN and SiC microwave FETs. *Proc. IEEE* 2002, *90*, 1048–1058. [CrossRef]

Alquier, D.; Bongiorno, C.; Roccaforte, F.; Raineri, V. Interaction between dislocations and He-implantation-induced voids in GaN epitaxial layers. *Appl. Phys. Lett.* 2005, *86*, 211911. [CrossRef]

- Mocanu, M.; Unger, C.; Pfost, M.; Waltereit, P.; Reiner, R. Thermal Stability and Failure Mechanism of Schottky Gate AlGaN/GaN HEMTs. *IEEE Trans. Electron Devices* 2017, 64, 848–855. [CrossRef]

- Unger, C.; Mocanul, M.; Pfost, M.; Waltereit, P.; Reiner, R. Experimental analysis of the gate-leakage-induced failure mechanism in GaN HEMTs. In Proceedings of the 2016 International Semiconductor Conference (CAS), Sinaia, Romania, 10–12 October 2016; pp. 127–130.

- 32. Cai, X.; Du, C.; Sun, Z.; Ye, R.; Liu, H.; Zhang, Y.; Duan, X.; Lu, H. Recent progress of physical failure analysis of GaN HEMTs. J. Semicond. 2021, 42, 051801. [CrossRef]

- 33. Owens, A.; Peacock, A. Compound semiconductor radiation detectors. *Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip.* **2004**, 531, 18–37. [CrossRef]

- Corrion, A.L.; Poblenz, C.; Wu, F.; Speck, J.S. Structural and morphological properties of GaN buffer layers grown by ammonia molecular beam epitaxy on SiC substrates for AlGaN/GaN high electron mobility transistors. J. Appl. Phys. 2008, 103, 093529. [CrossRef]

- 35. Xing, H.; Keller, S.; Wu, Y.F.; McCarthy, L.; Smorchkova, I.P.; Buttari, D.; Coffie, R.; Green, D.S.; Parish, G.; Heikman, S.; et al. Gallium nitride based transistors. *J. Phys. Condens. Matter* **2001**, *13*, 7139. [CrossRef]

- 36. Paskova, T.; Hanser, D.A.; Evans, K.R. GaN Substrates for III-Nitride Devices. Proc. IEEE 2010, 98, 1324–1338. [CrossRef]

- Huili, X.; Dora, Y.; Chini, A.; Heikman, S.; Keller, S.; Mishra, U.K. High breakdown voltage AlGaN-GaN HEMTs achieved by multiple field plates. *IEEE Electron Device Lett.* 2004, 25, 161–163. [CrossRef]

- Jena, K.; Swain, R.; Lenka, T.R. Impact of a drain field plate on the breakdown characteristics of AlInN/GaN MOSHEMT. J. Korean Phys. Soc. 2015, 67, 1592–1596. [CrossRef]

- Matys, M.; Ishida, T.; Nam, K.P.; Sakurai, H.; Narita, T.; Uesugi, T.; Bockowski, M.; Suda, J.; Kachi, T. Mg-implanted bevel edge termination structure for GaN power device applications. *Appl. Phys. Lett.* 2021, 118, 093502. [CrossRef]

- Dickerson, J.R.; Allerman, A.A.; Bryant, B.N.; Fischer, A.J.; King, M.P.; Moseley, M.W.; Armstrong, A.M.; Kaplar, R.J.; Kizilyalli, I.C.; Aktas, O.; et al. Vertical GaN Power Diodes With a Bilayer Edge Termination. *IEEE Trans. Electron Devices* 2016, 63, 419–425. [CrossRef]

- 41. Gallagher, J.C.; Ebrish, M.A.; Porter, M.A.; Jacobs, A.G.; Gunning, B.P.; Kaplar, R.J.; Hobart, K.D.; Anderson, T.J. Optimizing performance and yield of vertical GaN diodes using wafer scale optical techniques. *Sci. Rep.* **2022**, *12*, 658. [CrossRef]

- 42. Yue, Y.; Hao, Y.; Zhang, J.; Ni, J.; Mao, W.; Feng, Q.; Liu, L. AlGaN/GaN MOS-HEMT With HfO<sub>2</sub> Dielectric and Al<sub>2</sub>O<sub>3</sub> Interfacial Passivation Layer Grown by Atomic Layer Deposition. *IEEE Electron Device Lett.* **2008**, *29*, 838–840. [CrossRef]

- Gao, Z.; Romero, M.F.; Calle, F. Thermal and Electrical Stability Assessment of AlGaN/GaN Metal–Oxide–Semiconductor High-Electron Mobility Transistors (MOS-HEMTs) With HfO2 Gate Dielectric. *IEEE Trans. Electron Devices* 2018, 65, 3142–3148. [CrossRef]

- 44. He, J.; Wang, Q.; Zhou, G.; Li, W.; Jiang, Y.; Qiao, Z.; Tang, C.; Li, G.; Yu, H. Normally-OFF AlGaN/GaN MIS-HEMTs with Low RON and Vth Hysteresis by Functioning In-situ SiNx in Regrowth Process. *IEEE Electron Device Lett.* **2022**, *43*, 529–532. [CrossRef]

- 45. Ciarkowski, T.; Allen, N.; Carlson, E.; McCarthy, R.; Youtsey, C.; Wang, J.; Fay, P.; Xie, J.; Guido, L. Connection between Carbon Incorporation and Growth Rate for GaN Epitaxial Layers Prepared by OMVPE. *Materials* **2019**, *12*, 2455. [CrossRef] [PubMed]

- 46. Kapolnek, D.; Wu, X.H.; Heying, B.; Keller, S.; Keller, B.P.; Mishra, U.K.; DenBaars, S.P.; Speck, J.S. Structural evolution in epitaxial metalorganic chemical vapor deposition grown GaN films on sapphire. *Appl. Phys. Lett.* **1995**, *67*, 1541–1543. [CrossRef]

- 47. Dai, R.; Fu, S.; Xie, J.; Fan, G.; Hu, G.; Schrey, H.; Klingshirn, C. Photoluminescence of GaN epitaxial layers. *J. Phys. C Solid State Phys.* **1982**, *15*, 393. [CrossRef]

- Davydov, V.Y.; Averkiev, N.S.; Goncharuk, I.N.; Nelson, D.K.; Nikitina, I.P.; Polkovnikov, A.S.; Smirnov, A.N.; Jacobson, M.A.; Semchinova, O.K. Raman and photoluminescence studies of biaxial strain in GaN epitaxial layers grown on 6H–SiC. *J. Appl. Phys.* 1997, 82, 5097–5102. [CrossRef]

- 49. Epp, J. 4—X-ray diffraction (XRD) techniques for materials characterization. In *Materials Characterization Using Nondestructive Evaluation (NDE) Methods;* Hübschen, G., Altpeter, I., Tschuncky, R., Herrmann, H.-G., Eds.; Woodhead Publishing: Bremen, Germany, 2016; pp. 81–124. [CrossRef]

- Bunaciu, A.A.; Udristioiu, E.G.; Aboul-Enein, H.Y. X-ray diffraction: Instrumentation and applications. *Crit. Rev. Anal. Chem.* 2015, 45, 289–299. [CrossRef]

- 51. Sakai, A.; Sunakawa, H.; Usui, A. Transmission electron microscopy of defects in GaN films formed by epitaxial lateral overgrowth. *Appl. Phys. Lett.* **1998**, *73*, 481–483. [CrossRef]

- Griffiths, I.; Cherns, D.; Wang, X.; Wehman, H.H.; Mandl, M.; Strassburg, M.; Waag, A. Characterisation of 3D-GaN/InGaN core-shell nanostructures by transmission electron microscopy. *Phys. Status Solidi C* 2014, 11, 425–427. [CrossRef]

- 53. Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.I.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. *IEEE Trans. Electron Devices* **2017**, *64*, 779–795. [CrossRef]

- 54. Ishida, M.; Ueda, T.; Tanaka, T.; Ueda, D. GaN on Si Technologies for Power Switching Devices. *IEEE Trans. Electron Devices* **2013**, 60, 3053–3059. [CrossRef]

- 55. Chowdhury, N.; Lemettinen, J.; Xie, Q.; Zhang, Y.; Rajput, N.S.; Xiang, P.; Cheng, K.; Suihkonen, S.; Then, H.W.; Palacios, T. p-Channel GaN Transistor Based on p-GaN/AlGaN/GaN on Si. *IEEE Electron Device Lett.* **2019**, *40*, 1036–1039. [CrossRef]

- Singhal, S.; Roberts, J.C.; Rajagopal, P.; Li, T.; Hanson, A.W.; Therrien, R.; Johnson, J.W.; Kizilyalli, I.C.; Linthicum, K.J. GaN-ON-Si Failure Mechanisms and Reliability Improvements. In Proceedings of the 2006 IEEE International Reliability Physics Symposium Proceedings, San Jose, CA, USA, 26–30 March 2006; pp. 95–98.

- 57. Zhang, Y.; Sun, M.; Piedra, D.; Azize, M.; Zhang, X.; Fujishima, T.; Palacios, T. GaN-on-Si Vertical Schottky and p-n Diodes. *IEEE Electron Device Lett.* 2014, 35, 618–620. [CrossRef]

- Chung, J.W.; Ryu, K.; Lu, B.; Palacios, T. GaN-on-Si technology, a new approach for advanced devices in energy and communications. In Proceedings of the 2010 European Solid State Device Research Conference, Venice, Italy, 14–16 September 2010; pp. 52–56.

- 59. Pengelly, R.S.; Wood, S.M.; Milligan, J.W.; Sheppard, S.T.; Pribble, W.L. A Review of GaN on SiC High Electron-Mobility Power Transistors and MMICs. *IEEE Trans. Microw. Theory Technol.* **2012**, *60*, 1764–1783. [CrossRef]

- Ueda, T. Reliability issues in GaN and SiC power devices. In Proceedings of the 2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, USA, 1–5 June 2014; pp. 3D.4.1–3D.4.6.

- Jorudas, J.; Šimukovič, A.; Dub, M.; Sakowicz, M.; Prystawko, P.; Indrišiūnas, S.; Kovalevskij, V.; Rumyantsev, S.; Knap, W.; Kašalynas, I. AlGaN/GaN on SiC Devices without a GaN Buffer Layer: Electrical and Noise Characteristics. *Micromachines* 2020, 11, 1131. [CrossRef]

- Spaziani, L.; Lu, L. Silicon, GaN and SiC: There's room for all: An application space overview of device considerations. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 13–17 May 2018; pp. 8–11.

- 63. Rodríguez, M.; Zhang, Y.; Maksimović, D. High-Frequency PWM Buck Converters Using GaN-on-SiC HEMTs. *IEEE Trans. Power Electron.* 2014, 29, 2462–2473. [CrossRef]

- 64. Hove, M.V.; Boulay, S.; Bahl, S.R.; Stoffels, S.; Kang, X.; Wellekens, D.; Geens, K.; Delabie, A.; Decoutere, S. CMOS Process-Compatible High-Power Low-Leakage AlGaN/GaN MISHEMT on Silicon. *IEEE Electron Device Lett.* **2012**, *33*, 667–669. [CrossRef]

- Peralagu, U.; Alian, A.; Putcha, V.; Khaled, A.; Rodriguez, R.; Sibaja-Hernandez, A.; Chang, S.; Simoen, E.; Zhao, S.E.; Jaeger, B.D.; et al. CMOS-compatible GaN-based devices on 200mm-Si for RF applications: Integration and Performance. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 17.2.1–17.2.4.

- Jaeger, B.D.; Hove, M.V.; Wellekens, D.; Kang, X.; Liang, H.; Mannaert, G.; Geens, K.; Decoutere, S. Au-free CMOS-compatible AlGaN/GaN HEMT processing on 200 mm Si substrates. In Proceedings of the 2012 24th International Symposium on Power Semiconductor Devices and ICs, Bruges, Belgium, 3–7 June 2012; pp. 49–52.

- Yadav, S.; Cardinael, P.; Zhao, M.; Vondkar, K.; Peralagu, U.; Alian, A.; Khaled, A.; Makovejev, S.; Ekoga, E.; Lederer, D.; et al. CMOS compatible GaN-on-Si HEMT technology for RF applications: Analysis of substrate losses and non-linearities. In Proceedings of the 2021 International Conference on IC Design and Technology (ICICDT), Dresden, Germany, 15–17 September 2021; pp. 1–4.

- Man Ho, K.; Wong, K.Y.; Lin, Y.S.; Yao, F.W.; Tsai, M.W.; Chang, Y.C.; Chen, P.C.; Su, R.Y.; Wu, C.H.; Yu, J.L.; et al. CMOScompatible GaN-on-Si field-effect transistors for high voltage power applications. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 17.6.1–17.6.4.

- Wong, K.Y.R.; Kwan, M.H.; Yao, F.W.; Tsai, M.W.; Lin, Y.S.; Chang, Y.C.; Chen, P.C.; Su, R.Y.; Yu, J.L.; Yang, F.J.; et al. A next generation CMOS-compatible GaN-on-Si transistors for high efficiency energy systems. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 9.5.1–9.5.4.

- Yu, J.; Zhang, W.J.; Shorten, A.; Li, R.; Ng, W.T. A smart gate driver IC for GaN power transistors. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 13–17 May 2018; pp. 84–87.

- Antonov, A.A.; Karpovich, M.S.; Vasilyev, V.Y. Dual 4-A High-Speed Low-Side Gate Driver IC for GaN and Si MOSFETs and IGBTs. In Proceedings of the 2022 IEEE 23rd International Conference of Young Professionals in Electron Devices and Materials (EDM), Altai, Russia, 30 June–4 July 2022; pp. 378–382.

- 72. Perkins, S.; Arvanitopoulos, A.; Gyftakis, K.N.; Lophitis, N. A comprehensive comparison of the static performance of commercial GaN-on-Si devices. In Proceedings of the 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Santa Ana Pueblo, NM, USA, 30 October–1 November 2017; pp. 177–184.

- 73. Jones, E.A.; Wang, F.; Ozpineci, B. Application-based review of GaN HFETs. In Proceedings of the 2014 IEEE Workshop on Wide Bandgap Power Devices and Applications, Knoxville, TN, USA, 13–15 October 2014; pp. 24–29.

- 74. Moench, S.; Salcines, C.; Li, R.; Li, Y.; Kallfass, I. Substrate potential of high-voltage GaN-on-Si HEMTs and half-bridges: Static and dynamic four-terminal characterization and modeling. In Proceedings of the 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, USA, 9–12 July 2017; pp. 1–8.

- Perkins, S.; Arvanitopoulos, A.; Gyftakis, K.N.; Lophitis, N. On the Static Performance of Commercial GaN-on-Si Devices at Elevated Temperatures. In Proceedings of the 2018 1st Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Xi'an, China, 16–18 May 2018; pp. 174–178.

- 76. Yakimova, R.; Janzén, E. Current status and advances in the growth of SiC. Diam. Relat. Mater. 2000, 9, 432–438. [CrossRef]

- 77. Su, M.; Chen, C.; Rajan, S. Prospects for the application of GaN power devices in hybrid electric vehicle drive systems. *Senicond. Sci. Technol.* **2013**, *28*, 074012. [CrossRef]

- Liu, Z.; Xing, W.; Ng, G.I.; Fitzgerald, E.A. RF and Power GaN HEMTs on 200 mm-Diameter 725 μm-Thick p-Si Substrates. In Proceedings of the 2019 Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 100–102.

- 79. Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R.; et al. The 2018 GaN power electronics roadmap. *J. Phys. D Appl. Phys.* **2018**, *51*, 163001. [CrossRef]

- 80. Niranjan, S.; Muralidharan, R.; Sen, P.; Nath, D.N. Au-Free AlGaN/GaN HEMT on Flexible Kapton Substrate. *IEEE Trans. Electron Devices* **2022**, 69, 4212–4217. [CrossRef]

- Vohra, A.; Geens, K.; Zhao, M.; Syshchyk, O.; Hahn, H.; Fahle, D.; Bakeroot, B.; Wellekens, D.; Vanhove, B.; Langer, R.; et al. Epitaxial buffer structures grown on 200 mm engineering substrates for 1200 V E-mode HEMT application. *Appl. Phys. Lett.* 2022, 120, 261902. [CrossRef]

- 82. Ziegler, G.; Lanig, P.; Theis, D.; Weyrich, C. Single crystal growth of SiC substrate material for blue light emitting diodes. *IEEE Trans. Electron Devices* **1983**, *30*, 277–281. [CrossRef]

- 83. Kang, K.-H.; Eun, T.; Jun, M.-C.; Lee, B.-J. Governing factors for the formation of 4H or 6H-SiC polytype during SiC crystal growth: An atomistic computational approach. *J. Cryst. Growth* **2014**, *389*, 120–133. [CrossRef]

- 84. Su, J.; Chen, X.; Li, Y.; Pons, M.; Blanquet, E. A niching genetic algorithm applied to optimize a SiC-bulk crystal growth system. *J. Cryst. Growth* **2017**, *468*, 914–918. [CrossRef]

- 85. Narumi, T.; Kawanishi, S.; Yoshikawa, T.; Kusunoki, K.; Kamei, K.; Daikoku, H.; Sakamoto, H. Thermodynamic evaluation of the C–Cr–Si, C–Ti–Si, and C–Fe–Si systems for rapid solution growth of SiC. J. Cryst. Growth 2014, 408, 25–31. [CrossRef]

- 86. Powell, J.A. Silicon Carbide: Progress in Crystal Growth. MRS Online Proc. Libr. (OPL) 1987, 97, 159. [CrossRef]

- 87. Ghezzo, M.; Brown, D.M.; Downey, E.; Kretchmer, J.; Hennessy, W.; Polla, D.L.; Bakhru, H. Nitrogen-implanted SiC diodes using high-temperature implantation. *IEEE Electron Device Lett.* **1992**, *13*, 639–641. [CrossRef]

- 88. Hallén, A.; Linnarsson, M. Ion implantation technology for silicon carbide. Surf. Coat. Technol. 2016, 306, 190–193. [CrossRef]

- 89. Mehregany, M.; Zorman, C.A.; Rajan, N.; Chien Hung, W. Silicon carbide MEMS for harsh environments. *Proc. IEEE* **1998**, *86*, 1594–1609. [CrossRef]

- 90. Powell, A.R.; Rowland, L.B. SiC materials-progress, status, and potential roadblocks. Proc. IEEE 2002, 90, 942–955. [CrossRef]

- 91. Ellison, A.; Zhang, J.; Peterson, J.; Henry, A.; Wahab, Q.; Bergman, J.P.; Makarov, Y.N.; Vorob'ev, A.; Vehanen, A.; Janzén, E. High temperature CVD growth of SiC. *Mater. Sci. Eng. B* **1999**, *61*, 113–120. [CrossRef]

- 92. Chichignoud, G.; Ucar-Morais, M.; Pons, M.; Blanquet, E. Chlorinated silicon carbide CVD revisited for polycrystalline bulk growth. *Surf. Coat. Technol.* 2007, 201, 8888–8892. [CrossRef]

- 93. Malherbe, J.B. Diffusion of fission products and radiation damage in SiC. J. Phys. D Appl. Phys. 2013, 46, 473001. [CrossRef]

- 94. Gan, V.J.L.; Lo, I.M.C.; Ma, J.; Tse, K.T.; Cheng, J.C.P.; Chan, C.M. Simulation optimisation towards energy efficient green buildings: Current status and future trends. *J. Clean. Prod.* **2020**, 254, 120012. [CrossRef]

- Yan, B.; Luh, P.B.; Sun, B.; Song, C.; Dong, C.; Gan, Z.; Michel, L.D. Energy-efficient management of eco-communities. In Proceedings of the 2013 IEEE International Conference on Automation Science and Engineering (CASE), Madison, WI, USA, 17–20 August 2013; pp. 106–111.

- 96. Verma, A.; Chaudhary, P.; Tripathi, R.K.; Yadav, B.C. Flexible, environmentally-acceptable and long-durable-energy-efficient novel WS2–polyacrylamide MOFs for high-performance photodetectors. *Mater. Adv.* **2022**, *3*, 3994–4005. [CrossRef]

- 97. Yadlapalli, R.T.; Kotapati, A.; Kandipati, R.; Balusu, S.R.; Koritala, C.S. Advancements in energy efficientGaNpower devices and power modules for electric vehicle applications: A review. *Int. J. Energy Res.* **2021**, 45, 12638–12664. [CrossRef]

- He, S.; Chen, C.; Li, T.; Song, J.; Zhao, X.; Kuang, Y.; Liu, Y.; Pei, Y.; Hitz, E.; Kong, W.; et al. An Energy—Efficient, Wood—Derived Structural Material Enabled by Pore Structure Engineering towards Building Efficiency. *Small Methods* 2019, *4*, 1900747. [CrossRef]

Bairamov, B.H.; Gürdal, O.; Botchkarev, A.; Morkoç, H.; Irmer, G.; Monecke, J. Direct evidence of tensile strain in wurtzite

- structure n GaN layers grown on n Si(111) using AlN buffer layers. Phys. Rev. B 1999, 60, 16741–16746. [CrossRef]

Wang Z Th Fujikara N. Wang Z Th Fujikara N. Columnia The Yang O K. (Tolkara da Talamana New Yang China and China

- 100. Yamada-Takamura, Y.; Wang, Z.T.; Fujikawa, Y.; Sakurai, T.; Xue, Q.K.; Tolle, J.; Liu, P.L.; Chizmeshya, A.V.G.; Kouvetakis, J.; Tsong, I.S.T. Surface and Interface Studies of GaN Epitaxy on Si(111) via ZrB<sub>2</sub> Buffer Layers. *Phys. Rev. Lett.* 2005, 95, 266105. [CrossRef]

- 101. Tripathy, S.; Chua, S.J.; Chen, P.; Miao, Z.L. Micro-Raman investigation of strain in GaN and AlxGa1–xN/GaN heterostructures grown on Si(111). *J. Appl. Phys.* 2002, *92*, 3503–3510. [CrossRef]

- 102. El Hadi Khediri, A.; Benbakhti, B.; Gerbedoen, J.C.; Maher, H.; Jaouad, A.; Bourzgui, N.E.; Soltani, A. Dual role of 3C-SiC interlayer on DC and RF isolation of GaN/Si-based devices. *Appl. Phys. Lett.* **2022**, *121*, 122103. [CrossRef]

- 103. Soltani, A.; Cordier, Y.; Gerbedoen, J.C.; Joblot, S.; Okada, E.; Chmielowska, M.; Ramdani, M.R.; De Jaeger, J.C. Assessment of transistors based on GaN on silicon substrate in view of integration with silicon technology. *Semicond. Sci. Technol.* 2013, 28, 094003. [CrossRef]

- Gerbedoen, J.C.; Soltani, A.; Joblot, S.; Jaeger, J.C.D.; Gaquiere, C.; Cordier, Y.; Semond, F. AlGaN/GaN HEMTs on (001) Silicon Substrate With Power Density Performance of 2.9 W/mm at 10 GHz. *IEEE Trans. Electron Devices* 2010, 57, 1497–1503. [CrossRef]

- 105. Soltani, A.; Gerbedoen, J.C.; Cordier, Y.; Ducatteau, D.; Rousseau, M.; Chmielowska, M.; Ramdani, M.; Jaeger, J.C.D. Power Performance of AlGaN/GaN High-Electron-Mobility Transistors on (110) Silicon Substrate at 40 GHz. *IEEE Electron Device Lett.* 2013, 34, 490–492. [CrossRef]

- 106. Defrance, N.; Douvry, Y.; Hoel, V.; Gerbedoen, J.-C.; Soltani, A.; Rousseau, M.; Jaeger, J.C.D.; Langer, R.; Lahreche, H. Thermal resistance of AlGaN/GaN HEMTs on SopSiC composite substrate. In *Electronics Letters*; Institution of Engineering and Technology: London, UK, 2010; Volume 46, pp. 949–950.

- 107. Soltani, A.; BenMoussa, A.; Touati, S.; Hoël, V.; De Jaeger, J.C.; Laureyns, J.; Cordier, Y.; Marhic, C.; Djouadi, M.A.; Dua, C. Development and analysis of low resistance ohmic contact to n-AlGaN/GaN HEMT. *Diam. Relat. Mater.* 2007, 16, 262–266. [CrossRef]

- 108. Minko, A.; Hoel, V.; Morvan, E.; Grimbert, B.; Soltani, A.; Delos, E.; Ducatteau, D.; Gaquiere, C.; Theron, D.; Jaeger, J.C.D.; et al. AlGaN-GaN HEMTs on Si with power density performance of 1.9 W/mm at 10 GHz. *IEEE Electron Device Lett.* 2004, 25, 453–455. [CrossRef]

- 109. Ducatteau, D.; Minko, A.; Hoel, V.; Morvan, E.; Delos, E.; Grimbert, B.; Lahreche, H.; Bove, P.; Gaquiere, C.; Jaeger, J.C.D.; et al. Output power density of 5.1/mm at 18 GHz with an AlGaN/GaN HEMT on Si substrate. *IEEE Electron Device Lett.* 2006, 27, 7–9. [CrossRef]

- 110. Vladimir, O.; Cem, B.; Shari, F. Engineered Substrate Structure for Power and RF Applications. U.S. Patent US10297445B2, 21 May 2019.

- 111. Li, X.; Geens, K.; Guo, W.; You, S.; Zhao, M.; Fahle, D.; Odnoblyudov, V.; Groeseneken, G.; Decoutere, S. Demonstration of GaN Integrated Half-Bridge With On-Chip Drivers on 200-mm Engineered Substrates. *IEEE Electron Device Lett.* 2019, 40, 1499–1502. [CrossRef]

- 112. Tanaka, A.; Choi, W.; Chen, R.; Liu, R.; Mook, W.M.; Jungjohann, K.L.; Yu, P.K.L.; Dayeh, S.A. Structural and electrical characterization of thick GaN layers on Si, GaN, and engineered substrates. *J. Appl. Phys.* **2018**, 125, 082517. [CrossRef]

- 113. Li, X.; Amirifar, N.; Geens, K.; Zhao, M.; Guo, W.; Liang, H.; You, S.; Posthuma, N.; Jaeger, B.D.; Stoffels, S.; et al. GaN-on-SOI: Monolithically Integrated All-GaN ICs for Power Conversion. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 4.4.1–4.4.4.